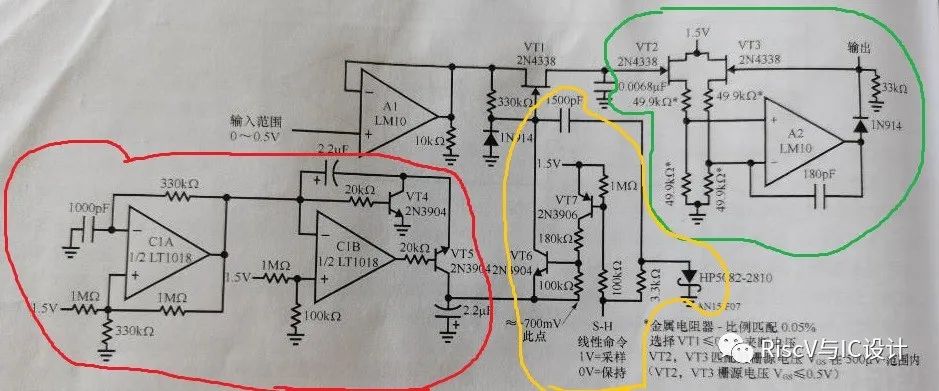

與ADC轉換器相伴出現的邏輯器件是采樣保持放大器。 對于1.5V工作的電路來說,采樣保持電路是最難設計的電路之一,主要是因為沒有可用的具有足夠低截止電壓的FET開關,這里介紹了兩個方法,第一種方法是通過去掉開關來解決相關問題,雖然其實現采樣保持的方法并非常規方法,但它不需要專門的部件,不需要微調,電路容易構建,具有大約4ms級采樣時間(穩定到0.1%)。

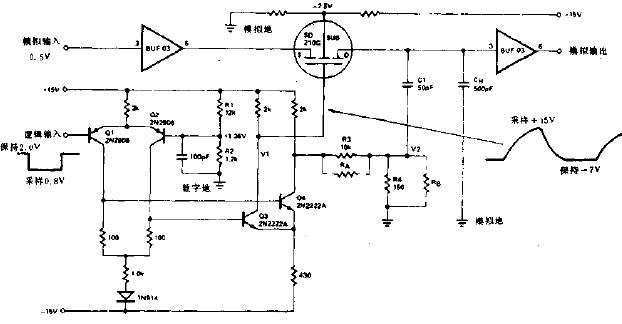

第二種是更加傳統的設計電路,需要專門進行選擇的匹配部件,更為復雜,但是其提供的125us( 0.1%)的采集時間,相比第一種的設計提高了30倍。我們將分兩次推文分別介紹這兩種設計,先介紹第一種設計:

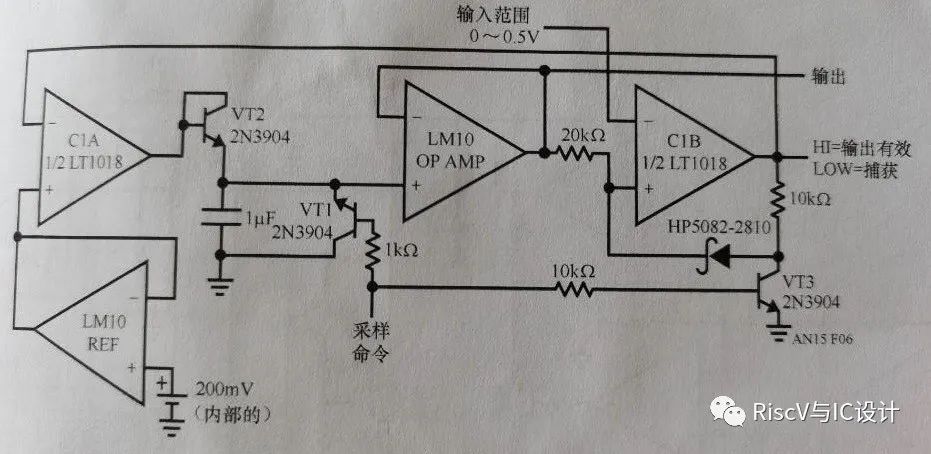

此電路利用積分與比較器構成采樣和保持功能,其中VT1是倒置三極管應用,保證采樣電容充分放電,C1B/C1A比較器構成反饋保持功能,特別是HP5082-2810一個小小肖特基二極管,構成了正反饋的鎖存器,以避免采樣保持電壓波動,因為仿真中發現LM10運放太老舊了,準備換成TI公司的最新超低壓運放,而此運放在multisim中沒有模型,需要自制元件模型,所以第一個視頻是介紹如何自制模型。后續推文將另外介紹orcad 的PSPICE A/D混合仿真時,其中的自制仿真模型與這里介紹的multisim自制仿真模型類似。

-

放大器

+關注

關注

143文章

13583瀏覽量

213368 -

電路分析

+關注

關注

62文章

518瀏覽量

98809 -

adc

+關注

關注

98文章

6495瀏覽量

544467 -

比較器

+關注

關注

14文章

1650瀏覽量

107185 -

FET

+關注

關注

3文章

632瀏覽量

62948 -

肖特基二極管

+關注

關注

5文章

927瀏覽量

34806 -

保持放大器

+關注

關注

0文章

7瀏覽量

8948 -

ADC轉換器

+關注

關注

1文章

28瀏覽量

8323

發布評論請先 登錄

相關推薦

不外接電阻的采樣保持放大器電路

每周經典電路分析:采樣保持放大器(1)

每周經典電路分析:采樣保持放大器(1)

評論