隨著信號速率-AMI模型在信號完整性仿真中應用越來越多,本文主要介紹了IBIS-AMI模型的基礎知識和建模方案。IBIS-AMI模型建模一般采用SystemVue或者ADS這兩個工具都能分別完成。

IBIS 模型

IBIS模型出現之前,系統仿真使用的模型主要是Spice模型,SPICE (Simulation Program with IntegratedCircuit Emphasis)是一種通用的電路模擬語言,其對應的網表文件可以作為用于描述器件內部實際電氣連接的器件模型。SPICE模型包含詳細的晶體管結構和具體的工藝技術,因此模型精度很高,但與此同時,由于其包含有過多有價值的信息,多數芯片廠商往往不會提供SPICE模型給客戶。另外,SPICE模型是電路級仿真,其仿真時間與電路復雜度直接相關,在芯片集成度越來越高、電路越來越復雜的今天,SPICE模型仿真往往計算量巨大、需要耗費大量時間,只適用于電路級的設計者使用。

為了解決這些問題, IBIS模型應運而生了

IBIS (I/O Buffer Information Specification) 是一個公開的且已經成為行業標準的數字電路輸入輸出建模規范。它是基于I/V、V/T曲線的用于描述芯片I/OBuffer行為級特性的模型,能夠反映芯片驅動和接收的電氣特性。芯片廠商很容易便可以在不透露知識產權的同時提供給客戶IBIS模型,以便在IBIS兼容仿真器(如ADS)中使用。并且與等效電路SPICE模型相比,IBIS的仿真速度要快的多。

為了建立統一的IBIS 模型,EDA廠商、IC供應商和最終用戶成立了一個IBIS格式制定委員會,以推出并不斷修訂IBIS模型規范。

IBIS 模型雖然強大,但是也不能解決數字電路仿真中出現的所有問題。高速串行總線在使用過程中經常會出現一類問題:由于鏈路較長或者由于頻率較高,而造成信號衰減過大,從而導致在接收端無法正確判別信號,所以這類SerDes架構的串行總線芯片都會有集成均衡或加重電路,尤其是接收端通常包含較復雜的均衡電路。而普通的IBIS模型無法對這樣復雜的均衡算法電路進行描述,

為了解決高速串行仿真在速率較高時帶來的問題,從IBIS 規范5.0開始,定義了新的IBIS AMI (Algorithmic Modeling Interface)模型,來實現IBIS模型無法描述的均衡算法功能。

AMI模型

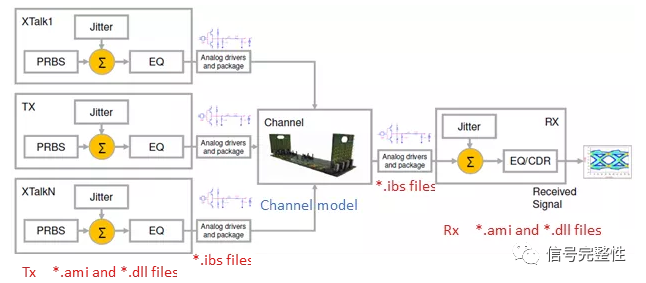

AMI(Algorithimic Model Interface)模型是IBIS協會制定的一種模型分析方法。在這一個分析方法當中,芯片廠商可以利用C++代碼建立模型,描述芯片內部功能電路的行為,然后將代碼編譯為動態鏈接庫(.dll),從而保護芯片內部設計的知識產權。對系統集成商而言,一旦從芯片廠商取得AMI模型,其開發工程師便可以結合自己設計的通道模型搭建成高速數字傳輸系統,通過軟件仿真來估算系統的眼圖(Eye Pattern)或者是誤碼率(BER),仿真時間只需數分鐘到數個小時便可完成。實踐證明使用IBIS AMI進行仿真的結果與實際測量通常具有相當高的吻合度,因而使用AMI模型進行系統仿真儼然已經變成整個產業的標準分析流程。

IBIS AMI 模型特點

與傳統模型相比,IBIS AMI模型具有以下優點,更符合芯片廠商和硬件設計者的需求:

·兼容性:不同半導體芯片廠商生成的模型可以在同一電路中仿真。

·可移植性:相同的模型可以用不同的仿真軟件來仿真分析。

· 高效率:10000000 bit的仿真可以在10 min或者更短的時間內完成。

·靈活性:模型支持統計和時域(bit-by-bit)分析模式。

·可優化:模型提供仿真控制參數(如抽頭系數等),用戶可以通過電路仿真器對各個參數進行掃描,優化,改善系統性能。

·知識產權保護: 芯片廠家只提供模型算法部分的加密動態鏈接庫文件,以避免逆向設計。

IBIS AMI 建模挑戰

IBIS AMI 模型由描述電氣特性的傳統的IBIS模型文件(*.ibs)、包含編譯后算法的動態鏈接庫文件(*.dll/*.so)以及參數描述文檔(*.ami)三個文件共同構成。

*.ibs 文件:

○聲明對應的AMI 參數文件和算法可執行文件*.dll,關鍵字為:

[Algorithmic Model]

[End Algorithmic Model]

○包含除均衡外的發射機特性:輸出電壓擺幅、輸出阻抗、轉換速度、輸出寄生參數等。

○包含除均衡外的接收機特性:輸入負載阻抗、寄生參數等。

*.ami 參數定義文件:

○[Reserved_Parameters]關鍵字中定義模型的處理流程,如:

Init_Returns_Impluse:是否有算法模型等效LTI沖激響應(若為TRUE,可用于統計模式)。

GetWave_Exists:若為TRUE,算法模型為 NLTV, 可通過AMI_GetWave 函數生成輸出信號。

使用Tx_Jitter、Rx_Clock_PDF加入抖動參數等。

○[Model_Specific] 關鍵字中把仿真器的參數傳遞給相應的可執行模塊。

*.dll/*.so 算法可執行文件:編譯后的算法文件(不可讀),是真正用于信號處理的文件。Windows系統中使用*.dll文件,Linux系統中使用*.so文件。

IBIS AMI模型的建模對芯片設計人員來說具有一定的挑戰:需要同時具備電路知識、高速信號傳輸知識及仿真能力,以及編程能力。產品往往覆蓋多種協議,如PCIe, USB, SAS, SATA, HDMI等等。并且隨著產品的更新換代,設計人員需要不斷地更新設計,同時保證每個模型的準確度,這也需要花費大量的時間和資源。

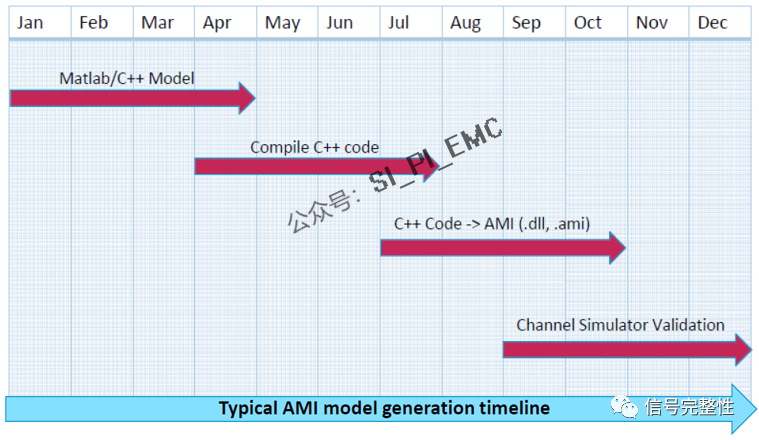

特別是對于沒有建模經驗的供應商而言,第一個IBIS AMI模型的建立往往需要花費半年到一年的時間才能得到第一代模型。而模型發布前還需要進行反復的驗證和測試,以確保模型精度。傳統的IBIS AMI建模周期如下圖所示:

傳統的IBIS AMI建模周期

對于系統工程師,及芯片廠商的客戶而言,相比于芯片的獲取,則可能需要等待較長的時間才能獲取到對應的精確的AMI模型。

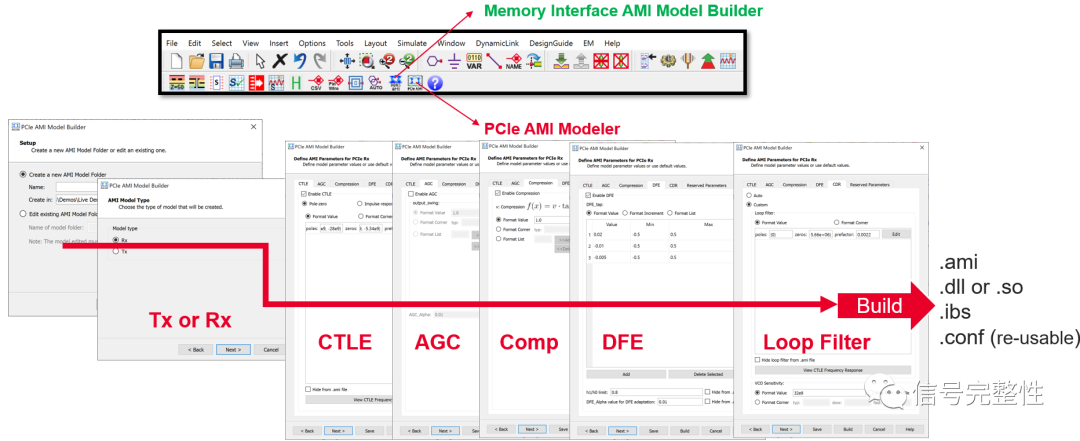

目前市場上能提供AMI模型建立以及測試工具的廠商很少,是德科技的 SystemVue以及 ADS是目前市場上被廣泛采用的工具。SytemVue提供了圖形化的界面以及豐富的模型庫,芯片廠商可以在模型庫里面挑選適當的元件搭建自己的發射/接收電路架構,隨后即可以自動編譯出AMI模型。ADS是業界高度認可的高速數字電路系統仿真平臺,同時也是支持AMI模型非常完整的工具。最新的ADS也能支持IBIS-AMI模型的建模。

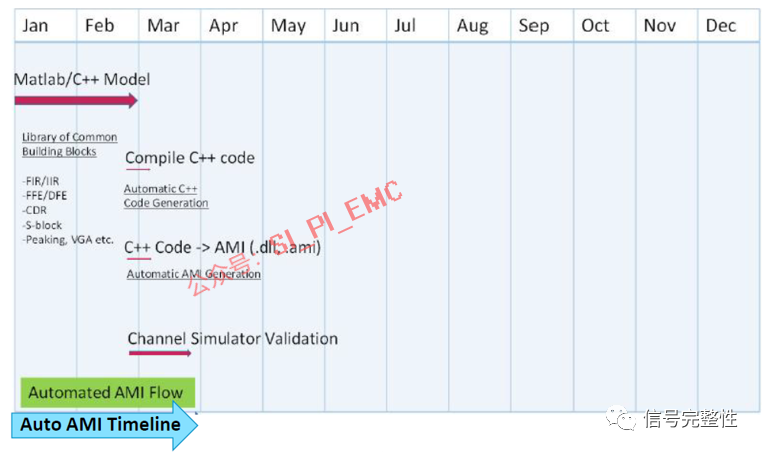

芯片廠商可以通過SystemVue以及ADS來加速AMI模型算法的開發以及驗證測試工作。系統集成商也可以方便的使用這兩種工具進行仿真以及測試,從而使得建模周期大大縮短:

使用PathWave SystemVue和PathWave ADS 縮短IBIS AMI建模周期

基于PathWave SystemVue的IBIS AMI 建模流程

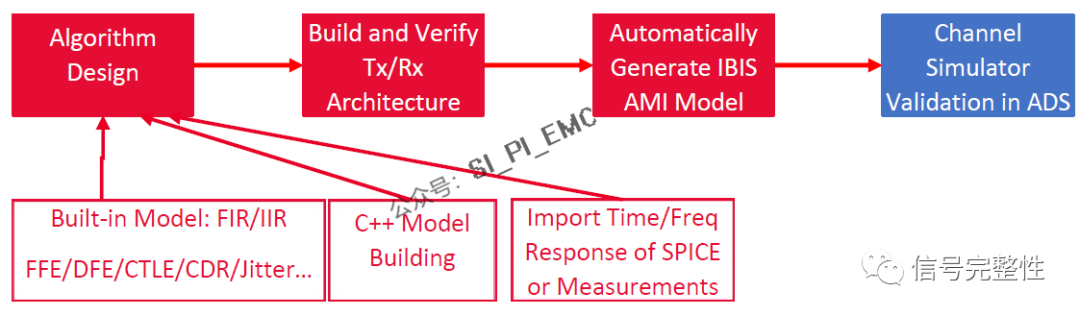

PathWave System Design, 即原SystemVue軟件,是專業的電子系統級仿真軟件,能夠為SerDes/DDR集成電路(IC)提供常用均衡算法及其他數字信號處理模塊,一旦算法設計并優化完成,PathWave System Design即可自動生成通用的IBIS AMI模型。用戶可將其導入通道仿真工具(如PathWave ADS)進行進一步的驗證,或提供給客戶,幫助他們設計包含有芯片特性的系統。

PathWave SystemVue提供一套自動化IBIS AMI建模流程,基于圖形界面設計。用戶可以使用軟件內建的常用算法模型,來快速對Tx/Rx中所需的Pre-shoot/De-emphasis(預加重/去加重)、CTLE(ContinuousTime Linear Equalizer,連續時間線性均衡)、Adaptive DFE(Adaptive Decision Feedback Equalizer,自適應判決反饋均衡)以及CDR(Clock Data Recovery時鐘數據恢復)等進行建模。同時,用戶也可以導入自定義的C/C++代碼或SPICE仿真或實際測量得到的電路時域/頻域響應等,來更精確地對芯片實際算法結構進行建模。經過仿真驗證后,用戶即可使用軟件提供的建模工具自動編譯生成所需的AMI文件,以便提供給通道仿真工具(如ADS)進行進一步的驗證。

IBIS AMI建模實例——SerDes模型庫及AMI 建模工具

AMI模型設計工具用于高速數字IC常用的信號處理算法設計,可以在不使用AMI模型的情況下對SerDes鏈路進行架構優化,同時也是用于建立IBIS AMI模型的必要模型庫。是高性能SerDes設計所必需的評估手段,幫助高速數字電路設計工程師利用物理層的信號處理手段以達到最大的互聯性能。其中也包括光纖通信中的 SerDes模型。

主要特性

·快速優化信號處理過程。同時支持算法設計、驗證及建模。

·在實施時無需經歷麻煩和耗時的迭代過程。將經過優化的算法模型作為一個可執行的規范,一次就成功地實施經過優化的體系結構。

· AMI 是基于產品和架構的模型。基于此工具能支持快速、精確、自動化地建立模型,避免了將敏感 IP 透露出去的危險。IBIS AMI 封裝程序可以確保標準一致性。

·無所有權加密。無需驗證和保有多個版本。AMI 模型設計工具提供了“一次編程,隨處可用”的功能。

·生成您需要發給客戶的所有格式的文件:*.ibs、*.ami、*.dll(Windows 可執行)、*.so(Linux的交叉編譯共享對象)。

·除了傳統的Tx/Rx模型外,還可對中間通道中繼器(Retimer/Redriver)和光纖通信鏈路進行建模。

·可與常用示波器眼圖分析軟件(FlexDCA)進行互操作,以便在同樣的眼圖分析算法下比對軟件仿真與硬件測試的結果。

·提供豐富的均衡算法,可取代大量編程工作。包括Blind/Adaptive FFE(預加重/去加重), CTLE線性時間均衡, CDR時鐘數據恢復 (可調整其中PLL, VCO各項參數),Blind/Adaptive DFE判決反饋均衡等復雜算法,也支持導入時域/頻域響應、自定義C++算法。可基于算法模型靈活設計所需功能,如非線性放大器等。

·支持添加抖動參數或抖動模型。

·支持靈活的畫圖方式,可對任意節點處的結果進行時域/頻域畫圖,也可對數據進行后處理。

·支持導入通道S參數,通道沖激響應/階躍響應等以用于鏈路仿真驗證。

·對于DDR5,提供獨家的方式支持DQ和DQS輸入。

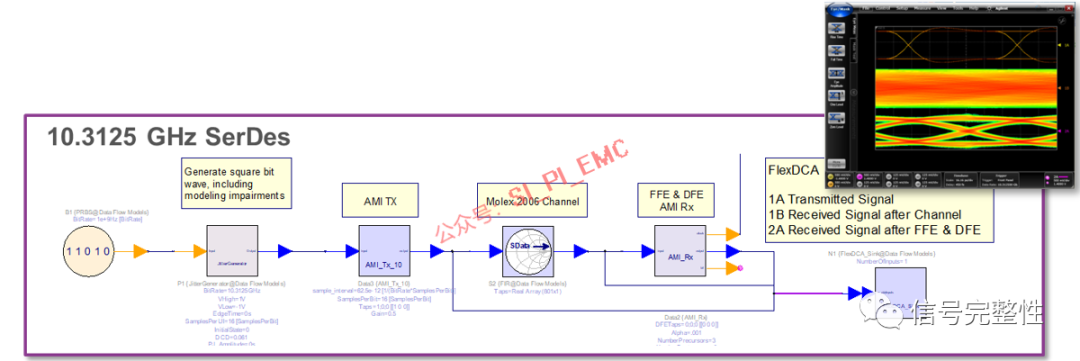

10.3125GHz SerDes 鏈路及模型示例:

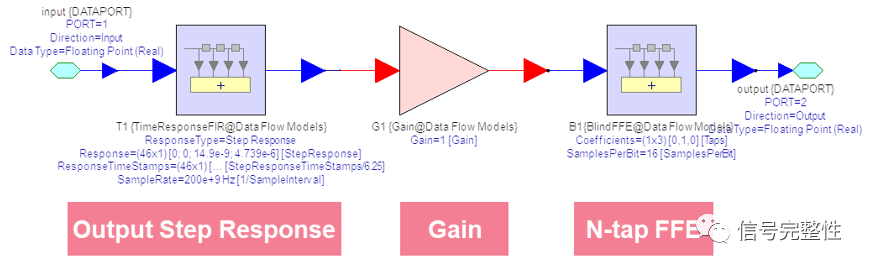

發射機模型架構示例:

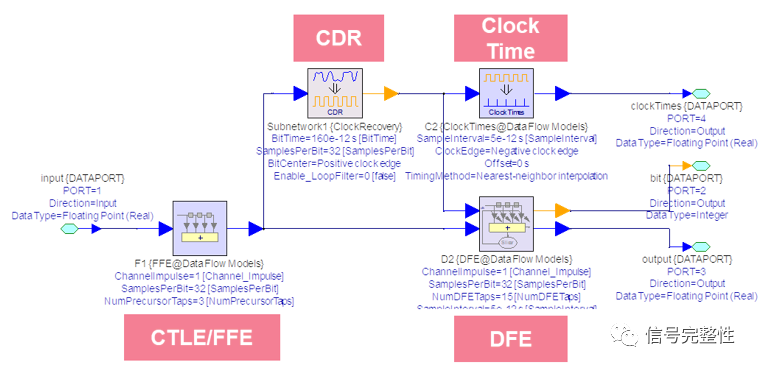

接收機模型架構示例:

DDR5 IBIS-AMI建模

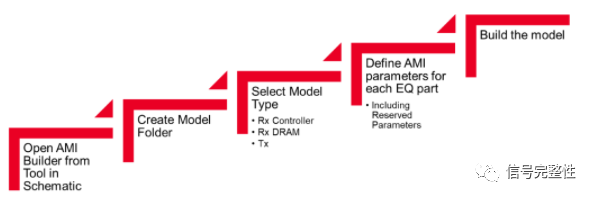

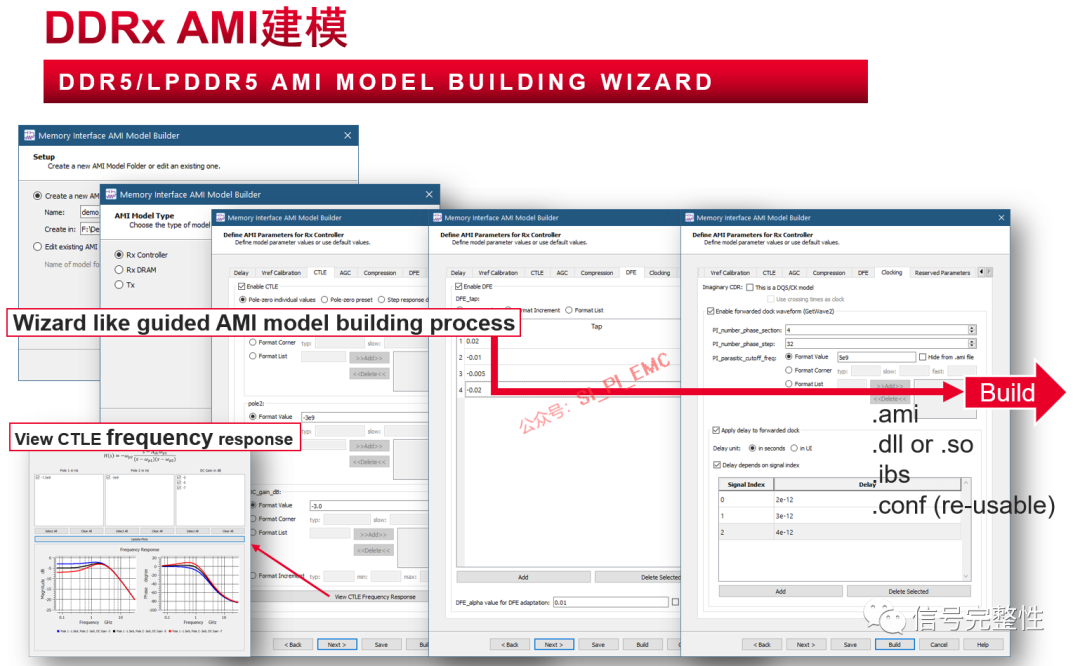

相較于串行總線,傳輸鏈路較短且損耗較低的DDR技術以往似乎一直沒有用到均衡,但隨著DDR5速率的提高(3200MTs ~ 8400MTs),愈發嚴重的碼間干擾(ISI)等問題使得眼圖難以張開,因此DFE等有效降低ISI的均衡算法也將應用于DDR5產品中。因此IBIS AMI 模型也將用于DDR5的仿真中。在ADS中能快速的建立DDR5的IBIS-AMI模型。其基本的建模流程如下:

DDR5 AMI 建模向導如下圖所示:

以Rx DRAM為例,包含如下功能選項(均參數可控),其中對時鐘的處理與SystemVue所提供的方法一致,即可以DQS作為時鐘觸發,若不以DQS作為時鐘,也可選擇與SerDes類似的方法,使用內部CDR恢復時鐘數據:

·Delay :(on signal index)為不同的信號線設置不同的delay參數。

·Vref Calibration:用于校準DC Offset,使之符合芯片中實際的DC Offset值。

·CTLE連續時間線性均衡

o Pole-zero 以零極點作為輸入設置(也可設置多組參數供使用者選擇)。

o Step/impulse response 輸入仿真或測量得到的時域響應。

·AGC:output swing 實現信號可控增益。

·Compression:Non-linearity 模擬芯片中的電路非線性行為。

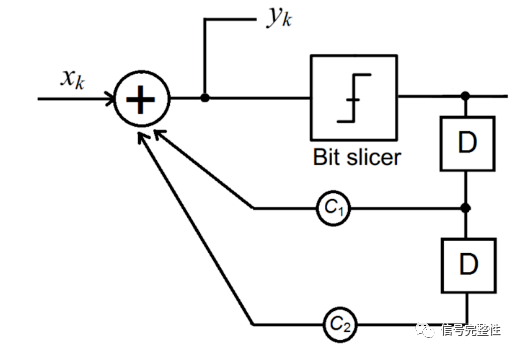

·DFE (adaptive)自適應判決反饋均衡

oInitial taps

oDFE_alphafor adaptation

·Clocking

oUse CDR if DQS/CK

o If not DQS/CK, support DQS as forwarded clock (當進行Controller建模時,增加Phase Interpolation 相位插值功能,以找到最佳時鐘相位。)

oSupport delay

·Reserved Parameters

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1033瀏覽量

84857 -

信號完整性

+關注

關注

68文章

1431瀏覽量

96363 -

SPICE

+關注

關注

6文章

190瀏覽量

43333 -

IBIS

+關注

關注

1文章

55瀏覽量

20133 -

AMI

+關注

關注

0文章

49瀏覽量

21993

原文標題:高速串行總線的IBIS-AMI建模詳解

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于HyperLynx VX.2.4的IBIS-AMI仿真測試臺構建方案

視頻: Artix-7 FPGA:如何在大批量應用中使用高速SerDes

申請TI Keystone DSP PCIe SerDes IBIS-AMI Models。

高速互連IBIS仿真模型概述

WEBENCH接口設計工具助力IBIS-AMI通道仿真

如何對系統進行最佳建模

IBIS建模對電路板原型設計的重要性

Agilent推出ADS 2010支持IBIS-AMI 模型

有關IBIS 6.1的知識信息簡介

TI Keystone DSP Hyperlink SerDes IBIS-AMI型號

評論