前言:

開關電源中采樣電路的設計是一個重點也是難點

而采樣電路更多的設計在于濾波器設計。

一般有兩種形式,一種是 有源濾波器(抗混疊濾波器)+RC(用于給ADC內(nèi)部保持電路提供電荷緩沖) 另一種是 單RC濾波器;

這部分內(nèi)容理解起來來比較難,一方面是比較抽象,另一方面包含的知識點非常多, 講解起來也很有難度。但也不用過于擔心,實際電路設計中大多是通過調(diào)試確定參數(shù)。所以這里只需要對結(jié)論有個全面的把握,在后續(xù)的章節(jié)會逐一分解其中涉及到的知識點。

一、ADC內(nèi)部電路

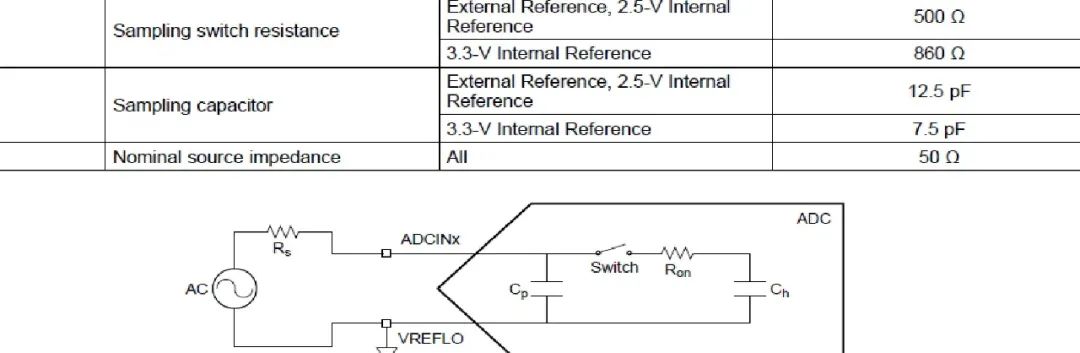

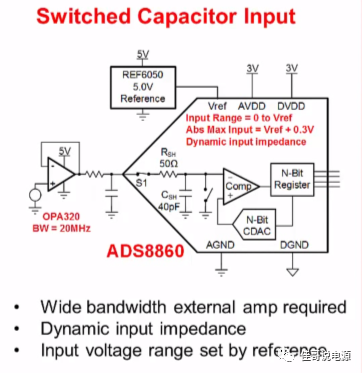

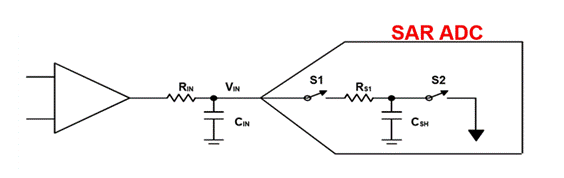

上圖是TMS320F28004X內(nèi)部ADC采樣保持電路,其中:

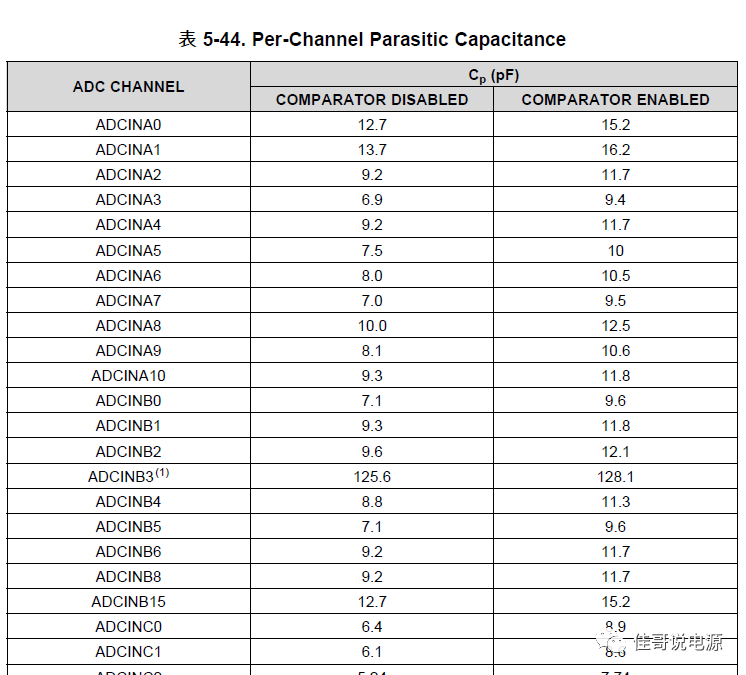

Cp: 寄生電容 Ron、Ch:采樣保持器

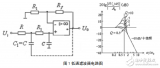

更準確的描述應該如下圖

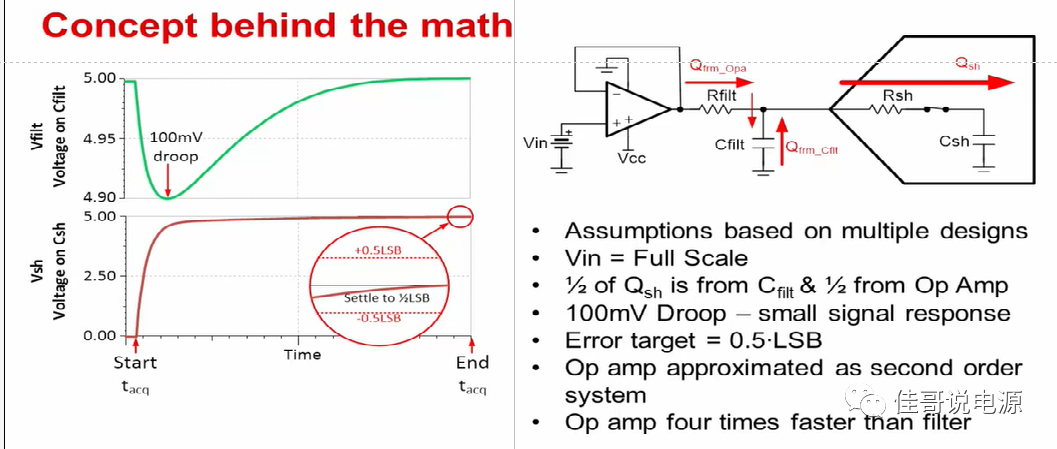

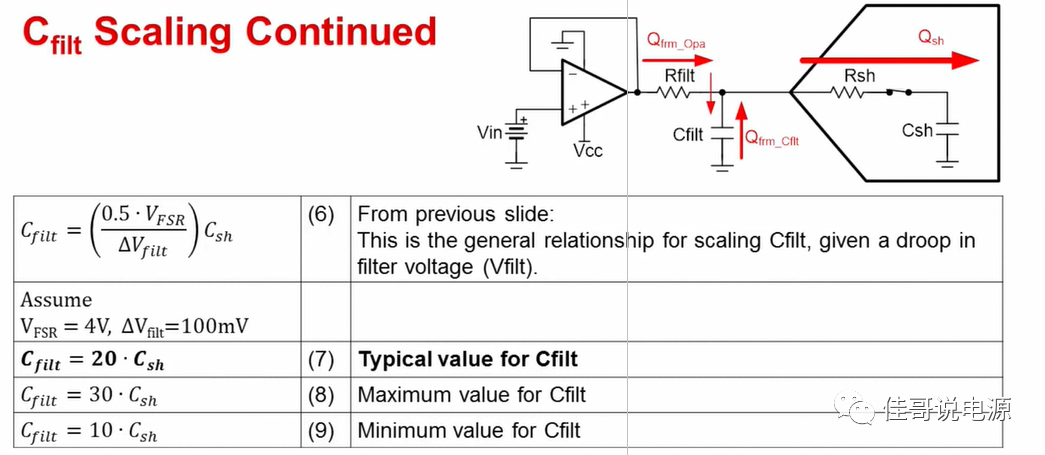

二、抗混疊濾波器

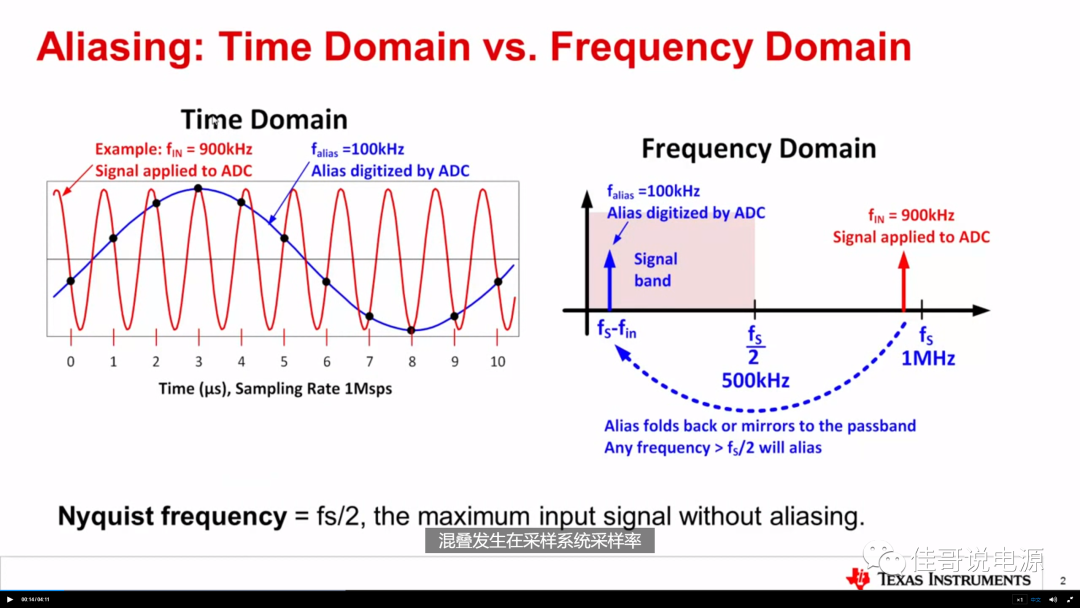

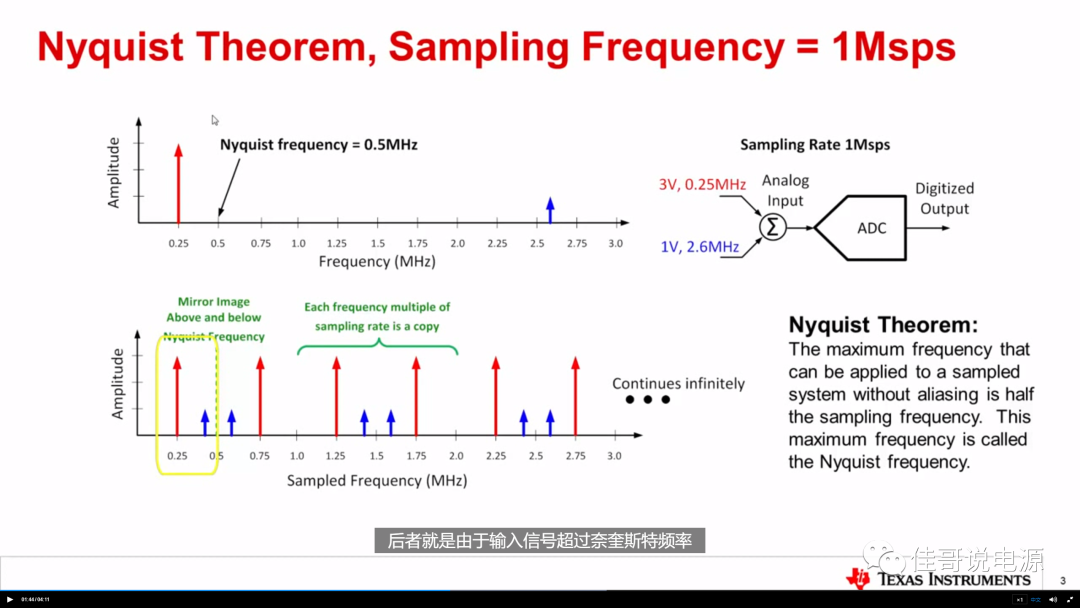

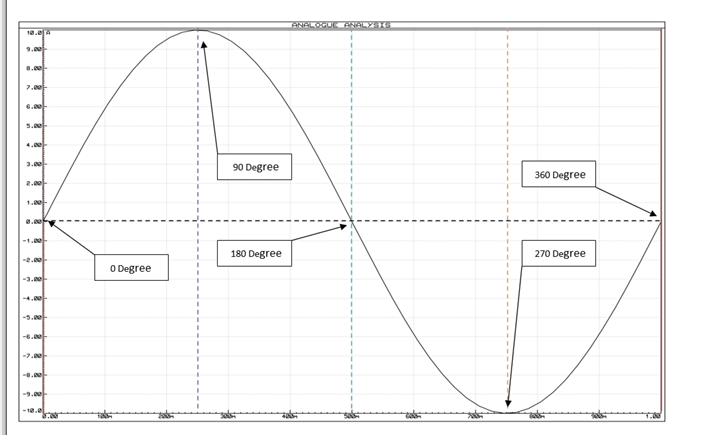

混疊是一種誤差我們希望將這種誤差降到最低 通常來說 混疊發(fā)生在采樣系統(tǒng)采樣率 不夠快的情況下經(jīng)常看到車輪轉(zhuǎn)得很快但實際我們眼睛發(fā)現(xiàn)轉(zhuǎn)得很慢 甚至反轉(zhuǎn)

實際上就是眼睛的采樣率不夠高 導致的混疊信號 可以從時域和頻域兩個維度來探討 ADC 的混疊現(xiàn)象 左圖是時域的混疊 輸入信號是 900kHz 采樣率是 1M 所以每一個黑點代表一個采樣點 將這些點集中起來 就是一個100kHz的信號 這個信號叫做混疊信號 實際上任何超過采樣率一半的輸入信號 都會產(chǎn)生混疊信號 這個頻率限制叫做奈奎斯特頻率 超過奈奎斯特頻率的信號都會產(chǎn)生混疊。這些混疊信號(或者說噪聲)會干擾真實信號,所以需要抗混疊濾波器將其濾除。

2.1、開關電源采樣抗混疊濾波器選型設計

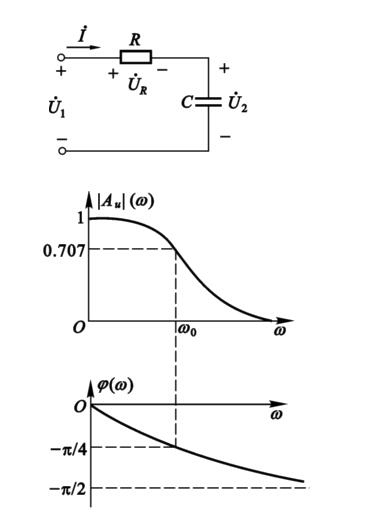

與一般的儀表或監(jiān)控等只需要考慮數(shù)據(jù)精度和抗干擾性(不考慮時延或相移,可以用高階有源濾波器獲得高Q值)。開關電源是一個典型的負反饋自動控制系統(tǒng),對可靠性和動態(tài)響應有非常高的要求,用于反饋的電流或電壓采樣信號要求盡量跟蹤原信號,所以要求ADC采樣濾波前后盡可能小的相位差,以獲得更高的環(huán)路帶寬。所以在電源里面采樣一般用到的是 一階濾波器 ,最典型的就是RC濾波器。

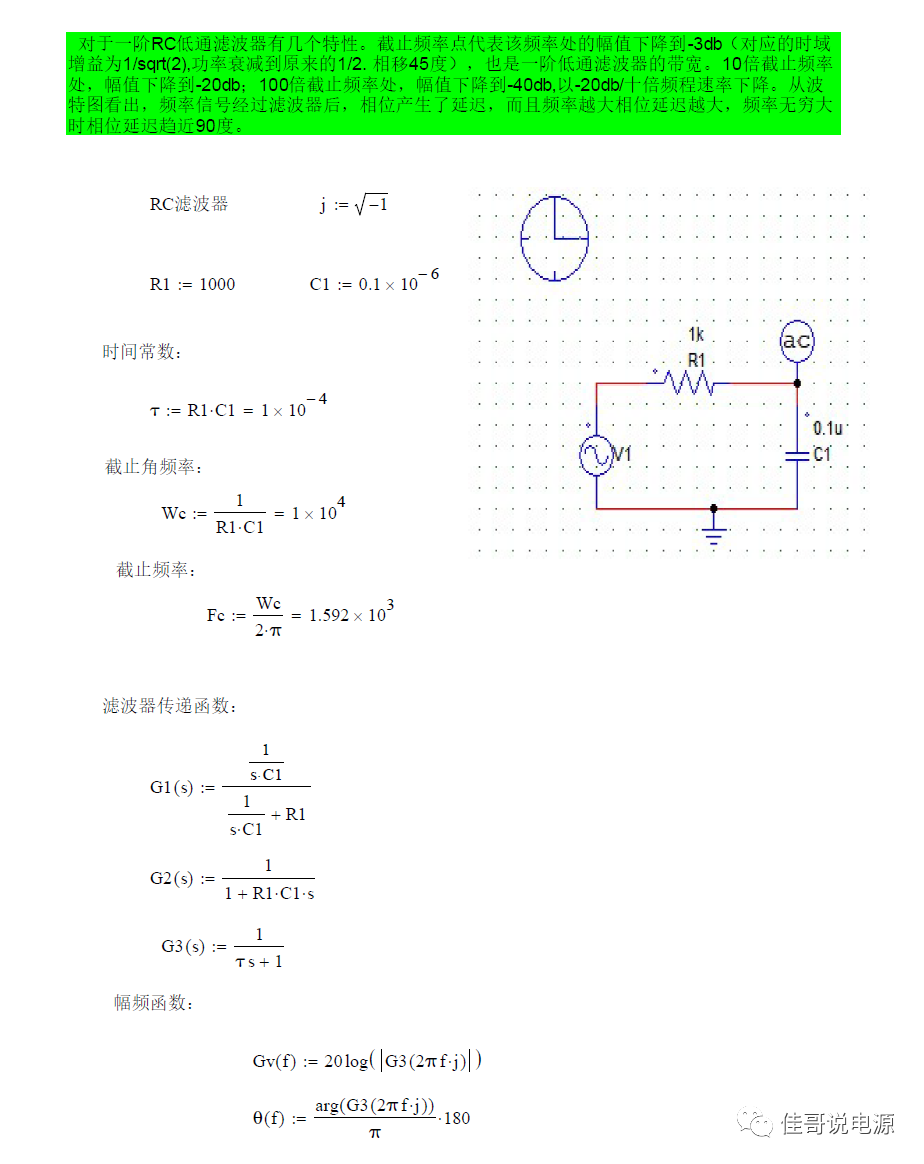

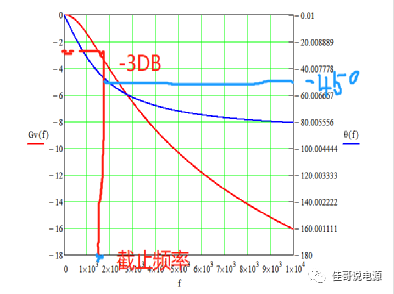

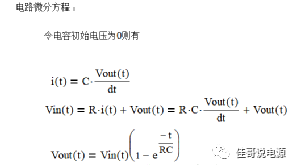

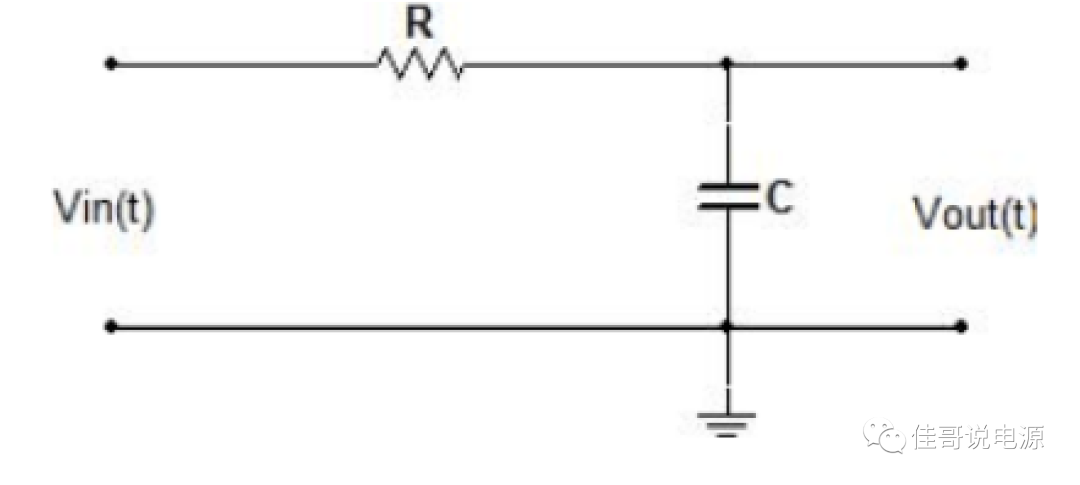

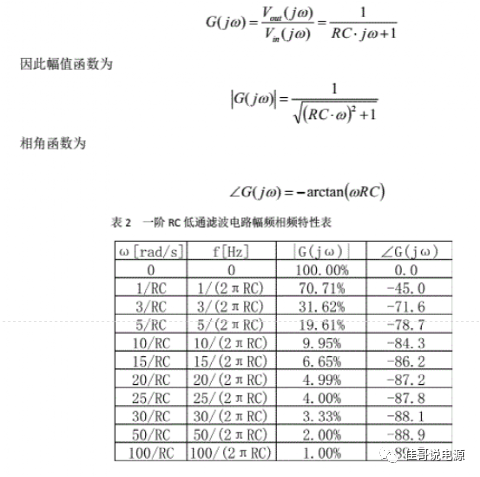

先回顧一下RC濾波器的特征:

為簡化分析:假定信號為周期性方波(對于RC濾器來講可以理解為階躍激勵信號),對于數(shù)字電源,一般是PWM周期性觸發(fā)ADC,為了滿足動態(tài)響應及精度,要求RC濾波器響應在每個周期開通Ton的前25%上升到待測信號95%。濾波設計主要考慮以下三點

1、 盡可能保證濾波后波形不失真

2、 盡量寬的帶寬保證盡量小的相移 ;

3、盡可能衰減干擾信號

時域上的考慮:

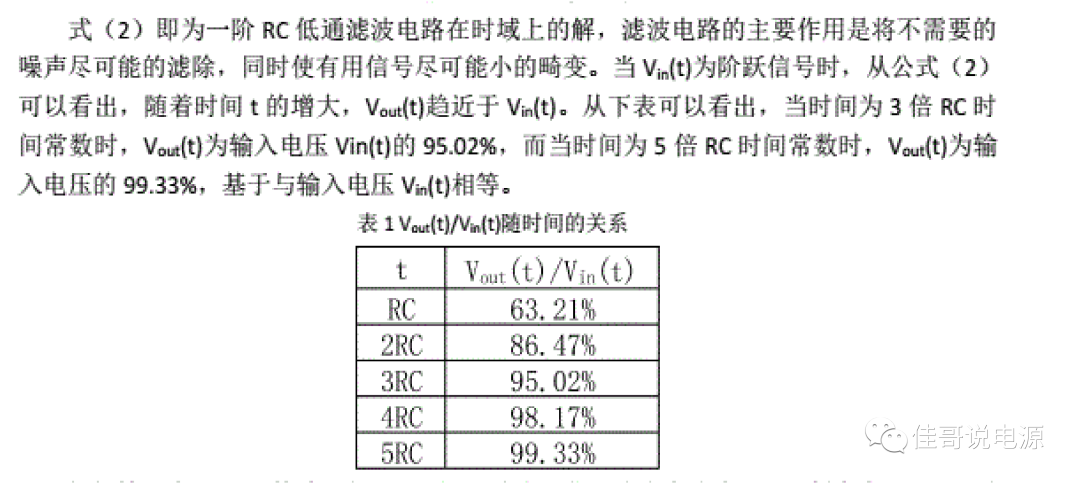

從上表可知,信號加在RC濾波器時間為1倍時間常數(shù)時,上升到信號的63.21%,3倍時間常數(shù)時,上升到原信號的95.02%。

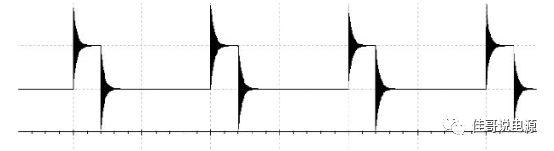

假設開關電源的開關頻率為100KHZ,則ADC采樣頻率也為100KHZ,波形如下,該信號最小占空比為20%,頻率為100Khz(周期10us),同時在上升沿和下降沿疊加了高頻振蕩干擾噪聲。

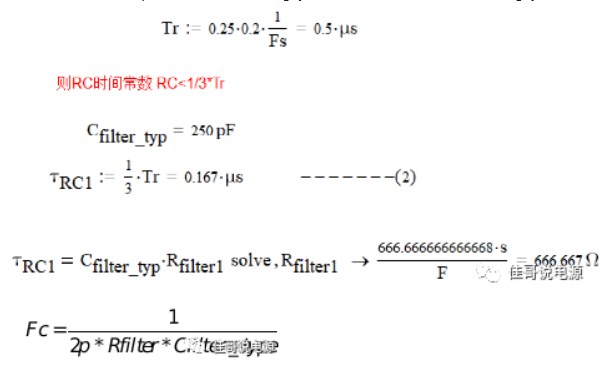

為了濾除干擾信號,并使波形盡可能小的畸變。則一階RC低通濾波電路的時間常數(shù)不應過大。現(xiàn)在要求經(jīng)過濾波后的信號從低電平上升到95%高電平的時間小于整個高電平時間的25%,即

Tr≤25%*20%*10us = 0.5us

因此 RC時間常數(shù)應小于Tr的1/3即

RC≤Tr/3=0.17us

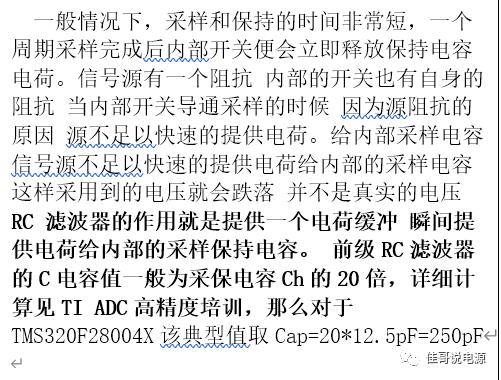

由于在采樣保持電容要求RC濾波電容典型要求為20*Cap_ch =250pF,

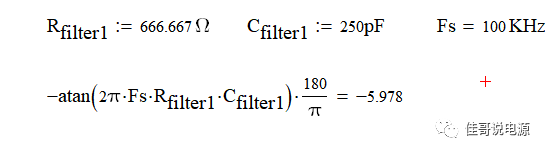

求得RC濾波電阻為Rfilter<< span="">666.667ohm,這僅是從時域角度考慮得到的阻值,以下再從頻率濾波和角度考慮

兼顧濾波效果和動態(tài)性能一般濾波器截止頻率Fc選取經(jīng)驗值為開關頻率Fs的5-10倍

取6

=600Khz

=600Khz

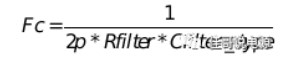

計算該濾波器的截止頻率

= 954.9Khz

954.9Khz > 600Khz

對比4.5Mhz干擾信號濾波前后效果,滿足要求

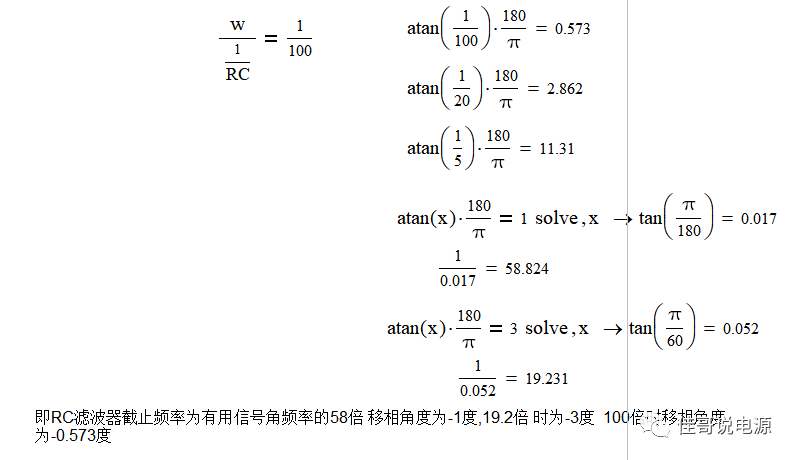

計算信號濾波前后相移

本例中:

即信號經(jīng)過RC濾波器后的相移為-5.978度。

-

濾波器

+關注

關注

161文章

7795瀏覽量

177996 -

運算放大器

+關注

關注

215文章

4929瀏覽量

172839 -

adc

+關注

關注

98文章

6495瀏覽量

544467 -

寄生電容

+關注

關注

1文章

292瀏覽量

19225 -

有源濾波器

+關注

關注

5文章

247瀏覽量

30918 -

RC濾波器

+關注

關注

0文章

75瀏覽量

16657 -

ADC采樣

+關注

關注

0文章

134瀏覽量

12840

發(fā)布評論請先 登錄

相關推薦

如何設計RC濾波器及運算放大器的選擇

精密SAR模數(shù)轉(zhuǎn)換器的前端放大器和RC濾波器設計

運算放大器放大信號供adc采集,運放前端需要怎么處理?需要額外的濾波降噪電路嗎?

通用運算放大器(Op-Amp)應用及分析

RC有源濾波器的設計

使用運算放大器的RC相移振蕩器

精密SAR模數(shù)轉(zhuǎn)換器的前端放大器和RC濾波器的設計

ADC前端運算放大器及RC濾波器設計案例

ADC前端運算放大器及RC濾波器設計案例

評論