導(dǎo)語(yǔ)

在更小、更輕、更薄的消費(fèi)產(chǎn)品趨勢(shì)的推動(dòng)下,越來(lái)越小的封裝類型已經(jīng)開(kāi)發(fā)出來(lái)。事實(shí)上,封裝已經(jīng)成為在新設(shè)計(jì)中使用或放棄設(shè)備的關(guān)鍵決定因素。本文首先定義了“倒裝芯片”和“芯片級(jí)封裝”這兩個(gè)術(shù)語(yǔ),并闡述了晶圓級(jí)封裝(WLP)技術(shù)的發(fā)展。接下來(lái)討論了使用晶圓級(jí)封裝器件的實(shí)際方面。討論的主題包括:確定給定器件的倒裝芯片/UCSP封裝的可用性;通過(guò)其標(biāo)記識(shí)別倒裝芯片/UCSP;圓片級(jí)封裝件的可靠性;尋找適用的可靠性信息。

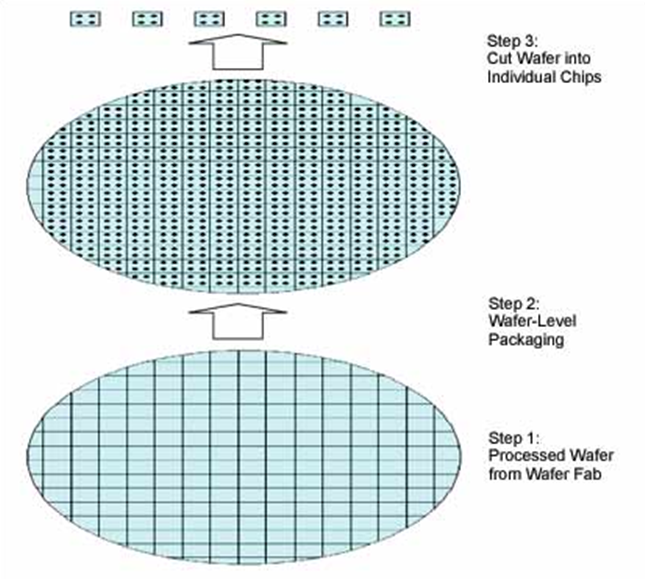

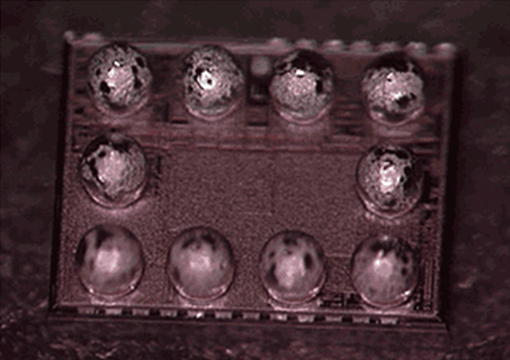

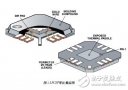

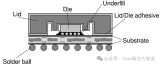

半導(dǎo)體技術(shù)的進(jìn)步創(chuàng)造了具有晶體管數(shù)量和功能的芯片,這在幾年前是不可想象的。如果沒(méi)有IC封裝同樣令人興奮的發(fā)展,我們今天所知道的便攜式電子產(chǎn)品是不可能實(shí)現(xiàn)的。在更小、更輕、更薄的消費(fèi)產(chǎn)品趨勢(shì)的推動(dòng)下,更小的封裝類型已經(jīng)被開(kāi)發(fā)出來(lái)。最小的封裝將永遠(yuǎn)是芯片本身的大小。圖1說(shuō)明了集成電路從晶圓到單個(gè)芯片的步驟。圖2顯示了一個(gè)實(shí)際的芯片級(jí)封裝(CSP)。

芯片尺寸封裝的概念在20世紀(jì)90年代發(fā)展起來(lái)。在1998年定義的CSP類別中,晶圓級(jí)CSP成為各種應(yīng)用的經(jīng)濟(jì)選擇,從低引腳數(shù)器件到ASIC和微處理器。CSP器件的制造過(guò)程稱為晶圓級(jí)封裝(WLP)。WLP的主要優(yōu)點(diǎn)是所有封裝制造和測(cè)試都是在晶圓上完成的。WLP的成本隨著晶圓尺寸的增加和芯片的縮小而下降。

圖1 晶圓級(jí)封裝(簡(jiǎn)化)最終將單個(gè)芯片與加工過(guò)的晶圓分離

圖2 一個(gè)12個(gè)凸起的芯片級(jí)封裝,其中2個(gè)凸起位置未填充

#1命名的由來(lái)

Nomenclature

業(yè)界對(duì)WLP的命名仍然存在困惑。CSP的晶圓級(jí)方法是獨(dú)特的,因?yàn)榉庋b內(nèi)部沒(méi)有鍵合技術(shù)。進(jìn)一步的困惑存在于如何稱呼封裝芯片。常用的描述性名稱有:Flip Chip、CSP、芯片級(jí)封裝、WLCSP、WL-CSP、Micro SMD、UCSP、凸模和Micro CSP。

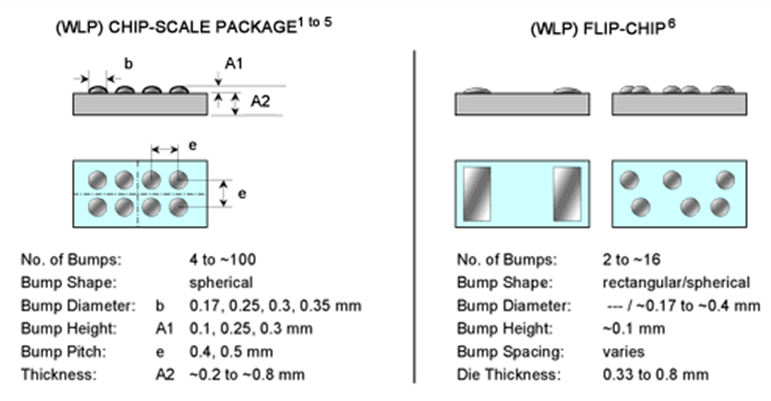

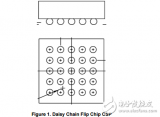

“倒裝芯片”和“芯片級(jí)封裝”最初是所有類型的晶圓級(jí)封裝芯片的同義詞。隨著時(shí)間的推移,這二者之間的區(qū)別越來(lái)越明顯。“倒裝芯片”描述的是具有任何形狀的凸點(diǎn)的晶圓級(jí)封裝芯片,可以位于任何位置(與邊緣有間隙)。而“芯片級(jí)封裝”描述的是晶圓級(jí)封裝芯片,其球形凸起位于具有預(yù)定義間距的網(wǎng)格上,圖3說(shuō)明了這些差異。

圖3 顯示芯片級(jí)封裝和倒裝芯片封裝之間的典型尺寸和差異

#2晶圓級(jí)封裝(WLP)技術(shù)

Wafer-Level Packaging (WLP) Technology

提供WLP零件的供應(yīng)商要么有自己的WLP工廠,要么外包封裝過(guò)程。因此,制造過(guò)程各不相同,用戶必須滿足的要求也各不相同,以確保最終產(chǎn)品的可靠性。

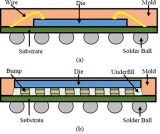

連接芯片到電路/配線板上的走線的凸起最初是由錫和鉛的共晶合金(Sn63Pb37)制成的。減少電子產(chǎn)品中有害物質(zhì)含量(RoHS)的舉措迫使半導(dǎo)體行業(yè)采用替代品,例如無(wú)鉛凸起(Sn96.5Ag3Cu0.5)或高鉛凸起(Pb95Sn5)。每種合金都有自己的熔點(diǎn),因此,在組件組裝回流過(guò)程中需要特定的溫度曲線(在特定溫度下的持續(xù)時(shí)間)。

集成電路的設(shè)計(jì)是為了提供所需的所有電路功能,并適合一組特定的封裝。芯片上的鍵合墊通過(guò)導(dǎo)線鍵合連接到傳統(tǒng)封裝的引腳上。傳統(tǒng)封裝的設(shè)計(jì)規(guī)則要求鍵合墊位于芯片的周長(zhǎng)。為了避免同一芯片的兩種設(shè)計(jì)(一種用于傳統(tǒng)封裝,另一種用于CSP),通常需要一個(gè)再分配層來(lái)連接凸起和鍵合墊。

#3設(shè)備標(biāo)識(shí)

Device Identification

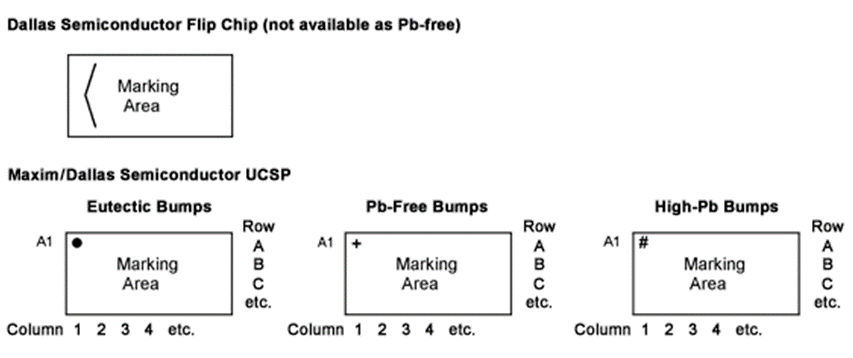

大多數(shù)倒裝芯片和UCSP沒(méi)有空間用于塑料封裝常見(jiàn)的傳統(tǒng)標(biāo)記。最小的UCSP(4個(gè)凸起)有足夠的空間來(lái)放置方向標(biāo)記和分布在兩行的6個(gè)字符的代碼。方向標(biāo)記還指示封裝是“標(biāo)準(zhǔn)”(共晶凸起)、高鉛(#)還是無(wú)鉛(+),參見(jiàn)圖4。

圖4 倒裝芯片和UCSP標(biāo)記模板

一旦制造完成,TSV通常會(huì)留下輕微的錐度,其中結(jié)構(gòu)底部的通孔更薄。較薄的區(qū)域由于其截面積較小,因此電流密度較大,因此電遷移更有可能首先發(fā)生在那里。結(jié)果會(huì)形成空洞,最終導(dǎo)致開(kāi)路。一旦空洞開(kāi)始形成,空洞也會(huì)成為應(yīng)力集中的區(qū)域,并可能發(fā)生機(jī)械斷裂。

#4晶圓級(jí)封裝部件的可靠性

Reliability of Wafer-Level Packaged Parts

晶圓級(jí)封裝(倒裝芯片和UCSP)代表了一種獨(dú)特的封裝形式,通過(guò)傳統(tǒng)的機(jī)械可靠性測(cè)試,其性能可能與封裝產(chǎn)品不一樣。封裝的可靠性與用戶的組裝方法、電路板材料和使用環(huán)境密切相關(guān)。在考慮使用WLP零件時(shí),應(yīng)仔細(xì)審查這些問(wèn)題。通過(guò)工作壽命測(cè)試和防潮性能保持不變,因?yàn)樗饕?a target="_blank">晶圓制造工藝決定。

機(jī)械應(yīng)力性能是WLP更關(guān)注的問(wèn)題。倒裝芯片和UCSP通過(guò)直接焊接接觸連接到用戶的PC板上,因此放棄了封裝產(chǎn)品引線框架的固有應(yīng)力緩解。因此,必須考慮焊點(diǎn)接觸完整性。

#5結(jié)論

Conclusion

如今,倒裝芯片和CSP仍然是一種不斷發(fā)展的新技術(shù)。正在進(jìn)行的改進(jìn)將應(yīng)用背面層壓涂層(BSL),保護(hù)模具的非活動(dòng)面免受光和機(jī)械沖擊,并提高在明光場(chǎng)照明下激光打標(biāo)的可讀性。隨著B(niǎo)SL,應(yīng)該期望減少模具厚度,以保持整體組裝高度不變。此外,重要的是要知道凹凸模WLP的具體合金成分,特別是如果一個(gè)設(shè)備沒(méi)有廣告和標(biāo)記為無(wú)鉛。一些具有高鉛凸起的器件(Pb95Sn5)已經(jīng)用無(wú)鉛電路板組裝回流工藝進(jìn)行了測(cè)試,發(fā)現(xiàn)其兼容性沒(méi)有顯著影響其可靠性。帶有共晶SnPb凸起的器件需要類似的共晶SnPb焊膏,與無(wú)鉛的組裝環(huán)境并不兼容。 接下來(lái),給各位推薦一個(gè)大型行業(yè)技術(shù)交流論壇。

8月17日第103屆CEIA電子智造高峰論壇即將在南京隆重舉辦,聚焦集成電路、5G通訊模組、光電通信等領(lǐng)域,融合系統(tǒng)集成產(chǎn)業(yè)鏈,從微組裝到先進(jìn)封裝,匯聚智造創(chuàng)新,洞察前沿新知,參會(huì)⑥重好禮,立即報(bào)名,搶占稀缺席位。

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27290瀏覽量

218086 -

封裝

+關(guān)注

關(guān)注

126文章

7873瀏覽量

142893 -

晶體管

+關(guān)注

關(guān)注

77文章

9682瀏覽量

138080 -

倒裝芯片

+關(guān)注

關(guān)注

1文章

90瀏覽量

16245

原文標(biāo)題:什么是倒裝芯片(Flip-Chip)和芯片級(jí)封裝(Chip-Scale Package)?

文章出處:【微信號(hào):CEIA電子智造,微信公眾號(hào):CEIA電子智造】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

計(jì)算機(jī)芯片級(jí)維修中心(芯片級(jí)維修培訓(xùn)教材)

倒裝芯片和晶片級(jí)封裝技術(shù)及其應(yīng)用

OL-LPC5410晶圓級(jí)芯片級(jí)封裝資料分享

引腳架構(gòu)芯片級(jí)封裝(LFCSP)設(shè)計(jì)與制造指南

AN-772引腳架構(gòu)芯片級(jí)封裝(LFCSP)設(shè)計(jì)與制造指南

倒裝芯片CSP封裝

AN-772: 引腳架構(gòu)芯片級(jí)封裝(LFCSP)設(shè)計(jì)與制造指南

實(shí)現(xiàn)芯片級(jí)封裝的最佳熱性能

倒裝芯片的優(yōu)勢(shì)_倒裝芯片的封裝形式

倒裝芯片和芯片級(jí)封裝的由來(lái)

倒裝芯片和芯片級(jí)封裝的由來(lái)

評(píng)論