實驗目的

實驗任務

設計一個4位奇偶校驗器電路。要求當輸入的4位二進制碼中有奇數個“1”時,輸出為“1”,否則輸出為“0”。

實驗原理

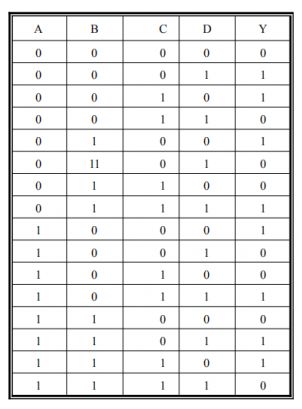

奇偶校驗,即判斷輸入變量中1的個數。當輸入變量中1的個數是奇數時,輸出為1。當輸入變量中1的個數是偶數時,輸出為0。真值表及邏輯表達式如下所示:

Y=A’B’C’D+A’B’CD’+A’BC’D’+A’BCD+AB’C’D’+AB’CD+ABC’D+ABCD’

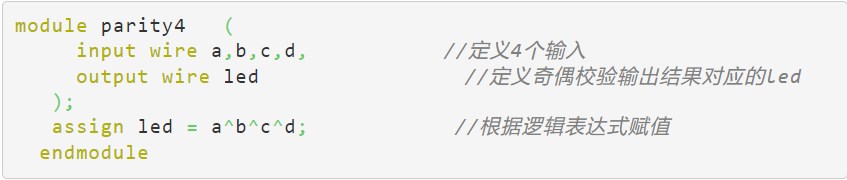

經過化簡得到:Y=A⊕B⊕C⊕D

邏輯電路

Verilog HDL建模描述

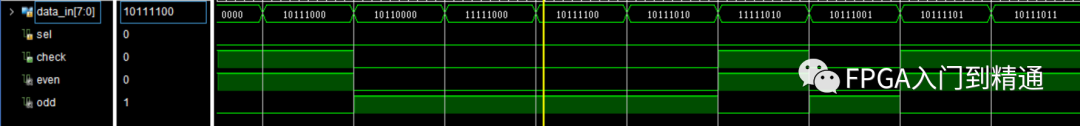

實驗步驟

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

二進制

+關注

關注

2文章

795瀏覽量

41643 -

奇偶校驗器

+關注

關注

0文章

7瀏覽量

7128 -

數字電路

+關注

關注

193文章

1605瀏覽量

80578 -

FPGA開發

+關注

關注

1文章

43瀏覽量

14911 -

HDL語言

+關注

關注

0文章

47瀏覽量

8913

發布評論請先 登錄

相關推薦

UART中有奇偶校驗位和無奇偶校驗位的數據傳輸是怎樣的?

例如,我使用 8 位數據傳輸類型。奇偶校驗位共有 3 種類型無奇偶校驗偶校驗奇校驗----------------------偶校驗我假設

發表于 12-08 07:24

單片機串口分析起始位停止位奇偶校驗位

串口解析串口配置1.波特率2.停止位3.數據位4.奇偶校驗位比特率:通訊的頻率停止位:可以選擇1/1.5/2三個選擇數據

發表于 11-20 10:36

?16次下載

增強FIFO模式下的奇偶校驗

自昊芯推出專題講解SCI串口通訊奇偶校驗,分為兩期講解,上期主要講解標準SCI模式下的奇偶校驗,本期主要講解增強FIFO模式下的奇偶校驗。

FPGA奇偶校驗的基本原理及實現方法

在數字電路中,數據的正確性非常重要。為了保證數據的正確性,在傳輸數據時需要添加一些冗余信息,以便在接收端進行校驗。其中一種常用的校驗方式是奇偶校驗(Parity Check)。本文將介

什么是奇偶校驗 奇偶校驗的基本原理 奇偶校驗電路什么意思

什么是奇偶校驗 奇偶校驗的基本原理 奇偶校驗電路什么意思? 奇偶校驗是一種用于檢測二進制數據中錯誤的方法。它的基本原理是在二進制數據的末尾添

什么是奇校驗和偶校驗?常見的奇偶校驗方式有哪些?

什么是奇校驗和偶校驗?常見的奇偶校驗方式有哪些? 1. 奇偶校驗是指在數字通信中采用一種技術對傳輸的數據進行

奇偶校驗和crc校驗的區別 CRC校驗和奇偶校驗之間有什么關系?

方法都可以檢測出特定類型的錯誤。 奇偶校驗是一種簡單的校驗方法,適用于串行傳輸數據,主要用于檢測傳輸中的單比特錯誤。其原理是通過添加一個校驗位來使原始數據的奇偶性成為對稱的,通過接收端

數字電路實驗—4位奇偶校驗器設計

數字電路實驗—4位奇偶校驗器設計

評論