低功耗FSMs

低功耗設計是當下的需要!這篇文章:低功耗設計方法論的必要性讓我們深入了解了現代設計的意圖和對功耗感知的需求。在低功耗方法標簽下的時鐘門控和電源門控的后續文章中,討論了一些SoC低功耗設計的方法。在這篇文章中,我們將考慮一個這樣的低功耗設計的FSM,可以推廣到任何低功耗時序電路的設計。

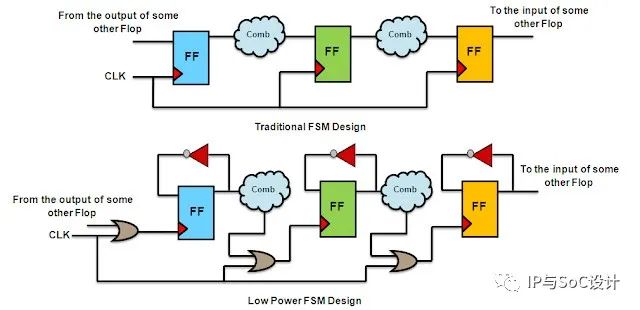

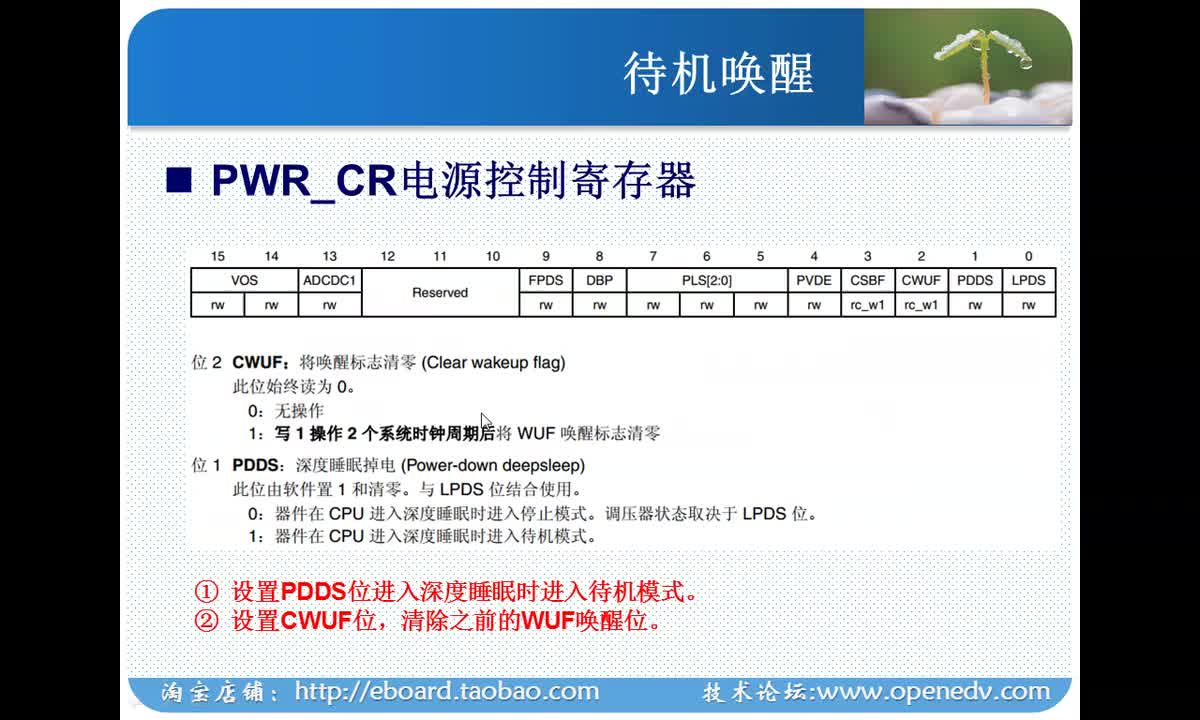

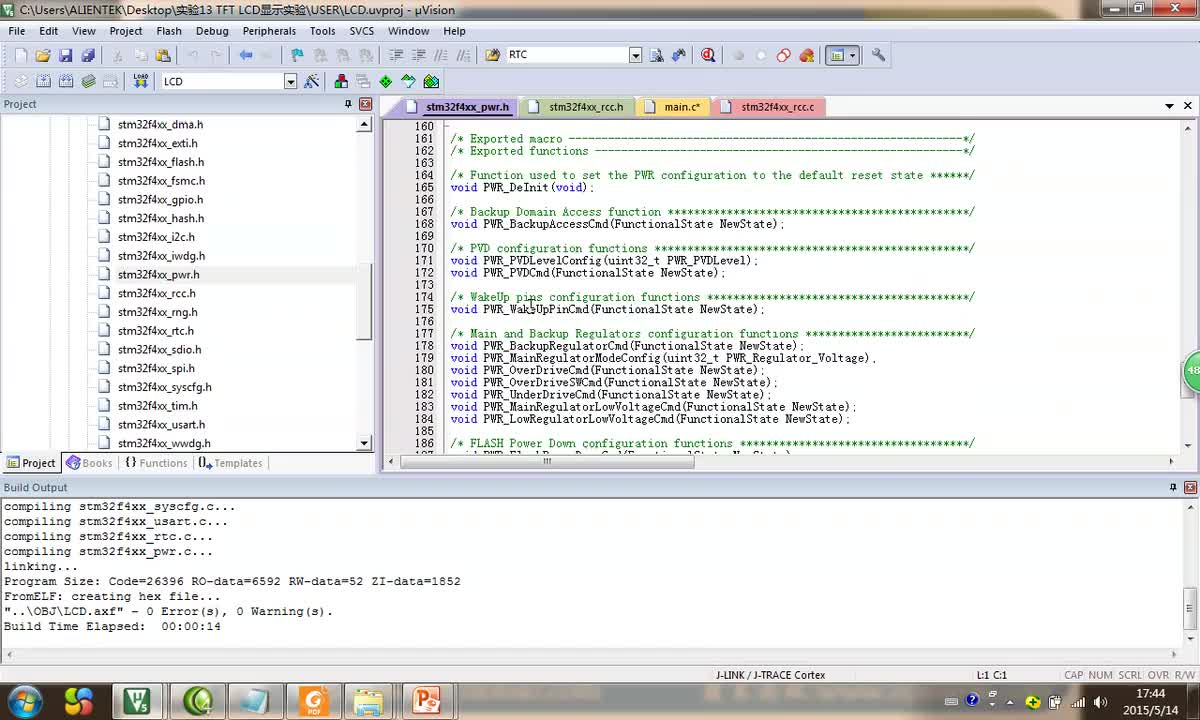

考慮以下傳統和低功耗FSM的通用設計:

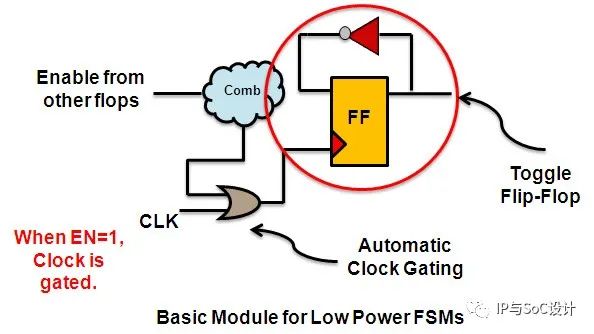

讓我們來討論一下我們在這里使用過的基本構建塊。"或"門作為觸發器的時鐘門。我們使用的觸發器是一個觸發器。當 enable = 0 時,觸發器接收時鐘,并切換其狀態。所以,每當我們需要改變翻牌的狀態時,我們可以給出一個時鐘脈沖。

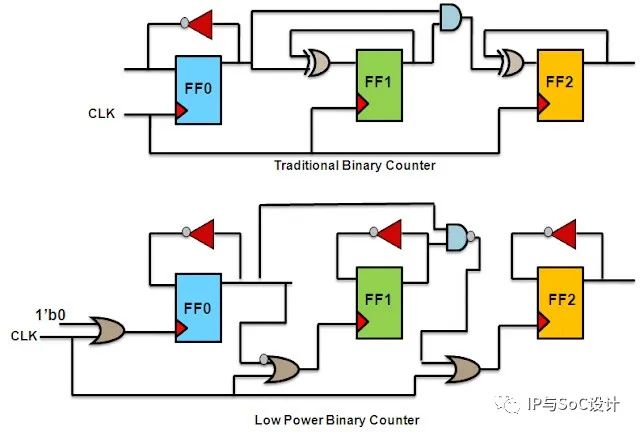

說得夠多了!現在我們來討論一個基本同步計數器的真實例子。以及如何利用上述方法設計一個低功耗同步計數器。

在任何二進制計數器中:

·最低階位在每個時鐘周期后切換。

·只有當所有低階位都在邏輯1時,任何高階位才進行切換。

記住這一點,我們現在可以建立低功耗計數器!!

審核編輯:湯梓紅

-

soc

+關注

關注

38文章

4161瀏覽量

218162 -

時序電路

+關注

關注

1文章

114瀏覽量

21696 -

觸發器

+關注

關注

14文章

2000瀏覽量

61132 -

低功耗設計

+關注

關注

0文章

80瀏覽量

16157

原文標題:博文速遞:Low Power FSMs

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【專題】低功耗電路設計__低功耗設計技巧

低功耗藍牙怎么低功耗?如何界定

AD,低功耗

低功耗電路設計_低功耗設計方法

什么是低功耗,對FPGA低功耗設計的介紹

還在了解什么是低功耗?FPGA低功耗設計詳解

如何使用Freeze技術實現低功耗設計

低功耗設計

FSMs低功耗設計

FSMs低功耗設計

評論