Zynq系列處理器包含了ARM和FPGA,與ARM處理器+FPGA這種兩個(gè)處理器相比最大的特點(diǎn)就是兩種結(jié)構(gòu)的數(shù)據(jù)交互在芯片內(nèi)部進(jìn)行。既節(jié)約了接口,有提升了交互速度。

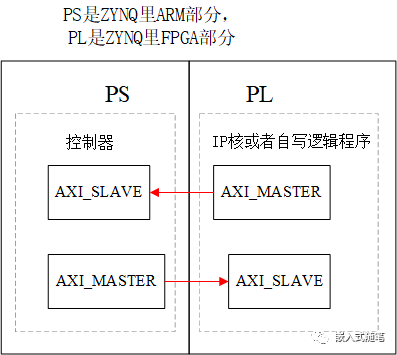

內(nèi)部交互主要是使用AXI接口。AXI是一種主從接口。雖然看起來很復(fù)雜,但也是主機(jī)發(fā)送地址然后讀寫數(shù)據(jù)。PS端通過芯片內(nèi)控制器來發(fā)送或者接收AXI接口信號,和SPI之類的主從接口一樣。

PL端通過IP核或者自寫的邏輯程序收發(fā)AXI接口程序。

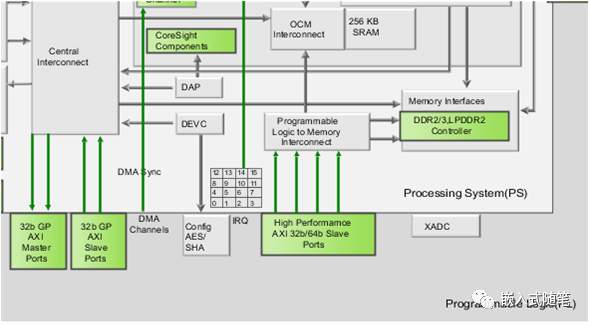

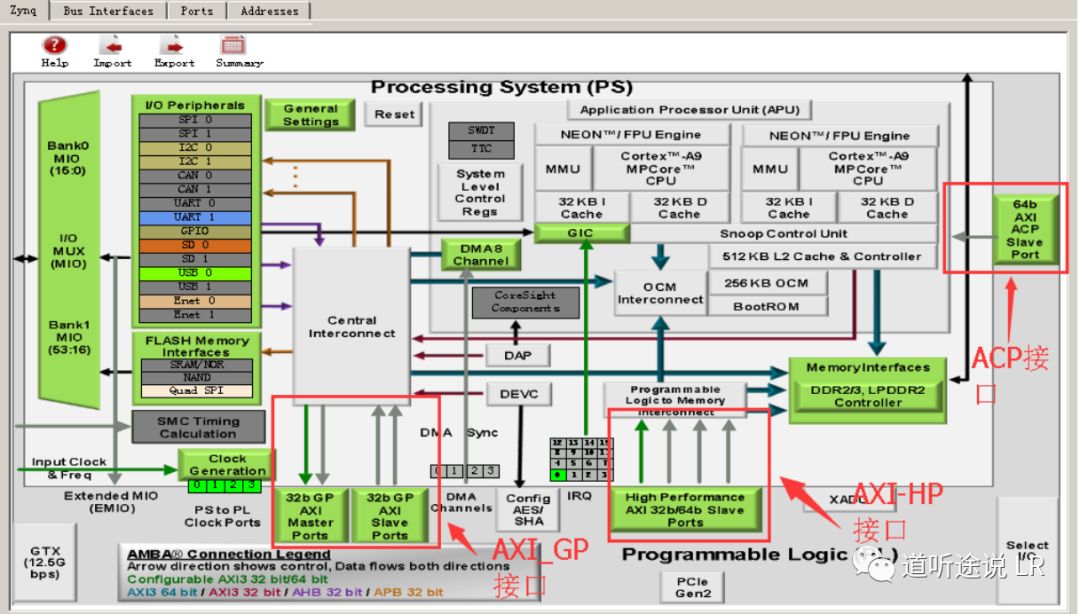

通過如下的圖(ZYNQ7000系列的)可以看出PS端的GP AXI連接一個(gè)控制器,HP AXI連接一個(gè)控制器。

如上圖所示,這個(gè)型號的GP AXI可以作為主機(jī)也可以作為從機(jī),來與PL端交互數(shù)據(jù)。HP AXI的傳輸速度快,通過Programmable Logic to Memory Interconnect可以連接到DDR控制器,可以訪問DDR數(shù)據(jù)。流程是:PL端的邏輯程序發(fā)出AXI接口的時(shí)序信號,Programmable Logic to Memory Interconnect接收到后轉(zhuǎn)化成可以訪問DDR控制器的信號來讀寫數(shù)據(jù)。

-

處理器

+關(guān)注

關(guān)注

68文章

19535瀏覽量

231855 -

FPGA

+關(guān)注

關(guān)注

1635文章

21837瀏覽量

608330 -

接口

+關(guān)注

關(guān)注

33文章

8775瀏覽量

152396 -

Zynq

+關(guān)注

關(guān)注

10文章

611瀏覽量

47486 -

AXI

+關(guān)注

關(guān)注

1文章

130瀏覽量

16831

發(fā)布評論請先 登錄

相關(guān)推薦

Xilinx zynq AXI總線全面解讀

玩轉(zhuǎn)Zynq連載34——[ex54] 基于Zynq的AXI GP總線的從機(jī)接口設(shè)計(jì)

玩轉(zhuǎn)Zynq連載37——[ex56] 基于Zynq的AXI HP總線讀寫實(shí)例

關(guān)于Zynq的理論部分

何謂 AXI?關(guān)于AXI3/AXI4的相關(guān)基礎(chǔ)知識

AXI_GP接口和AXI_HP接口的相關(guān)內(nèi)容

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

ZYNQ基礎(chǔ)---AXI DMA使用

Zynq系列處理器中AXI接口的使用

Zynq系列處理器中AXI接口的使用

評論