如前所述,數(shù)據(jù)緩存是創(chuàng)建高效DNN加速器的關(guān)鍵組件之一。因此,除了選擇適當(dāng)?shù)臄?shù)據(jù)流(控制數(shù)據(jù)緩存的位置和時(shí)間)外,DNN加速器還需要一個(gè)緩存方案,該方案應(yīng)尋求實(shí)現(xiàn)以下目標(biāo):

l 以高效并及時(shí)的方式準(zhǔn)確地傳送數(shù)據(jù)的consumer需要的數(shù)據(jù);

l 將未來所需數(shù)據(jù)的接收與當(dāng)前正在使用的數(shù)據(jù)的使用重疊;

l 在不再需要數(shù)據(jù)時(shí)刪除數(shù)據(jù);

l 通過同步來完成上述所有操作。

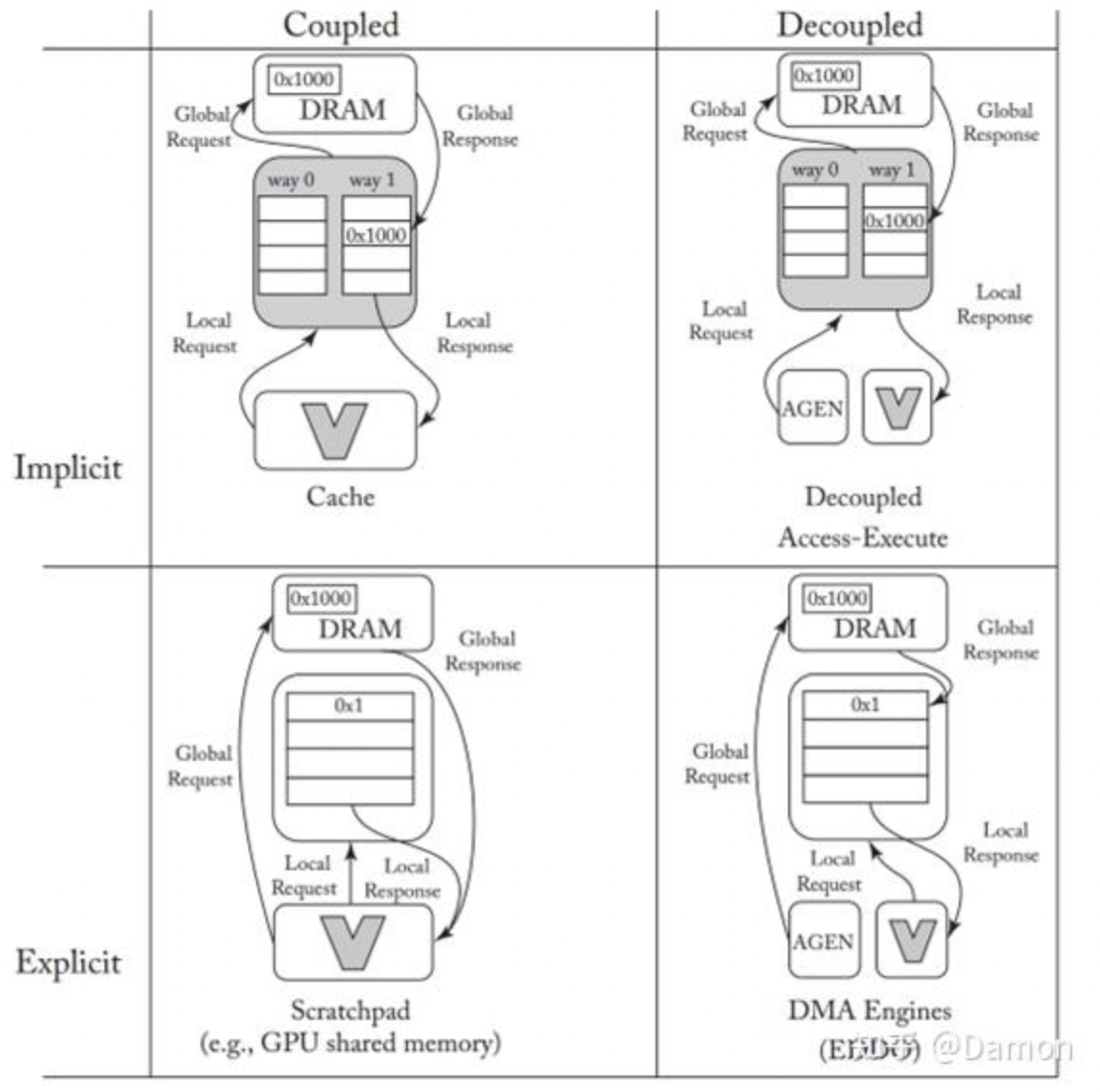

一般來說,可以實(shí)現(xiàn)這些目標(biāo)的稱為實(shí)現(xiàn)良好的數(shù)據(jù)編排。[170]中對(duì)當(dāng)前數(shù)據(jù)編排方法的分類如圖5.29所示。在圖中,buffer的用法沿著兩個(gè)軸進(jìn)行劃分。在較高的層次上,沿一個(gè)軸的implicit/explicit區(qū)分是指利用工作負(fù)載來控制數(shù)據(jù)緩沖決策的程度,而在另一個(gè)軸上的coupled/decoupled是指內(nèi)存響應(yīng)和請(qǐng)求是往返(請(qǐng)求-響應(yīng))還是向前流(自動(dòng)將數(shù)據(jù)推送給consumer)。

圖5.29: 數(shù)據(jù)編排方法的分類。假設(shè)通信(帶箭頭的線)在硬件通道(通常是 NoC 鏈路)上傳輸。 (圖來自[170])

5.8.1 隱式與顯式編排

在通用計(jì)算中,cache是主要的緩沖機(jī)制,并且基于加載/存儲(chǔ)操作。緩存有幾個(gè)理想的屬性,例如以不可見的方式組合成層次結(jié)構(gòu)。內(nèi)存級(jí)并行性(多個(gè)未完成的填充以及填充和訪問當(dāng)前內(nèi)容之間的并發(fā)性)可以使用經(jīng)過充分研究的附加硬件(通常稱為無鎖緩存結(jié)構(gòu))來實(shí)現(xiàn)。

Cache可以被描述為執(zhí)行implicit式數(shù)據(jù)編排,因?yàn)榧虞d請(qǐng)求發(fā)起者不直接控制緩存層次結(jié)構(gòu)關(guān)于響應(yīng)數(shù)據(jù)是否保留在存儲(chǔ)層次結(jié)構(gòu)的任何給定級(jí)別上的決策,也不直接控制何時(shí)刪除響應(yīng)數(shù)據(jù)。啟發(fā)式替換策略在通用場(chǎng)景中是有利的,因?yàn)樗鼈兣c工作負(fù)載無關(guān)。另一方面,對(duì)于DNN加速器來說,標(biāo)簽匹配和關(guān)聯(lián)集等特征的面積和能量開銷很高。

Cache的另一種替代方法是使用scratchpad,它為加載和存儲(chǔ)了特定暫存緩沖區(qū)的地址范圍,從而支持對(duì)數(shù)據(jù)編排的顯式和精確控制 (在圖5.29中,這是由管理本地和全局請(qǐng)求/響應(yīng)的數(shù)據(jù)路徑表示的)。GPU的共享scratchpad [171]是這種顯式數(shù)據(jù)編排習(xí)慣用法的一個(gè)例子。scratchpad的大小和地址范圍在體系結(jié)構(gòu)上是公開的,數(shù)據(jù)進(jìn)出scratchpad的傳輸是通過明確的指令進(jìn)行管理的。雖然scratchpad避免了緩存的硬件開銷,但提取內(nèi)存并行性(跨填充和重疊填充和訪問)既繁瑣又容易出錯(cuò),因此很難將它們組合成層次結(jié)構(gòu)。

5.8.2 耦合和解耦編排

緩存和暫存區(qū)都使用加載/存儲(chǔ)模式,其中請(qǐng)求的發(fā)起方也接收響應(yīng)。這被稱為數(shù)據(jù)的耦合分段,反映在圖5.29的左列中。有了這種設(shè)置,數(shù)據(jù)需求和數(shù)據(jù)可用性之間的同步既高效又直觀——當(dāng)相應(yīng)的響應(yīng)返回時(shí)(load-use)會(huì)通知請(qǐng)求者。缺點(diǎn)是,由于單個(gè)requester/consumer必須在請(qǐng)求和使用響應(yīng)之間交替,它使數(shù)據(jù)塊的填充和訪問重疊(例如,通過雙緩沖)變得復(fù)雜。此外,傳入數(shù)據(jù)tile的“l(fā)anding zone”必須在整個(gè)往返加載延遲期間保留(因此是空閑的),這增加了內(nèi)存資源的壓力,否則內(nèi)存資源可能會(huì)用于更大的瓦tile size。

另一種選擇是將負(fù)載請(qǐng)求啟動(dòng)器與響應(yīng)接收器解耦(在圖5.29中,這由指向不同模塊的請(qǐng)求/響應(yīng)箭頭表示)。在這種設(shè)置中,一個(gè)單獨(dú)的硬件模塊(例如DMA引擎或地址生成器(AGEN))負(fù)責(zé)將數(shù)據(jù)推入一個(gè)或多個(gè)功能單元的緩沖器。為了容忍延遲,這些緩沖器通常是雙緩沖的,有時(shí)被稱為ping-pong buffers [172, 173]。這種方法的主要優(yōu)點(diǎn)是,請(qǐng)求者可以以自己的速率運(yùn)行,并且可以將數(shù)據(jù)多播到多個(gè)同時(shí)使用的用戶。此外,pipeline的前饋特性意味著只需要按層次結(jié)構(gòu)相鄰級(jí)別之間的延遲比例保留tile landing zone,而不是整個(gè)層次結(jié)構(gòu)遍歷往返,從而增加對(duì)同等大小內(nèi)存的利用率。最后,這種方法通常可以傳輸大數(shù)據(jù)塊(即批量傳輸,這比小請(qǐng)求更有效),這些數(shù)據(jù)塊必須動(dòng)態(tài)地重新合并對(duì)同一內(nèi)存行的訪問。

這種分離的producer/consumer方法類似于Smith[174]的通用計(jì)算架構(gòu)的decoupled access execute (DAE)風(fēng)格。在DAE組織中,兩個(gè)處理器通過硬件隊(duì)列連接。訪問處理器負(fù)責(zé)執(zhí)行所有地址計(jì)算和生成負(fù)載——類似于DMA引擎。負(fù)載響應(yīng)被傳遞給執(zhí)行處理器——類似于加速器的功能單元及其本地staging緩沖區(qū)。DAE提高了并行性,減少了指令的關(guān)鍵路徑,同時(shí)允許兩個(gè)處理器以其自然速率進(jìn)行計(jì)算。然而經(jīng)典的DAE并沒有顯式地控制數(shù)據(jù)編排緩沖區(qū)——關(guān)于暫存在數(shù)據(jù)的決策仍然由緩存層次管理,因此圖5.29將DAE歸類為隱式解耦。

5.8.3 顯式解耦數(shù)據(jù)編排(EDDO)

DNN加速器中最常見的緩沖方法是顯式解耦數(shù)據(jù)編排(EDDO)。硬件FIFO[175,176]是一種傳統(tǒng)的可重用EDDO分段緩沖結(jié)構(gòu)。其優(yōu)點(diǎn)是FIFO通過頭指針和尾指針清晰地封裝了同步,并且易于分層組合。然而在實(shí)踐中FIFO不夠靈活,無法滿足DNN加速器的需求,因?yàn)镈NN加速器經(jīng)常在一個(gè)窗口內(nèi)重復(fù)訪問(例如,在執(zhí)行卷積時(shí))。此外,對(duì)于部分和之類的數(shù)據(jù)類型,分級(jí)數(shù)據(jù)必須在清除之前進(jìn)行多次修改。這在沒有昂貴的再循環(huán)的單寫端口FIFO中是不可能的。

一些深度神經(jīng)網(wǎng)絡(luò)加速器[142, 152, 159, 177, 178]已經(jīng)將顯式解耦數(shù)據(jù)編排(EDDO)方案作為定制緩沖機(jī)制納入其中,并提出了其他特定的EDDO緩沖方案,如DESC[179]。然而,為了說明典型的EDDO方案將描述buffets[170],它是Eyeriss[101]中數(shù)據(jù)編排方案的概括。

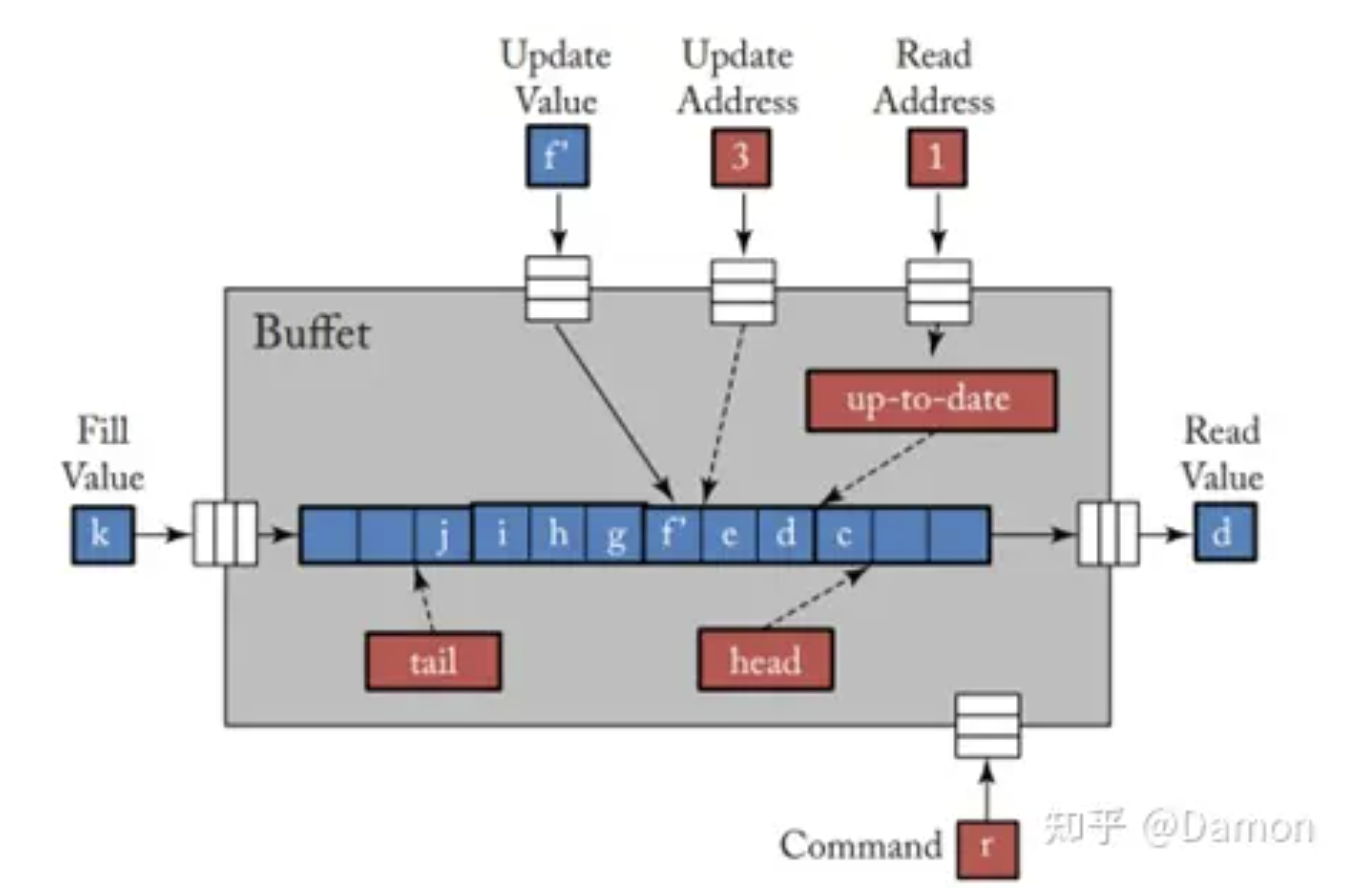

從本質(zhì)上講,buffet的操作就像FIFO一樣,值從輸入NoC鏈路(即硬件通信通道)填充到由頭和尾指針控制的圓形緩沖區(qū)中。只有當(dāng)填充發(fā)生時(shí),值才會(huì)從填充NoC鏈接中刪除。對(duì)緩沖區(qū)中的數(shù)據(jù)的訪問是由讀取命令提供的,但是與只能在其頭部讀取的FIFO不同,buffet讀取增加了一個(gè)地址,這被解釋為頭部的偏移量。在buffet中保留一組值并多次讀取它們可以重用數(shù)據(jù)塊。與填充類似,read命令只在讀取值可以在讀取值NoC鏈路上發(fā)送時(shí)才會(huì)執(zhí)行(即,NoC鏈路沒有阻塞)。

Buffets還支持在其緩沖區(qū)中更新值。只允許更新之前讀過的值,并使用read+update命令讀取位置的值。這使得buffet支持存儲(chǔ)和更新partial sum。

最后,buffet提供了一個(gè)shrink操作,從緩沖區(qū)的頭部刪除指定數(shù)量的項(xiàng)。shrink可以讓人輕松地釋放tile占用的空間。為了避免在切換tile時(shí)發(fā)生延遲,可以定義一個(gè)比buffet尺寸小的tile。因此,在處理前一個(gè)tile片時(shí),可以開始填充下一個(gè)tile。然而,額外的空間只需要足夠大,就避免在下一個(gè)tile上開始工作之前的啟動(dòng)瞬態(tài)。這通常比雙緩沖所需的空間要小得多。

shrink不需要移除整個(gè)tile。只移除tile的一部分(例如,只移除一個(gè)值),然后從零偏移開始按順序再次讀取,這樣buffets就可以支持滑動(dòng)窗口。

圖5.30給出了buffet的框圖。當(dāng)操作(命令或填充)所需的所有輸入NoC鏈接上都有值,并且輸出NoC鏈接中有空間(僅用于讀取)時(shí),就會(huì)發(fā)生操作。圖中所示的活動(dòng)如下。

圖5.30: buffet框圖: 主要的輸入是一個(gè)fill value; a read address and read value; an update address, and update value; 以及一個(gè)command,可以指定是執(zhí)行讀取、讀取+更新還是shrink。唯一的輸出是一個(gè)read value。head、tail和date單元在內(nèi)部提供了同步,通過暫停操作來保持正確的順序。

l 正在調(diào)用read命令(r),該read命令將讀取地址(1)作為從head的偏移量來產(chǎn)生read value(d)

l Update address (3)處的更新正在將update value(f’)寫入buffet。請(qǐng)注意,這是允許的,因?yàn)檩^早的命令必須是偏移量3處的read+update

l Fill value(k)即將寫入buffet的尾部tail

上述所有活動(dòng)都是在buffet內(nèi)部通過head、tail和最新狀態(tài)進(jìn)行協(xié)調(diào)的,這保證了正確的ordering。例如,一個(gè)read操作必須等待數(shù)據(jù)filled and updated (如果之前有一個(gè)read+update)。fill必須等到緩沖區(qū)有空間。

這里沒有說明shrink命令,它只是在等待未完成的更新后調(diào)整頭部指針,從buffet頭部刪除給定數(shù)量的值。

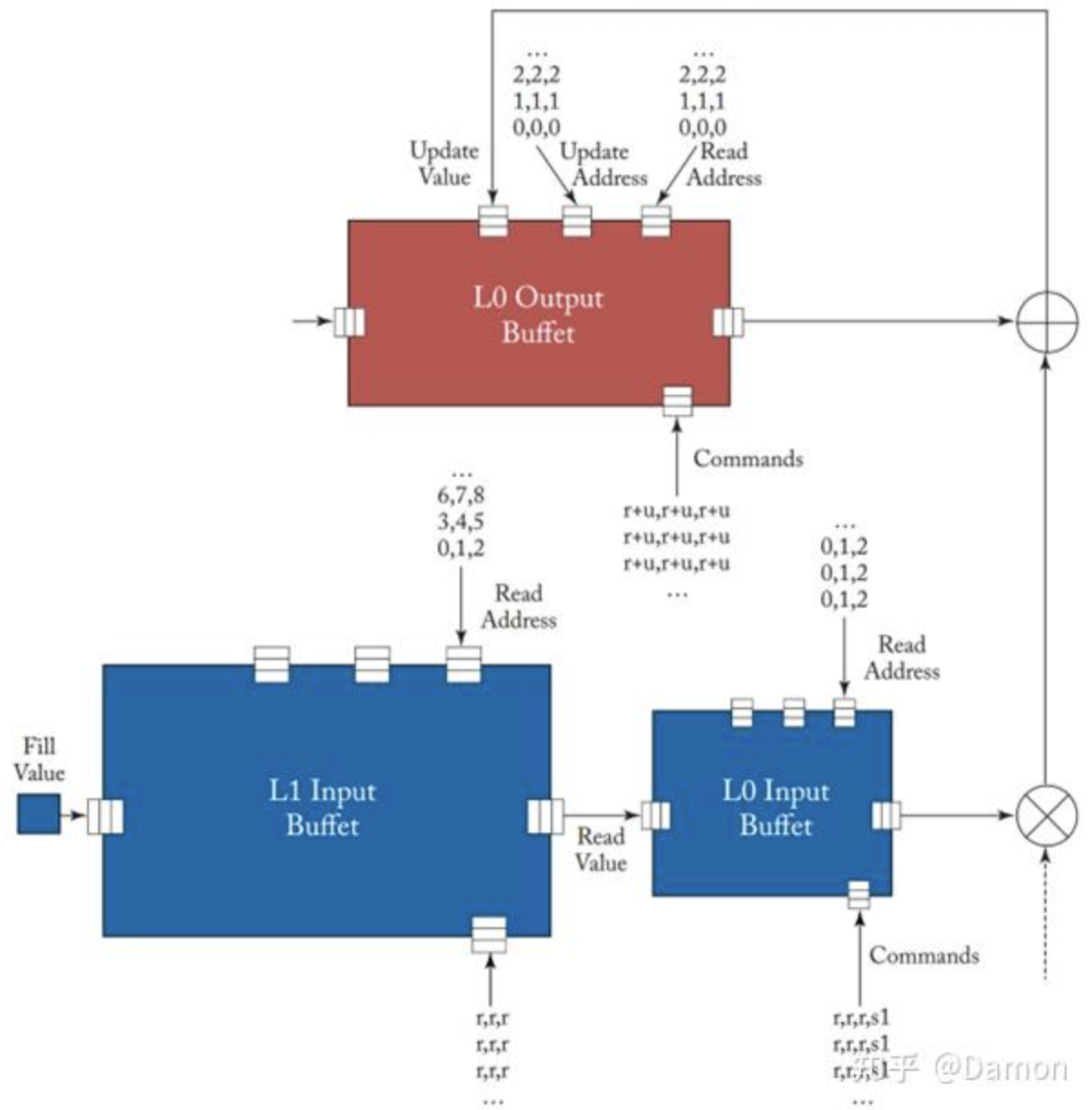

圖5.31展示了一個(gè)簡單的示例,演示了buffet是如何自然組合的,并可以用來處理滑動(dòng)窗口和更新。L1輸入buffet與L0輸入buffet的自然組合允許外部無同步填充,因?yàn)樘畛溆擅總€(gè)buffet的內(nèi)部排序控件控制。在L0 Input Buffet中的1個(gè)shrink會(huì)創(chuàng)建一個(gè)輸入滑動(dòng)窗口,因此輸入的相對(duì)序列將是0, 1, 2, 1, 2, 3, 2, 3, 4......內(nèi)部同步還控制partial sum的更新。

圖5.31: buffet示例——一個(gè)類似于Eyeriss的全局緩沖區(qū)和使用buffet構(gòu)建的PE的示例。對(duì)L1輸入buffet的讀取填充L0 buffet,L0 buffet執(zhí)行讀取,將輸入滑動(dòng)窗口傳遞給乘法器。L0輸出緩沖區(qū)執(zhí)行一系列read+update命令來生成partial sum。Weight buffet沒有顯示。

總之,在DNN加速器設(shè)計(jì)中需要有效的數(shù)據(jù)編排,并且通常由管理數(shù)據(jù)移動(dòng)的機(jī)制(如buffet)提供。這通常在設(shè)計(jì)中表現(xiàn)為明確的控制,其中數(shù)據(jù)在存儲(chǔ)層次結(jié)構(gòu)中被確定地推送,避免了昂貴的往返通信,并最大限度地減少了“l(fā)anding space”存儲(chǔ)需求。通過解耦的活動(dòng)還可以提高效率,其中硬件提供所需值的本地確定和本地同步控制。顯然,并非每個(gè)存儲(chǔ)緩沖區(qū)都需要buffet的完整語義,因此可以采用這些語義子集的優(yōu)化實(shí)現(xiàn)或其他提供類似好處的自定義設(shè)計(jì)。

-

加速器

+關(guān)注

關(guān)注

2文章

796瀏覽量

37838 -

緩沖器

+關(guān)注

關(guān)注

6文章

1921瀏覽量

45473 -

FIFO存儲(chǔ)

+關(guān)注

關(guān)注

0文章

103瀏覽量

5968 -

AI芯片

+關(guān)注

關(guān)注

17文章

1879瀏覽量

34990

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

深入理解DNN加速器中的基本單元——DSP

家居智能化,推動(dòng)AI加速器的發(fā)展

使用AMD-Xilinx FPGA設(shè)計(jì)一個(gè)AI加速器通道

【書籍評(píng)測(cè)活動(dòng)NO.18】 AI加速器架構(gòu)設(shè)計(jì)與實(shí)現(xiàn)

《 AI加速器架構(gòu)設(shè)計(jì)與實(shí)現(xiàn)》+第2章的閱讀概括

一種基于FPGA的高性能DNN加速器自動(dòng)生成方案

UIUC推出最新DNN/FPGA協(xié)同方案 助力物聯(lián)網(wǎng)終端設(shè)備AI應(yīng)用

借助 NVIDIA 融合加速器開發(fā)套件加速數(shù)據(jù)中心 AI

什么是AI加速器 如何確需要AI加速器

用于 AI 應(yīng)用的硬件加速器設(shè)計(jì)師指南

使用AXI CDMA制作FPGA AI加速器通道

使用賽靈思Alveo加速器卡加速DNN

PCIe在AI加速器中的作用

AI芯片設(shè)計(jì)DNN加速器buffer管理策略

AI芯片設(shè)計(jì)DNN加速器buffer管理策略

評(píng)論