PCIe接口自從被推出以來,已經成為了PC和Server上最重要的接口。為了更高了數據吞吐率,PCI-SIG組織不斷刷新接口標準,從PCIe 3.0的8GT/s數據速率,到PCIe 4.0的16GT/s數據速率,再到PCIe 5.0的32GT/x。PCI-SIG組織實現了在速率翻倍的同時,仍能保持使用普通的FR4板材和廉價接插件,主要源自兩個方面的改進,一是使用128b/130b編碼來代替8b/10b編碼,使得編碼效率大幅提高;另一個是使用動態均衡技術,來代替先前代的靜態均衡技術。

這里聚焦于PCIe 3.0和4.0中的動態均衡技術,介紹其原理、實現及其相關的一致性測試。這樣一種動態均衡技術,在spec中被稱作“Link Equalization”(鏈路均衡,簡稱為LEQ)。本系列文章分上下兩篇,本文理論篇主要介紹PCIe 3.0/4.0的鏈路均衡的工作原理,下一篇實踐篇則側重于鏈路均衡的測試和調試。

PCIe 3.0 & 4.0的鏈路均衡

在PCIe 3.0和4.0中的鏈路均衡技術相較于先前代要復雜得多,這樣一種動態均衡技術可以分為兩個方面進行討論。

均衡特性方面:從這個方面來說,相對于先前代的均衡來說,3.0和4.0中的均衡技術的硬件性能指標要求更高了。

協議方面:為了實現動態地調整均衡設置,需要協議層的配合,這是通過PHY層的LTSSM狀態機中的Recovery.Equalization子狀態來實現的。

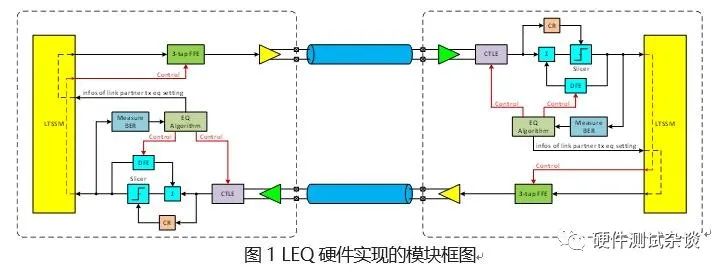

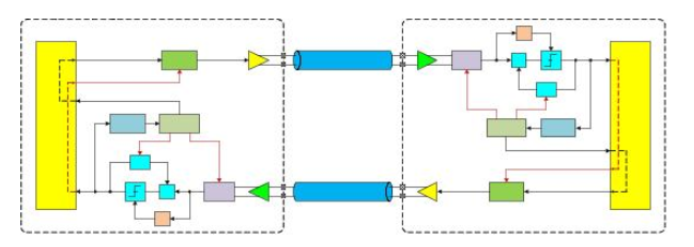

先來從均衡特性的角度來看看PCIe 3.0和4.0的均衡,如下展示了在PCIe 3.0/4.0中所使用的全部均衡技術,在Tx端有FFE(Feed Forward Equalizer,前饋均衡器);在Rx端有:CTLE(Continuous Time Linear Equalizer,連續時間線性均衡器)和DFE(Decision Feedback Equalizer,判決反饋均衡器)。通過FFE和CTLE,可以去除大部分由ISI所引入的抖動;通過DFE可以進一步去除ISI,它還能去除部分的阻抗失配所造成的反射。通過這些均衡處理,就能夠最大程度上地保證在接收端判決輸入處將眼圖打開。

除了上述這些均衡特性上的支持外,在協議層(LTSSM)中還規定需要通過協議的方式來動態調整鏈路上的均衡設定值,這整個過程稱作鏈路均衡(Link Equalization,LEQ)。在鏈路均衡過程中:

本地端按照某個初始Tx EQ的設定來發送數據;

對端在接收到數據時,會根據誤碼率或信號質量來判斷該Tx EQ是否合適;

若不合適,對端會通過協議向本地端請求一個新的Tx EQ值;

本地端在接收到這個請求值之后,會改變Tx EQ的值。

通過這一動態過程,就能夠保證鏈路上的Tx EQ為最優值。與此同時,本地端和對端也會同時調整Rx EQ。通過動態地調整Tx EQ和Rx EQ,就能夠靈活地適應不同的信道情況。

發送端的均衡:FFE

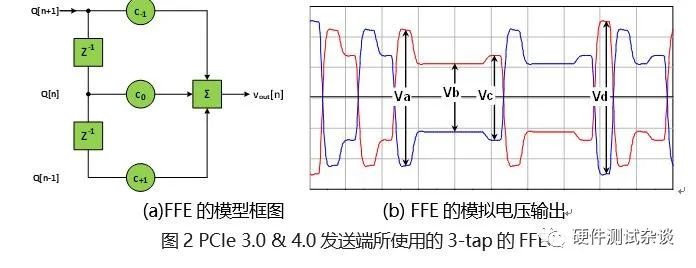

在PCIe 3.0 & 4.0中使用的都是3-tap FFE,如圖 2a所示。其中, 為數字信號,建模時取值為±1; 為FFE的抽頭系數; 為發送端的模擬信號輸出。

理想情況下的差分電壓幅度有:23÷2=4種可能性,這四個電壓幅度在PCIe標準中(如圖 2b所示)分別被標記為Va,Vb,Vc,Vd。

其中,Vb被稱作去加重電壓(de-emphasis voltage),Vc被稱作預沖電壓(preshoot voltage);Vd被稱作最大幅度電壓(boost voltage),PCIe標準中沒有為Va取一個專門的名字。在此基礎上,標準中通過三組比值來完備地描述FFE的性能:

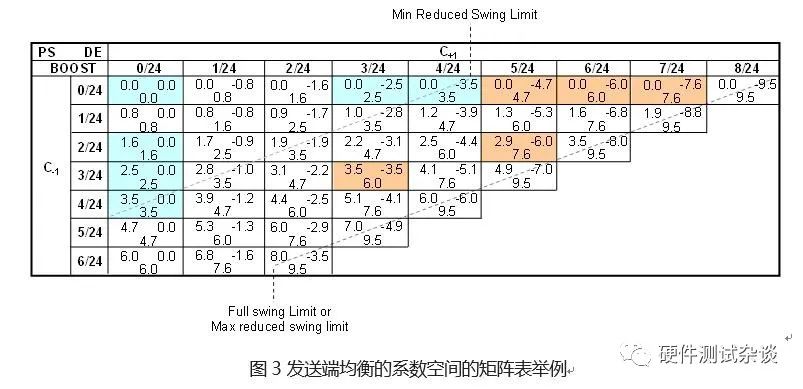

若不加限制的來說,那么 形成的組合有無窮多個。但并不是所有的組合在實際應用中都是合適的。其中一個最重要的約束條件就是:去加重電壓Vb不能過小,過小的去加重電壓會導致輸出信號在接收端的眼高過低。因此通過BOOST比值對去加重地電壓幅值進行限制:對于滿擺幅的Tx輸出,規范要求BOOST≤9.5dB;對于減擺幅的Tx輸出,規范要求BOOST≤3.5dB。最終會形成一個如圖 3類似的矩陣表,圖中系數的粒度為1/24。在實際應用中可以是其他的粒度值,例如1/64;更小的粒度能夠使系數空間的取值可能性更多,在LEQ調節時也更精細。

鑒于系數空間上的取值可能性較多,PCI-SIG協會在開發協議的過程中,廣泛地研究了在不同插入損耗下最優的系數取值組合;最后選定了若干個特定的系數取值組合,并把它們稱作預設定值(preset),在實際的LEQ過程中,鏈路雙方就可以先采用預設定值進行粗調;若還認為鏈路的均衡設置仍然沒有達到最優,可以進一步通過系數空間的方式進行細調,最終達到速度和精度的平衡。

接收端的均衡:CTLE和DFE

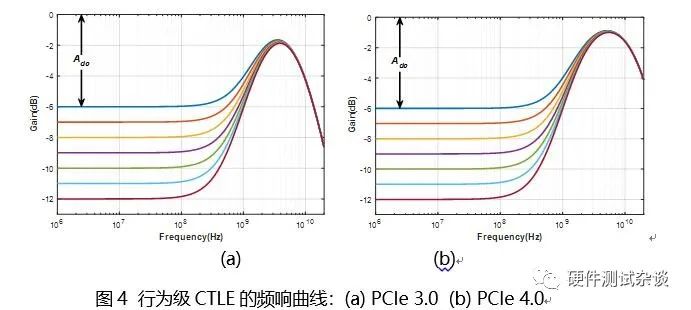

在PCIe 3.0 & 4.0 基礎規范中,并沒有明確地規定接收端的結構是怎樣的;而只是從測量的角度對接收端性能進行了規定。相反地,在規范中定義了一個行為級CTLE和行為級DFE。這些行為級模型可以作為設計指南;并且為了使得待測對象能夠通過規范的要求,一般來說用戶所設計的接收端性能至少要等于這些行為級模型的性能,可以強于這些行為級模型,但不能弱于這些行為級模型。

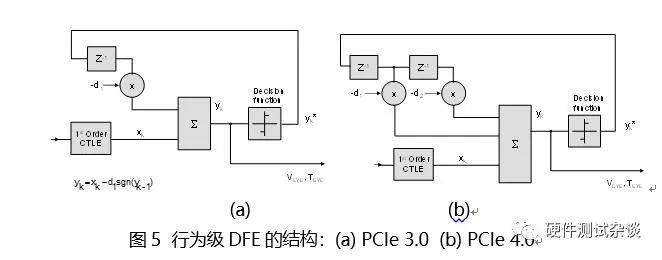

發送端的輸出在經過一段很長的FR4走線之后,僅僅使用CTLE,可能是不夠的。因此在PCIe 3.0 & 4.0中,還使用了DFE的技術。在3.0中,使用1-tap的DFE,而在4.0,由于速率相對于3.0翻倍了;所以使用2-tap的DFE,以便移除更大的ISI。

與線性均衡器FFE和CTLE相比,DFE為一種非線性均衡器。DFE的基本想法是:若已經正確接收了之前的比特數據的話;那么先前的比特數據對當前比特所產生的影響就是已知的;從而我們就可以通過反饋的方式進行補償,這樣就能夠進一步消除抖動和噪聲的影響。不難看出這里的非線性體現在:反饋回來的信號是經過判決之后的數字信號;而判決電路是一種非線性電路。顯然,反饋通路上的抽頭數目越多,那么對抖動和噪聲的消除可能就越好;這也就是為什么3.0中使用1-tap的DFE,而在4.0中使用2-tap的DFE。

鏈路均衡過程

鏈路上的兩端剛開始建立通信的時候,并不知道整個信道的物理特性是怎樣的,例如插入損耗多大,是否有阻抗不連續等。由于PCIe 3.0和4.0的插入損耗允許的變化范圍很大,一個靜態的均衡設置并不能覆蓋所有的情況。這樣就需要鏈路上的雙方根據當前物理信道的特性,來動態地調整均衡設置,使得均衡設置對于當前的物理信道來說是最優的。假設Port A和Port B是一個鏈路上的兩端,那么鏈路均衡過程要做的事情有:

配置Port A和Port B的初始均衡設置;

配置從Port A Tx à Port B Rx這一方向的均衡設置;

配置從Port B Tx à Port A Rx這一方向的均衡設置;

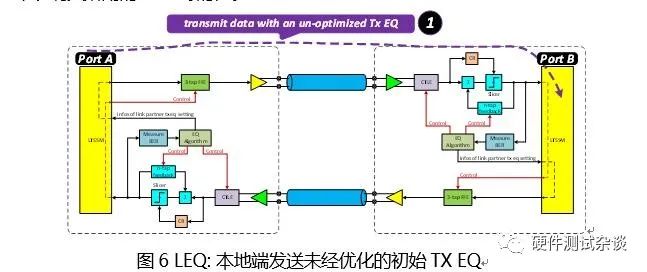

下面我們以Port A Tx à Port B Rx這一方向來說明鏈路均衡時如何實現的。如圖 6所示,在8GTs/或者16GT/s速率下的鏈路開始建立通信時,是以初始的未優化的TX EQ在發送TS1/TS2序列,并且Port A在TS1/TS2序列中表明其所用的TX EQ的值。

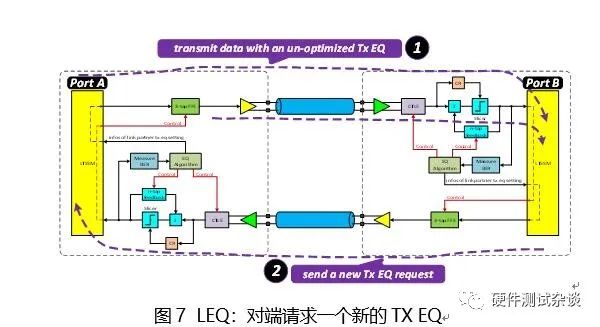

當Port B Rx在接收到這些TS1/TS2序列時,芯片內部存在一塊電路或者一套算法來評估當前的TX EQ是否合適,若認為不合適,就會如圖7所示,發送TS1序列來請求一個新的TX EQ。

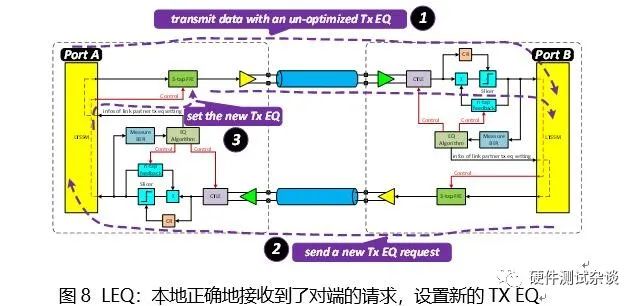

隨后,Port A會接收到請求設置TX EQ的TS1序列,如圖8所示,調整其TX端的FFE的設置。

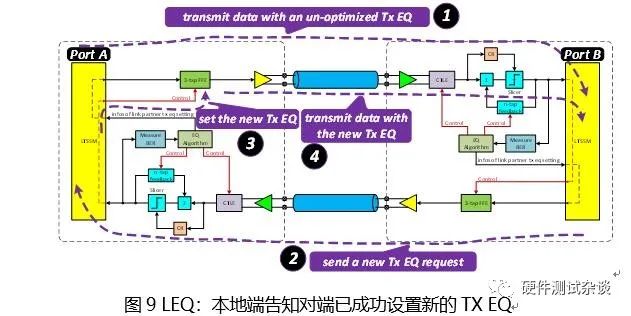

Port A在調整完Tx FFE的設置之后,如圖9所示,會將新的TX EQ設置值更新到TS1/TS2的序列之中,發送到Port B端。若Port B仍然覺得這個時候的TX EQ不是最優,那么仍然會重復圖中的2~4步驟,直到達到最優的TX EQ。當然上述過程并不能無限進行下去,必須要在大概32ms的范圍進行完。

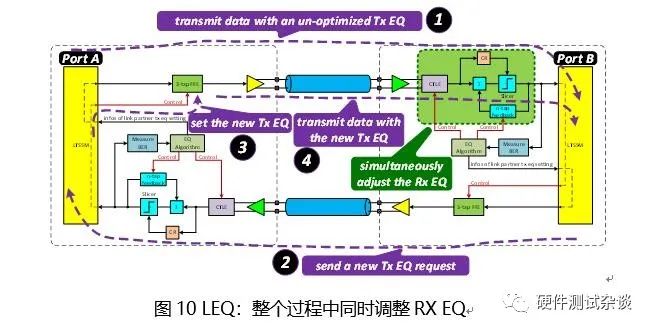

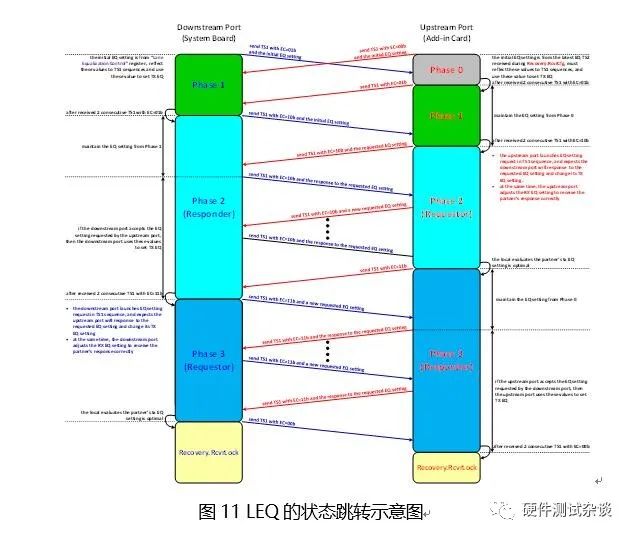

在上述24步驟的同時,Port B的RX端也在不停地調整其RX EQ,如圖 10所示。如圖6圖10中所討論的,LEQ是基于請求-響應機制來完成動態均衡的。在PCIe的規范中,LEQ總共包含四個階段:Phase 0、Phase 1、Phase 2、Phase 3。其中上行端口包含全部四個過程;而下行端口不包含Phase 0。

通過圖11不難看出,在LEQ過程中,上行端口和下行端口的行為是有區別的。以上描述的是在LEQ過程中鏈路上的雙方如何調整Tx EQ。而對于Rx EQ,根據Base規范中的說明,在整個LEQ的過程、以及在后續正常工作的過程中,鏈路雙方都可以一直調整Rx EQ。

審核編輯:劉清

-

編碼器

+關注

關注

45文章

3638瀏覽量

134426 -

均衡器

+關注

關注

9文章

210瀏覽量

30348 -

boost電路

+關注

關注

3文章

164瀏覽量

30333 -

PCIe接口

+關注

關注

0文章

120瀏覽量

9702 -

FFE

+關注

關注

0文章

8瀏覽量

1154

原文標題:PCIE3&4的接收端均衡技術

文章出處:【微信號:硬件測試雜談,微信公眾號:硬件測試雜談】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe Gen3/Gen4接收端鏈路均衡測試(上篇:理論篇)

PCIe Gen3/Gen4接收端鏈路均衡測試(下篇:實踐篇)

基于PCIe和V4L2的8通道視頻采集&顯示IP

供應EMI測試接收機R&S ESCI

力科PCIE 3.0系列文章之二——PCIE 3.0的動態均衡測試挑戰

如何區分Java中的&amp;和&amp;&amp;

if(a==1 &amp;&amp; a==2 &amp;&amp; a==3),為true,你敢信?

HarmonyOS &amp;amp;amp;潤和HiSpark 實戰開發,“碼”上評選活動,邀您來賽!!!

Channel怎么來匹配?發射端均衡器和接收端均衡器有怎么樣的玩法?

Open RAN的未來及其對AT&amp;T的意義

onsemi LV/MV MOSFET 產品介紹 &amp;amp; 行業應用

聚焦PCIE3&4的接收端均衡技術

聚焦PCIE3&4的接收端均衡技術

評論