1、前言

FPGA圖像采集領(lǐng)域目前協(xié)議最復(fù)雜、技術(shù)難度最高的應(yīng)該就是MIPI協(xié)議了,MIPI解碼難度之高,令無數(shù)英雄競折腰,以至于Xilinx官方不得不推出專用的IP核供開發(fā)者使用,不然太高端的操作直接嚇退一大批FPGA開發(fā)者,就沒人玩兒了。

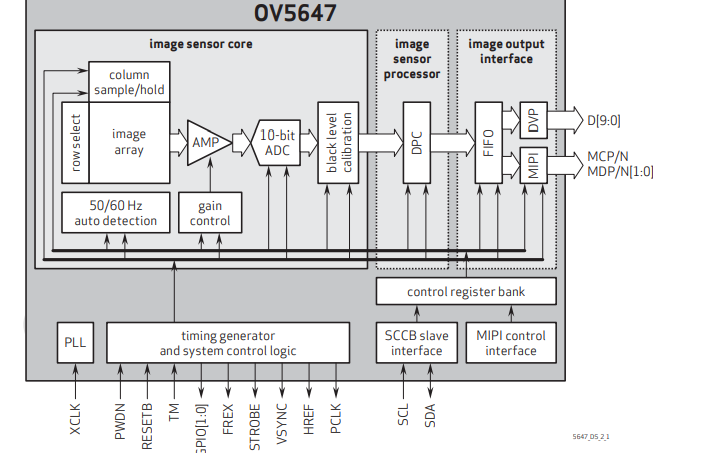

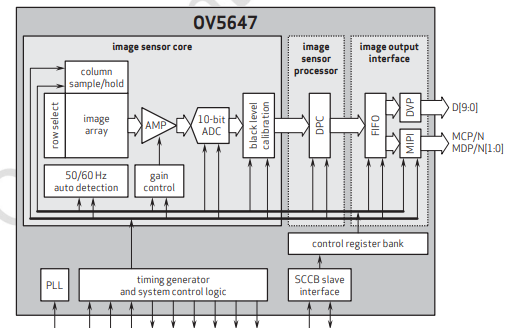

本設(shè)計(jì)基于Xilinx的Kintex7開發(fā)板,采集OV5647 攝像頭的720P 2Line MIPI視頻,OV5647 攝像頭引腳接Kintex7的 BANK16 LVDS_25 差分引腳,經(jīng)過純vhdl實(shí)現(xiàn)的 CSI2 RX模塊輸出AXIS視頻流,再將bayer數(shù)據(jù)轉(zhuǎn)RGB,再經(jīng)過FDMA將圖像送入DDR3中做三幀緩存后讀出,最后經(jīng)HDMI發(fā)送模塊輸出顯示器;

本文詳細(xì)描述了設(shè)計(jì)方案,工程代碼編譯通過后上板調(diào)試驗(yàn)證,可直接項(xiàng)目移植,適用于在校學(xué)生做畢業(yè)設(shè)計(jì)、研究生項(xiàng)目開發(fā),也適用于在職工程師做項(xiàng)目開發(fā),可應(yīng)用于醫(yī)療、軍工等行業(yè)的數(shù)字成像和圖像傳輸領(lǐng)域;

提供完整的、跑通的工程源碼和技術(shù)支持;

工程源碼和技術(shù)支持的獲取方式放在了文章末尾,請(qǐng)耐心看到最后;

關(guān)于MIPI協(xié)議,請(qǐng)自行搜索,csdn就有很多大佬講得很詳細(xì),我就不多寫這塊了;

2、Xilinx官方主推的MIPI解碼方案

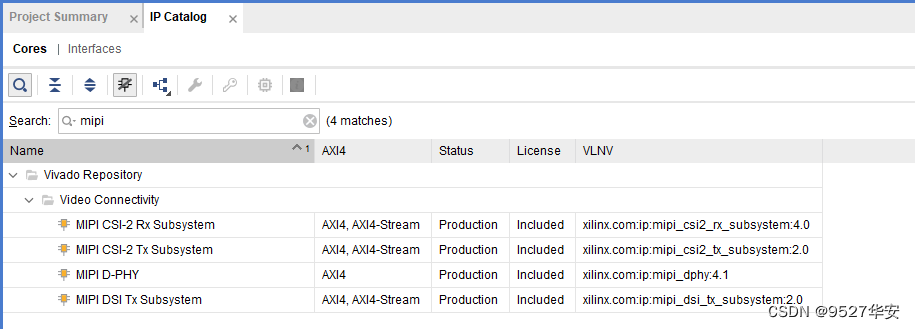

Xilinx官方主推的MIPI解碼方案是專用IP核,在vivado的ip倉庫里輸入MIPI就會(huì)看到如下的一堆IP:

Xilinx方案使用很簡單,調(diào)用IP就行,用SDK配置即可使用,MIPI解碼后的數(shù)據(jù)格式為AXIS,方便與他家的VDMA之類的IP對(duì)接,你無須關(guān)心復(fù)雜的MIPI協(xié)議即可暢玩兒MIPI,但問題就來了,如果你用的FPGA不是Xilinx家的怎么辦?

3、本 MIPI CSI2 模塊性能及其優(yōu)越性

本方案MIPI解碼后的視頻時(shí)序?yàn)閂GA時(shí)序,即行同步,場同步,數(shù)據(jù)有效,數(shù)據(jù)信號(hào);方便后端直接處理;解串部分使用Xilinx源語,本工程用到的是7系列源語,更高級(jí)別的FPGA應(yīng)用,需要更改源語參數(shù),但問題不大;

一個(gè)字:牛逼,表現(xiàn)如下:

1:純Vhdl代碼實(shí)現(xiàn),學(xué)習(xí)性和閱讀性達(dá)到天花板;

2:移植性還可以,只要兼容Xilinx解串源語的FPGA均可移植;

3:算法達(dá)到天花板,標(biāo)準(zhǔn)的CSI2接收協(xié)議實(shí)現(xiàn)解碼;

4:實(shí)用性達(dá)到天花板,采用OV4689攝像頭作為輸入,不同于市面上驗(yàn)證性和實(shí)驗(yàn)性的工程,本設(shè)計(jì)直接面向?qū)嵱霉こ蹋N近真實(shí)項(xiàng)目,MIPI輸入,2路視頻輸出,做類似項(xiàng)目的兄弟可直接拿去用,一個(gè)月工資直接拿到手。。。

5:支持高達(dá)4K分辨率的MIPI視頻解碼;

6:時(shí)序收斂很到位,考慮到MIPI協(xié)議的復(fù)雜性和時(shí)序的高要求,所以沒有采用時(shí)序收斂不強(qiáng)的verilog,而是VHDL,雖然閱讀性可能會(huì)低一些,但用戶只需要知道用戶接口即可,并不需要去看內(nèi)部的復(fù)雜代碼;

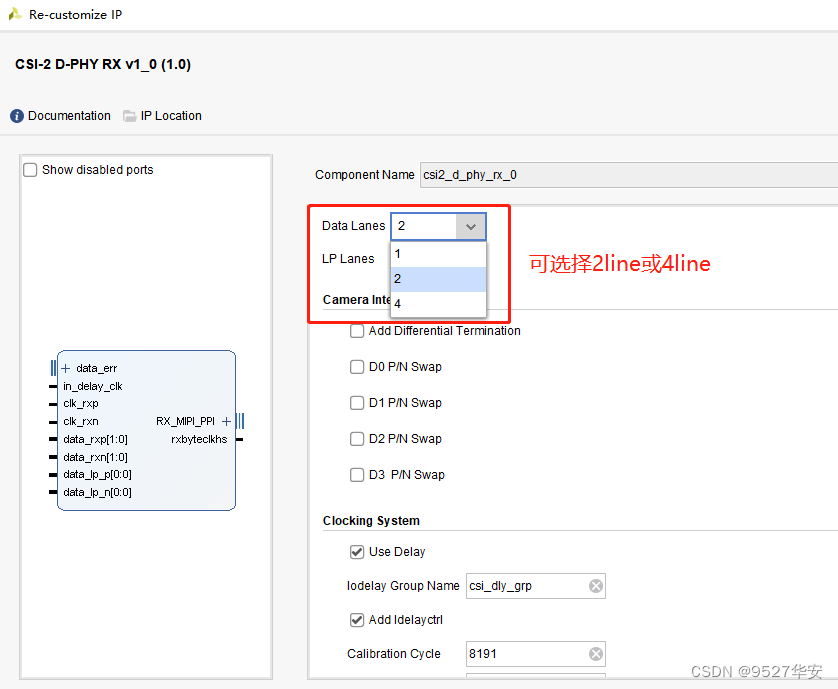

7:自定義IP封裝,方便Xilinx系列FPGA用戶使用,CSI-2自定義IP支持2line或4line輸入,可在IP配置界面手動(dòng)配置;

4、我這里已有的 MIPI 編解碼方案

我這里目前已有豐富的基于FPGA的MIPI編解碼方案,主要是MIPI解碼的,既有純vhdl實(shí)現(xiàn)的MIPI解碼,也有調(diào)用Xilinx官方IP實(shí)現(xiàn)的MIPI解碼,既有2line的MIPI解碼,也有4line的MIPI解碼,既有4K分辨率的MIPI解碼,也有小到720P分辨率的MIPI解碼,既有基于Xilinx平臺(tái)FPGA的MIPI解碼也有基于Altera平臺(tái)FPGA的MIPI解碼,還有基于Lattice平臺(tái)FPGA的MIPI解碼,后續(xù)還將繼續(xù)推出更過國產(chǎn)FPGA的MIPI解碼方案,畢竟目前國產(chǎn)化方案才是未來主流,后續(xù)也將推出更多MIPI編碼的DSI方案,努力將FPGA的MIPI編解碼方案做成白菜價(jià)。。。

5、詳細(xì)設(shè)計(jì)方案

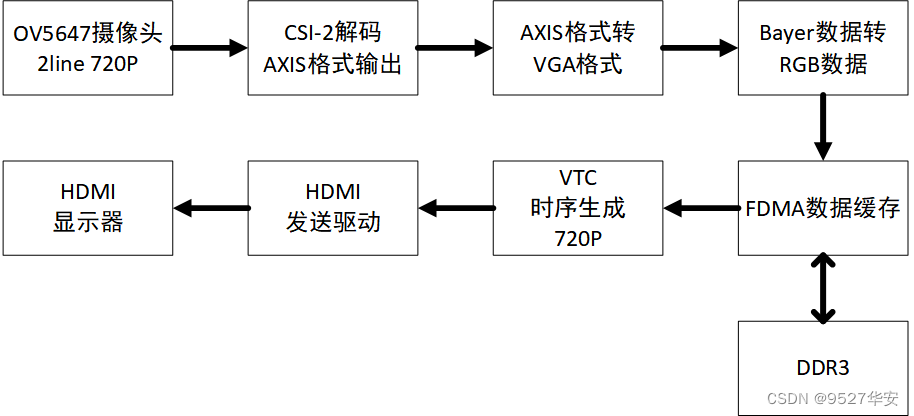

詳細(xì)設(shè)計(jì)方案如下:

視頻輸入:

OV5647攝像頭輸入,MIPI 2line,720P分辨率;

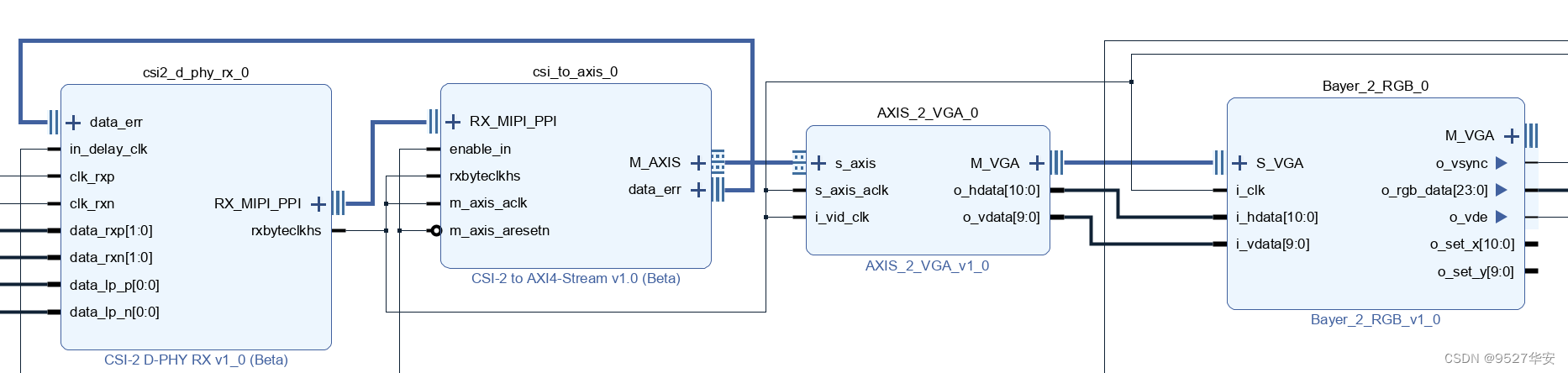

MIPI解碼:

純vhdl代碼編寫的CSI-2解碼器,可針對(duì)2line或4line輸入的MIPI視頻解碼,輸出為AXIS數(shù)據(jù)流,經(jīng)過AXIS轉(zhuǎn)VGA輸出VGA格式數(shù)據(jù),經(jīng)Bayer轉(zhuǎn)RGB輸出VGA格式的RGB888視頻數(shù)據(jù);

圖像輸出:

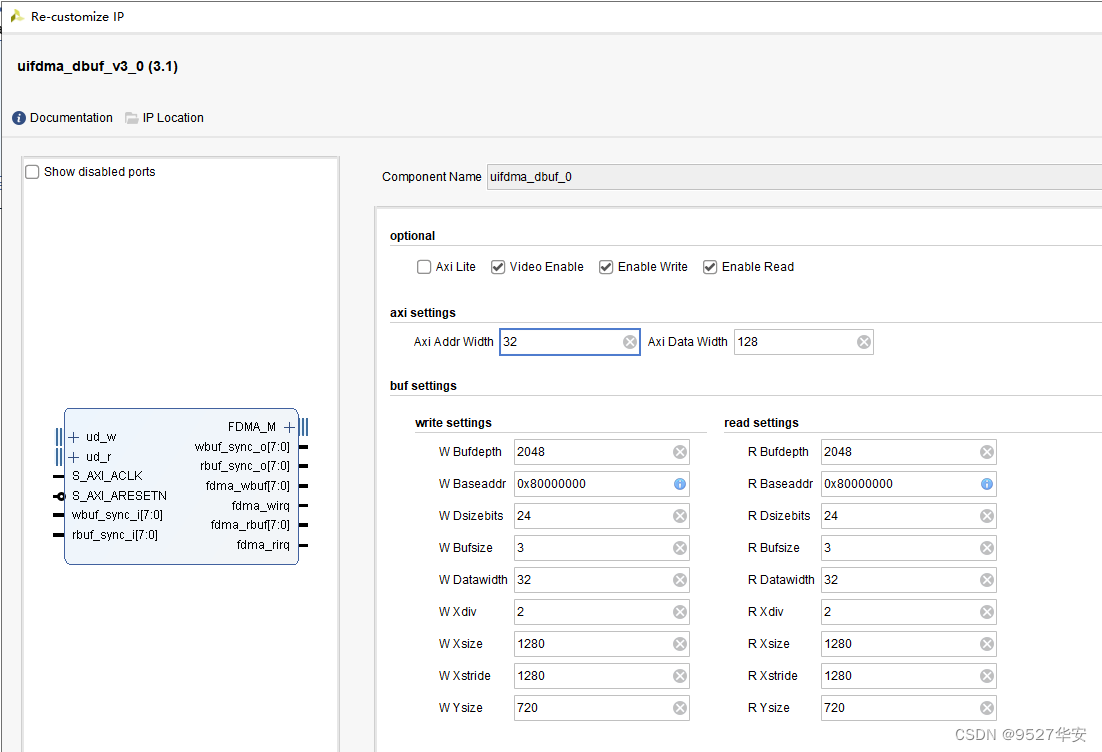

經(jīng)FDMA圖像3幀緩存后,相當(dāng)于MIPI視頻進(jìn)DDR3逛了一圈又回來了,經(jīng)過VGA時(shí)序發(fā)生器VTC和HDMI發(fā)送驅(qū)動(dòng)輸出顯示器,HDMI發(fā)送驅(qū)動(dòng)采用純verilog代碼編寫,不含任何IP,輸出穩(wěn)定可靠,我項(xiàng)目一直都在用

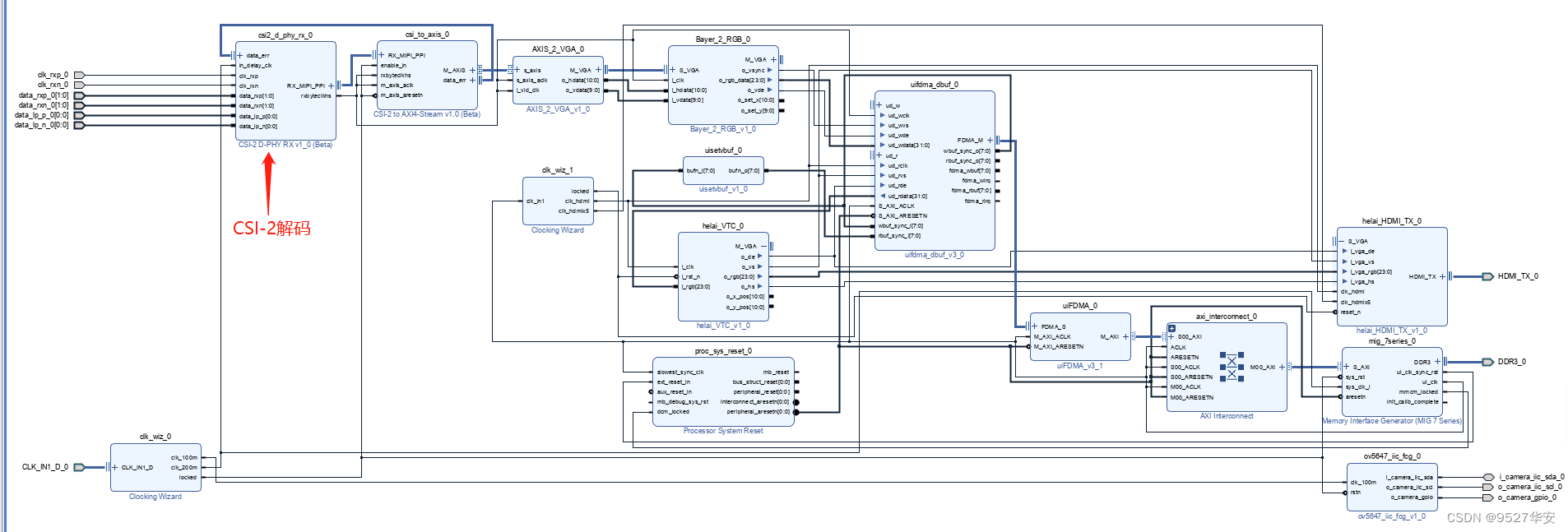

6、vivado工程介紹

開發(fā)板:Xilinx Kintex7開發(fā)板;

開發(fā)環(huán)境:vivado2020.2;

輸入:OV5647攝像頭輸入,MIPI 2line,720P分辨率;

輸出:HDMI,720P分辨率;

工程BD如下:

MIPI解碼部分的IP搭建如下:

CSI-2 IP配置界面如下:

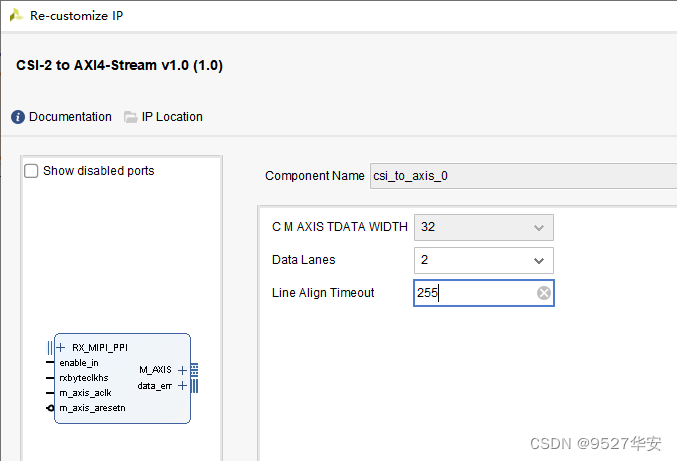

CSI-2轉(zhuǎn)AXIS

FDMA配置如下:

綜合后的工程代碼架構(gòu)如下:

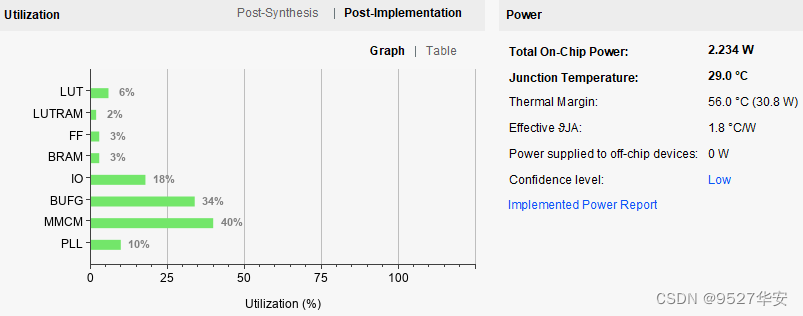

FPGA資源消耗和功耗預(yù)估如下:

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603005 -

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42243 -

攝像頭

+關(guān)注

關(guān)注

59文章

4836瀏覽量

95599 -

RGB

+關(guān)注

關(guān)注

4文章

798瀏覽量

58461 -

MIPI

+關(guān)注

關(guān)注

11文章

310瀏覽量

48613

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于RK3588J的6路MIPI CSI視頻采集案例分享,多路視頻系統(tǒng)必看!

[艾諾]無色塊10M碼流720P 推動(dòng)高清MP4標(biāo)準(zhǔn)

無色塊10M碼流720P 艾諾推動(dòng)高清MP4標(biāo)準(zhǔn)

無色塊10M碼流720P 推動(dòng)高清MP4標(biāo)準(zhǔn)

特權(quán)FPGA VIP視頻圖像開發(fā)套件例程詳解5——VGA SVGA 720p 1080p多分辨率顯示驅(qū)動(dòng)

RGB轉(zhuǎn)MIPI CSI芯片方案TC358746XBG

【小梅哥FPGA】OV5640攝像頭資料,含應(yīng)用手冊(cè),1280*720P分辨率,30幀應(yīng)用工程

關(guān)于dm8168 ezsdk下openmax decode_display例子輸出分辨率的問題。

請(qǐng)教DM6467關(guān)于1024x768分辨率的視頻處理

DM6467 720P H.264 編碼問題

怎么自動(dòng)識(shí)別視頻分辨率和幀頻?

OV5647傳感器的數(shù)據(jù)手冊(cè)

CMOS圖像傳感器OV5647的數(shù)據(jù)手冊(cè)免費(fèi)下載

AN-1337:ADI視頻解碼器與MIPI CSI-2接收器連接的設(shè)計(jì)考慮

FPGA解碼MIPI視頻OV5647 2line CSI2 720P分辨率采集

FPGA解碼MIPI視頻OV5647 2line CSI2 720P分辨率采集

評(píng)論