FPGA中的晶振大小多少比較合適?為什么會用到兩個晶振

FPGA (Field-Programmable Gate Array) 是一種可編程邏輯芯片,它可以根據用戶的需要重編程實現不同的功能。FPGA 的性能和功能主要由內部的晶振頻率決定。因此,在 FPGA 設計中,選擇合適的晶振非常重要。

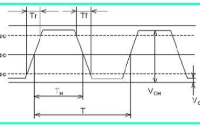

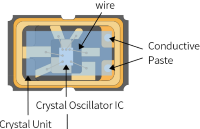

晶振的作用是為 FPGA 提供一個穩定的時鐘信號。FPGA 的內部邏輯由時鐘信號驅動,如果時鐘信號不穩定,就會導致 FPGA 內部邏輯錯誤,從而影響其性能和正確性。因此,選擇合適的晶振頻率至關重要。

晶振的大小與其頻率有關。一般來說,FPGA 需要的晶振頻率越高,晶振就越小,這是由于晶體振蕩器的電容和電感與頻率成反比例關系。比較常用的晶振頻率是 50MHz、100MHz、125MHz、150MHz、200MHz 等。選擇哪個頻率的晶振取決于應用程序的需求和 FPGA 的性能。

對于一些簡單應用場景,50MHz 的晶振已經足夠滿足要求。而對于一些高性能應用,需要使用更高頻率的晶振,比如 200MHz。對于一些需要精確計時的應用,需要選擇更精準的晶振,并使用 PLL (Phase-Locked Loop) 進行校準。

在某些情況下,可能需要使用兩個晶振。一個晶振用于 FPGA 的時鐘,另一個晶振用于與 FPGA 進行通信的接口芯片的時鐘。這是因為,接口芯片的時鐘可能與 FPGA 不同步,如果共用一個晶振可能會導致通信錯誤。

總之,選擇合適的晶振頻率和數量,是 FPGA 設計中非常重要的一環。需要綜合考慮應用場景、性能要求、計時精度等因素。

-

FPGA

+關注

關注

1643文章

21950瀏覽量

613743 -

晶振

+關注

關注

34文章

3188瀏覽量

69495

發布評論請先 登錄

晶振串聯電阻大小的影響

愛普生汽車晶振,汽車級晶振規格選型應用

評論