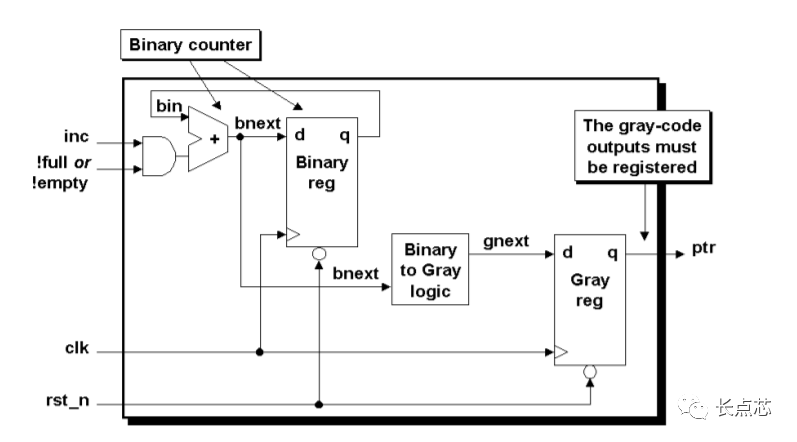

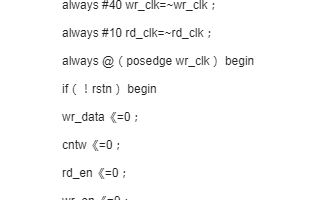

設計者為了提升FIFO的速度使用了將二進制計數器和格雷碼計數器結合在一起的方法,從最開始用一組寄存器來進行格雷碼到二進制碼的轉換,二進制碼的遞增和二進制碼到格雷碼的轉換,到后來的style#2(如圖)。

在本篇當中,作者進一步對此設計進行了說明,使用這種格雷碼計數器的目的是利用了二進制數進位的機制簡化了格雷碼到二進制碼的轉換電路來減少組合邏輯電路,這樣整個計數器的工作頻率上限就會有所提升。

Dual n-bit Gray Code counter style#2

但是,可以看到這里的設計需要使用兩組寄存器,這里可能會體現到PPA trade-off的思想了(因為我也沒有實驗過這種替換方式會不會帶來更大的面積損耗)。不過,對FPGA來講,FPGA包含著許多寄存器資源,所以使用FPGA來實現這種設計方法就不需要考慮面積上的損耗,更能凸顯出速度提升上的優勢!

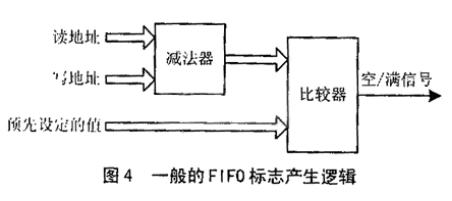

上文說到,設計FIFO中最重要的部分也是最難的部分之一就是如何產生空滿標志信號。一種方法就是上一篇提到的使用發送到對面時鐘域的同步后的格雷碼指針來進行比較,從而判斷空滿信號的產生。而另外一種方法就是本篇文章所提到的,指針的比較不再是同步的了,而是通過“異步”比較,并判斷空滿信號。

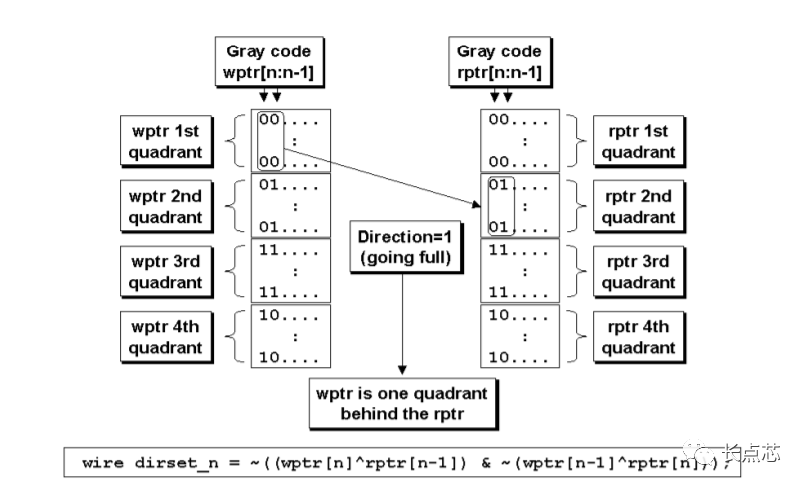

上篇文章提到的判斷空滿信號的方法是比較指針是否一樣,并通過多增加一個bit位來討論指針被套圈的問題。不同于上個設計,本篇文章提出了一個更有創意的思路來判斷空滿信號的產生。

作者將FIFO的地址分成了四個區間并通過編碼兩個指針計數器最高的兩位來比較判斷FIFO將要空滿的 趨勢 。舉個栗子,如果寫指針落在讀指針后面一個區間則表示FIFO將要滿,然后當指針重合時則將direction寄存器置位,如下圖。

FIFO is going full because the wptr trails the rptr by one quadrant

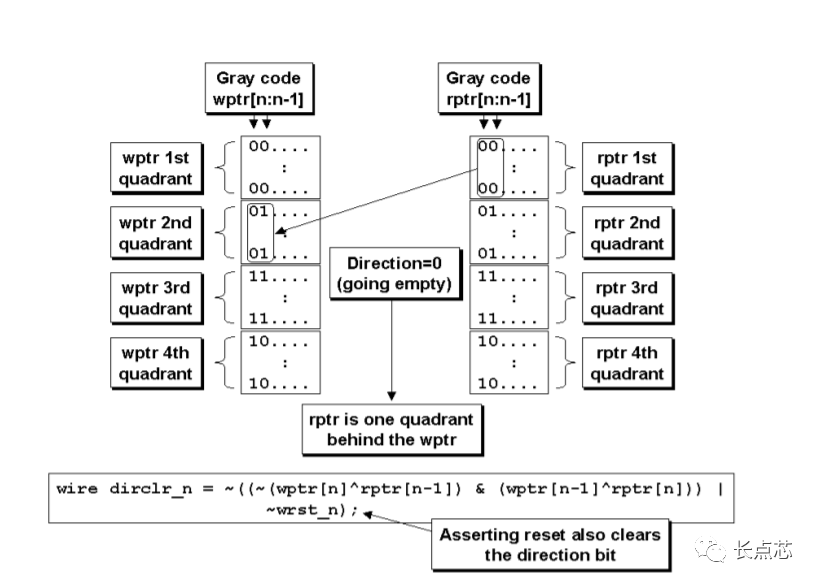

而如果寫指針落在讀指針前面一個區間則代表FIFO將要空,然后當指針重合的時候則將direction寄存器復位。

FIFO is going empty because the rptr trails the wptr by one quadrant

結語:

這篇文章理解起來可能要比前一篇更難理解一點,給我的感覺就是看起來很暈。沒有把握給大家闡明清楚,所以就不再做更深入的探討了。還是推薦大家如果對這個設計方法感興趣的話可以讀一下原文。

-

編碼器

+關注

關注

45文章

3639瀏覽量

134429 -

寄存器

+關注

關注

31文章

5336瀏覽量

120235 -

二進制

+關注

關注

2文章

795瀏覽量

41643 -

FIFO存儲

+關注

關注

0文章

103瀏覽量

5969 -

組合邏輯電路

+關注

關注

6文章

70瀏覽量

14649

發布評論請先 登錄

相關推薦

用FPGA芯片實現高速異步FIFO的一種方法

異步FIFO結構及FPGA設計

一種異步FIFO的設計方法

異步FIFO結構及FPGA設計

基于FPGA的異步FIFO設計方法詳解

基于異步FIFO結構原理

關于一種面向異步FIFO的低開銷容錯機制研究

一種基于FPGA內部存儲器的適合音頻解嵌的高效異步FIFO設計

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用

同步FIFO和異步FIFO區別介紹

關于另外一種設計異步FIFO的簡介

關于另外一種設計異步FIFO的簡介

評論