關鍵要點

為什么IC設計需要從兩個不同的方向入手。

了解準備IC設計文件的過程。

成本和收益問題限制了IC的物理設計。

密集晶體管數硅晶片始于一系列IC設計步驟。

盡管晶體管的推出相對較晚,但它是人類歷史上生產最多的產品。除非出現完全不可預見的技術突破,否則這種情況不太可能改變;自推出以來的幾十年里,器件晶體管的數量呈指數級增長,而小型化制造奇跡是數字革命的核心。然而,晶體管數量增加的趨勢正在突破設計和制造工藝的極限。IC設計構建了一個迭代過程,將對細節的關注與對設備特性和功能的高層次、系統的包含結合起來。

迭代和雙向設計動機

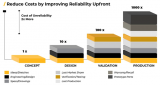

IC設計步驟類似于PCB設計,但由于更多的約束和更嚴格的公差而產生差異。超大規模集成電路(VLSI)指導IC設計,將數十億MOSFET組合到一個芯片中,實現密集的電子功能,如片上系統(SoC)。與PCB設計類似,VLSI設計流程是一個迭代過程,但需要注意的是,物理制造過程中的迭代比小批量原型要昂貴得多。而且,與PCB設計不同的是芯片在制造后缺乏用戶可維護性——它是一種二進制的,不是成功就是失敗。

IC設計的迭代性質源于自上而下和自下而上的設計風格的組合:

自上而下的設計是逆向工程意義上的分解。設計團隊制定好的系統框架,然后在設計過程中為子系統添加細節。

自下而上的設計是先構建子系統,然后再將各個子系統合并到系統中。

雖然大部分IC設計側重于自下而上的方法,因為它允許最精細的細節來塑造更高水平的設計復雜性,但自上而下的方法可以幫助利用自下而上的設計來改善性能結果。例如,尺寸是IC的兩個主要設計約束之一,在沒有準確估計芯片面積的情況下實施自上而下的架構設計可能會超出分配的空間。相反,IC設計應盡早集成物理約束,以構建具有互補特性的器件功能。最好的設計綜合了自下而上的復雜性和對自上而下方法的約束:

概念設計-IC的規格。與所有工程一樣,IC特性將有合理的權衡,以符合設計意圖。然而,IC布局將允許在這些限制范圍內有很大的自由度,允許設計者選擇最合適的拓撲結構和布局

原理圖設計和仿真 -IC的組件需要互連定義。網表必須完整描述與電源、接地和外部 I/O 引腳的連接。為了正確實現原理圖,設計團隊必須創建表示元件分組的符號,稱為電路模塊。除了布局之外,這些模塊也是設計仿真階段不可或缺的一部分。仿真階段是有雙重意義的:設計驗證和優化性能。

布局和驗證 -布局可以增強或抑制關鍵性能,主要是IC的功率、尺寸和運行速度。此外,精心的布局會抵消寄生電阻和電容的影響。然后,布局將使用可配置的DFM約束執行設計規則檢查(DRC),以檢測設計的IC與制造要求之間的沖突。

布局后仿真 -在確定布局和原理圖之間不存在差異后,此階段將是原理圖級仿真的改進版本。它是一種更強大的仿真,可將寄生效應和信號延遲參數納入評估中,從而準確模擬實際性能。仿真后的結果提供了有關布局的反饋,相關的設計規范可能需要進一步修訂。

物理 IC 設計步驟的細節

完整的設計和制造的IC之間仍然存在著巨大的差距。制造工具和技術將要求遵守最小特征尺寸和間距規則。可制造性保證將取決于迭代和先前IC設計步驟的質量:

平面規劃 -放置數十億個單獨的晶體管是不可行的;相反,晶體管被劃分在功能模塊中,然后遞歸地定義為更小的子塊。平面圖必須最好地將這些塊分組,以最小化面積并方便布線。

布局-這個階段涉及到塊在芯片上的精確定位。第一個放置將是評估步驟之前的單元的粗略排列,旨在優化空間,同時遵守設計限制。對布線空間的估計可指導放置是否需要繼續迭代。

第一次布局將是在評估步驟之前對單元進行粗略布置,評估步驟旨在優化空間,同時遵守設計要求限制。對布線空間的估計可指導布局是否需要繼續迭代。

布線-塊之間的空間為布線保留空間,布線過程跨越兩個階段。布線必須保留空間,并通過在引腳之間占用盡可能短的路徑來最小化寄生效應的影響。首先,全局布線在金屬層之間以交替的首選方向組織連接。詳細布線如下,其中指定了這些連接的幾何形狀。

萃取-物理布局轉化為網表,以實現包含精確細節的最精確仿真水平。必須對電氣參數進行最終檢查,以確定信號延遲和時序。

布線——塊之間的空間為互連預留了空間,連接過程分為兩個階段。布線必須保留空間,并通過占據引腳之間盡可能短的距離來最小化寄生效應的影響。首先,全局布線以交替的優先方向在金屬層之間組織連接。接下來是詳細的布線,它指定了這些連接的幾何形狀。

導出-物理布局轉化為網表,以進行最精確的仿真,其中包含精確的細節。為了建立信號延遲和時序,需要對電氣參數進行最終檢查。

使用Cadence解決方案逐步進行IC設計

IC設計步驟需要嚴格控制和精確度,以將密集的晶體管制造納入現代封裝中。然而,IC設計在概念上與PCB設計中的過程相差無幾,這并不奇怪,因為IC實際上就是一塊微型化的PCB。電路板或元器件需要復雜的工具集和最先進的建模,以不斷實現設計突破的性能。

結論

Cadence Allegro PCB Designer是一個綜合的PCB設計和分析工具,可涵蓋設計流程的各個方面,包括原理圖設計、布局、布線、分析等。這樣可以大大提高工作效率,減少數據傳遞和轉換過程中的錯誤和不一致性。

Cadence Allegro PCB Designer提供了一系列強大的分析工具,包括信號完整性分析、電源完整性分析、射頻噪聲分析等。這些工具可以幫助您識別和解決設計中可能存在的噪聲問題,優化電路性能。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

IC

+關注

關注

36文章

5953瀏覽量

175656 -

IC設計

+關注

關注

38文章

1297瀏覽量

103987 -

DFM

+關注

關注

8文章

464瀏覽量

28216

發布評論請先 登錄

相關推薦

AmpereOne如何滿足現代數據中心需求

在當今要求苛刻的技術環境中,數據中心和企業面臨著嚴峻的挑戰。不斷上升的能源成本促使公司尋求更節能的解決方案,以滿足可持續性和成本目標。對可擴展計算密度的需求也在增長,以跟上日益復雜的應用程序和云原生

【華秋DFM】V4.4新版發布:以用戶需求為核心,持續優化設計與制造體驗

衷心感謝每一位新老用戶對華秋DFM軟件的支持與陪伴!正是有了大家寶貴的反饋和持續的信任,我們才能不斷進步,為大家提供更加優質的服務,大家的支持是我們前進的重要動力。

經過一個半月的不懈努力與精心打磨

發表于 11-20 22:22

MySQL還能跟上PostgreSQL的步伐嗎

Can MySQL Catch Up with PostgreSQL’s Momentum?[2] 譯者:馮若航[3],Vonng,Pigsty[4]?作者,PostgreSQL 大法師,數據庫老司機,云計算泥石流。 MySQL還能跟上PostgreSQL的步伐嗎

DFM在實際應用中的關鍵考慮和策略

一站式PCBA智造廠家今天為大家講講DFM對SMT貼片加工有什么影響?DFM對SMT貼片加工的重要性。在電子制造領域,SMT(Surface Mount Technology,表面貼裝技術)貼片加工

華秋DFM軟件再升級,熱門功能搶先體驗

在快速迭代的電子設計領域,每一處細節都可能成為決定產品成敗的關鍵。

因此華秋DFM團隊始終堅持不懈地 優化軟件的服務、升級功能的應用 ,全面支持電子產品研發流程中的多元角色,尤其 聚焦于硬件

發表于 09-11 20:23

在 KiCad 中使用華秋 DFM 插件

“在 KiCad 中使用華秋DFM插件,高效完成工藝規則檢查,且可以根據檢測結果直接在 PCB 中進行修改。”

華秋 DFM 插件介紹

DFM 插件可以幫助您在 KiCad 的 PCB 中一

發表于 08-18 22:15

精益求精:DFM助力產品設計升級

DFM的核心原則詳解簡化設計你的目標是設計零部件,使其能夠順利地裝配在一起。盡量減少復雜或手動組裝步驟的數量。確保它們易于對齊、緊固和連接。這減少了組裝過程中出錯的機會。減少零件數量:例如,將多個

華秋DFM新版本 #持續優化 #服務升級

親愛的各位工程師們,首先感謝大家一直以來對華秋DFM軟件的不離不棄與寶貴支持!大家的每一份關注都是我們 前進的動力 。

近幾個月,大家可能都注意到我們的版本 更新比較頻繁 ,這是因為我們正緊

發表于 07-04 18:44

熱詞解析| 制造企業如何跟上新質生產力建設步伐

回顧3月份的網絡熱詞,「新質生產力」在各大平臺霸榜刷屏,并且受到兩會政府工作報告的頻繁聚焦。究竟何為新質生產力?以及,傳統制造企業如何加速融入這場火熱的現代化產業革新浪潮之中?

什么是DFM?DFM檢查在SMT貼片加工生產中的重要性

現在越來越多的smt貼片廠都引進了DFM可制造性設計服務了,這是因為在SMT貼片加工生產前進行可制造性設計(DFM)能夠有效的控制生產成本。

華秋SMT優惠再升級!攜手DFM智能分析,助力高效生產無隱患

訂單、SMT+PCB+IC訂單● 不可參與訂單類型:純SMT訂單、SMT+IC訂單福利二:除原5折SMT貼片外新增8折貼片且不限物料種類● 5折SMT活動:物料種類大于50,無訂單類型要求● 8折SMT

發表于 03-19 18:22

IC設計步驟:跟上現代DFM的步伐

IC設計步驟:跟上現代DFM的步伐

評論