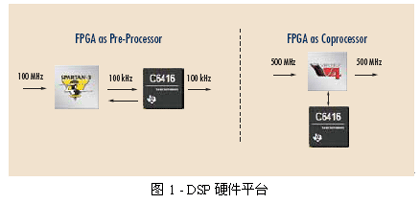

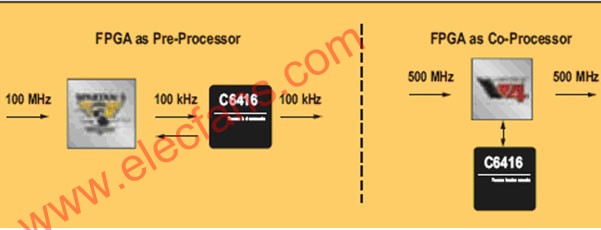

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。

盡管優勢如此明顯,但習慣于使用基于處理器的系統進行設計的團隊,仍會避免使用FPGA,因為他們缺乏必要的硬件技能,來將FPGA用作協處理器(圖1)。不熟悉像VHDL和Verilog這樣傳統的硬件設計方法,限制或阻止了FPGA的使用,這通常會導致設計成本過高,且功耗過大。ESL,一套全新推出的設計工具,能夠解決這一設計難題。它在保留常規軟硬件設計方式的同時,幫助基于處理器的設計者使用可編程邏輯加速自己的設計。

借助FPGA協處理提升性能

設計人員能夠利用由FPGA架構的并行性所帶來的使用靈活的特點,大幅提升DSP系統的性能。通常的設計示例包括(并不局限于)FIR濾波、FFT、數字下變頻和前向糾錯(FEC)模塊等。

Xilinx? VirtexTM-4和Virtex-5架構提供了多達512個并行乘法器,它們能夠以超過500MHz的速度運行,提供256GMAC的DSP峰值性能。通過在FPGA上實現高速并行處理,而在DSP上實現高速串行處理,可以使整個DSP系統的性能得到優化,同時降低系統的功率需求。

借助FPGA嵌入式處理降低成本

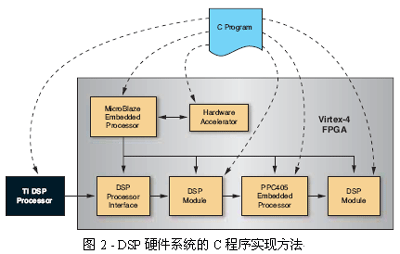

帶有FPGA協處理器的DSP硬件系統,為C算法范疇之內的運算(例如DSP處理器、FPGA可配置邏輯塊(CLB)和FPGA嵌入式處理器之間的算法劃分)提供了許多實現方法。Virtex-4器件提供了兩種嵌入式處理器——通常被用作系統控制的MicroBlazeTM軟核處理器和性能更高的PowerPCTM硬核處理器。由FPGA架構實現的并行操作,能夠被直接用于DSP的數據路徑,或被配置為一個嵌入式處理器的硬件加速器。

設計者所面對的挑戰是如何在所提供的硬件資源之間劃分DSP的系統操作,才能做到最為有效和最節省成本。使用FPGA嵌入式處理器的最大好處并不總是顯而易見的,但這一硬件資源的確能夠極大地降低系統的整體成本。FPGA嵌入式處理器提供了這樣一個機會:將所有非關鍵性操作集中于嵌入式處理器上所運行的軟件,從而最大限度降低系統所需硬件資源的總量。

C程序到系統門

在FPGA的應用中,術語“C程序到系統門”特指如下兩種實現方法之一——在FPGA架構上直接實現一個DSP模塊或為MicroBlaze或PowerPC 405嵌入式處理器創建一個硬件加速器(圖2)。

當操作直接在DSP數據路徑中進行時,將FPGA作為一個DSP模塊來實現操作,能夠獲得最高的性能。這一方法先將C代碼直接綜合成RTL代碼,然后在DSP的數據通路中對模塊進行實體化。你可以使用傳統的HDL設計方法,或通過像Xilinx System Generator for DSP這樣的系統工具,來進行實體化。這種直接實體化方式,能夠讓開發人員以最小的開銷達到最高的性能。

主流的C綜合工具可實現的性能,能夠與手寫RTL相媲美——但要做到這一點,需要對C綜合工具的工作原理和代碼風格有詳盡的了解。為了達到所要求的性能,通常需要對代碼進行修改,并且添加內聯綜合指令,以插入并行和流水線級。雖然要進行這些改進,但是設計效率還是能夠大大提高。C系統模型仍然是驅動設計流程的主要因素。

作為一種替代方案,為Xilinx嵌入式處理器創建一個硬件加速器通常是一個更為簡單的方法。在該方法中,仍然主要使用處理器來運行C程序,只是將對性能有重大影響的操作以硬件加速器的形式放置到FPGA邏輯中執行。這是一種更偏向于以軟件為中心的設計方法。然而,這一方法會犧牲一些性能。與DSP模塊的方法相似,C程序被綜合成RTL代碼,所不同的是頂層實體被接口邏輯包圍,以便能與Xilinx嵌入式處理器的總線相連。這就創建了一個硬件加速器,它能夠被調入到Xilinx EDK環境中,并且被軟件友好的C程序調用。

對將C程序映射到硬件加速器的性能要求,通常不是那么苛刻。這里的目標是使性能比使用純軟件實現的方法得到提高,同時保持軟件友好的設計流程。雖然仍有編碼技術和內聯綜合指令,但通常可以不使用它們就達到所要求的性能提升。

設計方法——采用FPGA協處理的障礙

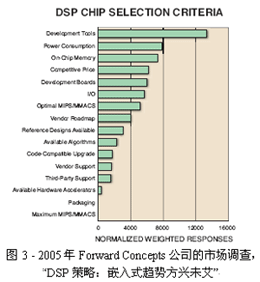

正確劃分和實現一個復雜DSP系統,需要花費大量時間和精力掌握所需的技能。Forward Concepts市場調查公司為了確定在DSP設計中選用FPGA最重要的標準,開展了一項調查。調查的結果表明開發工具是最重要的選擇標準,如圖3所示。

調查結果顯示,使用FPGA協處理器實現DSP硬件系統的優勢,已經得到用戶的充分認可,但對于傳統的DSP設計者來說,開發工具現有的狀況,成為他們采用這一設計方法的障礙。

Xilinx ESL計劃

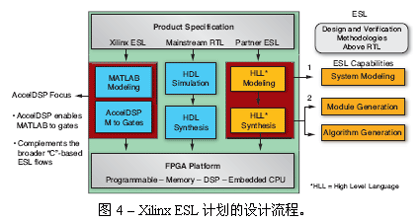

ESL設計工具將數字設計的抽象度在RTL的基礎上又提高了一步。其中部分工具專門用來將由C/C++開發的系統模型映射到包含FPGA和DSP處理器的DSP系統中。此舉的目的是使硬件平臺對軟件設計者變得透明(圖4)。

今年,為了全面解決上述障礙,Xilinx公司和主要的ESL工具廠商攜手啟動了一個被稱為ESL計劃的合作項目。這一合作計劃的主要目標是賦予設計者軟件編程的能力,使他們能夠在可編程硬件中輕松地實現自己的想法,而無需學習傳統的硬件設計技巧。該計劃融合了ESL成員機構的創新,能夠加速產品開發進程,推動設計人員采用世界上最先進的設計方法。

結論

將Xilinx ESL合作伙伴的工具結合在一起,能夠提供廣泛的互補性解決方案,這些解決方案已針對一系列產品、平臺和最終用戶進行了優化。Xilinx公司也在集中力量研究互補技術。例如,AccelDSP綜合為在浮點MATLAB中開發的算法提供了硬件實現的方法,而Xilinx System Generator for DSP使得用ESL設計開發的模塊,能夠輕松地與Xilinx IP和嵌入式處理器結合起來。借助多個極富創新精神的合作伙伴的工作,是實現程序員期望的FPGA設計流程最快捷的途徑。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602998 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121304 -

Verilog

+關注

關注

28文章

1351瀏覽量

110074 -

C語言

+關注

關注

180文章

7604瀏覽量

136692 -

vhdl

+關注

關注

30文章

817瀏覽量

128119

原文標題:FPGA協處理的優勢有哪些?如何去使用FPGA協處理?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【FPGA干貨分享六】基于FPGA協處理器的算法加速的實現

采用FPGA的協處理器來簡化ASIC仿真

簡述協處理器發展歷程及前景展望

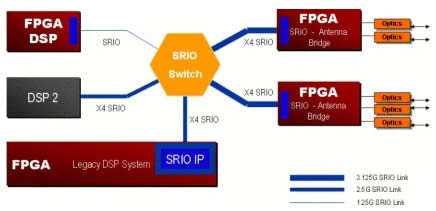

利用串行RapidIO實現FPGA協處理

利用串行RapidIO實現FPGA協處理

FPGA協處理技術介紹及進展

采用FPGA協處理的無線子系統

FPGA協處理的優勢有哪些?如何去使用FPGA協處理?

FPGA協處理的優勢有哪些?如何去使用FPGA協處理?

評論