SPI總線概述

1 基本概念

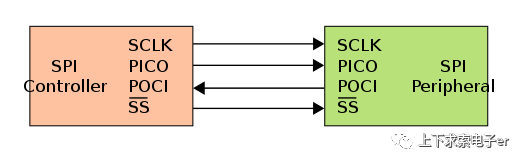

串行外設(shè)接口(Serial Peripheral Interface)的簡稱也叫做SPI,是一種高速、全雙工同步通信的一種接口,串行外設(shè)接口一般是需要4根線來進行通信(NSS、MISO、MOSI、SCK),但是如果打算實現(xiàn)單向通信也可以只使用3根線(NSS、MISO/MOSI、SCK),就可以利用這種機制實現(xiàn)一對多或者一對一的通信。

2 引腳定義

通常SPI通過4個引腳與外部器件相連:

- MISO (Master Input Slave Output):主設(shè)備輸入/從設(shè)備輸出引腳 。該引腳在從模式下發(fā)送數(shù)據(jù),在主模式下接收數(shù)據(jù)。

- MOSI (Master Output Slave Input):主設(shè)備輸出/從設(shè)備輸入引腳。 該引腳在主模式下發(fā)送數(shù)據(jù),在從模式下接收數(shù)據(jù)。

- SCK (Serial Clock):串行時鐘 ,作為主設(shè)備的輸出,從設(shè)備的輸入.

- NSS (Negative Slave Select):低電平有效的從器件選擇。 這是一個可選的引腳,用來選擇主/從設(shè)備。它的功能是用來作為“片選引腳”,讓主設(shè)備可以單獨地與特定從設(shè)備通訊,避免數(shù)據(jù)線上的沖突。

SPI總線:單一主機對單一從機

SPI總線:單一主機對復合從機

SPI總線采用的 環(huán)形結(jié)構(gòu) ,利用的是主從模式(主機→從機)進行數(shù)據(jù)的傳輸,由于是同步通信,所以在主機發(fā)送數(shù)據(jù)的同時也會收到從機發(fā)送的數(shù)據(jù)。

MOSI腳相互連接,MISO腳相互連接。這樣,數(shù)據(jù)在主和從之間串行地傳輸(MSB位在)。通信總是由主設(shè)備發(fā)起。主設(shè)備通過MOSI腳把數(shù)據(jù)發(fā)送給從設(shè)備,從設(shè)備通過MISO引腳回傳數(shù)據(jù)。這意味全雙工通信的數(shù)據(jù)輸出和數(shù)據(jù)輸入是用同一個時鐘信號同步的;時鐘信號由主設(shè)備通過SCK腳提供。

NSS的說明:主機的NSS引腳在空閑狀態(tài)下應(yīng)處于高電平(VDD),主機發(fā)送數(shù)據(jù)時,主機的NSS應(yīng)為輸出模式,從機的NSS為輸入模式,當主機的NSS引腳拉低,從設(shè)備的NSS引腳可以檢測到低電平,該設(shè)備被選中。

從SPI的結(jié)構(gòu)框圖中可以看到NSS也是外部引腳的名稱,其實控制SPI收發(fā)數(shù)據(jù)是通過內(nèi)部的NSS信號實現(xiàn)的,而這個內(nèi)部的NSS信號源可以由SPI_CR1寄存器的SSM(Software slave management)位來配置。

- 軟件NSS模式,SSM=1 :可以通過設(shè)置SPI_CR1寄存器的SSM位來使能這種模式。在這種模式下NSS引腳可以用作它用,而內(nèi)部NSS信號電平可以通過寫SPI_CR1的SSI位來驅(qū)動。

SSM :軟件從設(shè)備管理。當SSM被置位時,NSS引腳上的電平由SSI位的值決定。

0:禁止軟件從設(shè)備管理;

1:啟用軟件從設(shè)備管理。 - 硬件NSS模式,SSM=0:內(nèi)部NSS信號電平由NSS引腳電平?jīng)Q定。在這種“硬件模式”下要用SPI_CR2的SSOE(Software Save Output Enable)位來控制NSS作為輸入還是輸出,當SSOE=0時,NSS引腳被配置為輸入;當SSOE=0時,NSS引腳被配置為輸出。

3 工作模式

注意:由于SPI外設(shè)是 全雙工同步通信 ,所以時鐘信號就由SCK引腳來生成, SCK引腳只能由主設(shè)備控制,從設(shè)備是無法控制的 ,所以SCK引腳輸出的脈沖信號的極性和相位就需要進行配置。

3.1 時鐘信號的相位和極性

SPI_CR寄存器的CPOL(時鐘極性位)和CPHA(時鐘相位位),能夠組合成四種可能的時序關(guān)系。

- 時鐘極性CPOL :指的是在SPI總線空閑狀態(tài)下(不傳輸任何數(shù)據(jù))SCK引腳的默認的電平狀態(tài)。SCK空閑狀態(tài)下的電平可以由SPI_CR1寄存器的CPOL位來進行設(shè)置。主設(shè)備的時鐘極性要根據(jù)從設(shè)備來設(shè)置。

- 如果CPOL被清‘0’,SCK引腳在空閑狀態(tài)保持低電平;

- 如果CPOL被置’1’,SCK引腳在空閑狀態(tài)保持高電平。

- 時鐘相位CPHA :指的是在傳輸數(shù)據(jù)時選擇脈沖信號的邊沿(上升沿或者下降沿)來進行數(shù)據(jù)的采集或者修改。該位可以由SPI_CR1寄存器的CPHA位來進行設(shè)置。主設(shè)備的時鐘相位要根據(jù)從設(shè)備來設(shè)置。

- 如果CPHA位被置’1’,SCK時鐘的第二個邊沿(CPOL位為0時就是下降沿,CPOL位為’1’時就是上升沿)進行數(shù)據(jù)位的采樣,數(shù)據(jù)在第二個時鐘邊沿被鎖存。

- 如果CPHA位被清’0’,SCK時鐘的第一邊沿(CPOL位為’0’時就是下降沿,CPOL位為’1’時就是上升沿)進行數(shù)據(jù)位采樣,數(shù)據(jù)在第一個時鐘邊沿被鎖存。

| CPOL | CPHA | 模式說明 |

|---|---|---|

| 0 | 0 | 該模式指的是SCK引腳在空閑狀態(tài)下為低電平,并且在第一個時鐘邊沿(上升沿)采集數(shù)據(jù),在第二個時鐘邊沿(下降沿)來修改數(shù)據(jù)。 |

| 0 | 1 | 該模式指的是SCK引腳在空閑狀態(tài)下為低電平,并且在第二個時鐘邊沿(下降沿)采集數(shù)據(jù),在第一個時鐘邊沿(上升沿)來修改數(shù)據(jù)。 |

| 1 | 0 | 該模式指的是SCK引腳在空閑狀態(tài)下為高電平,并且在第一個時鐘邊沿(下降沿)采集數(shù)據(jù),在第二個時鐘邊沿(上升沿)來修改數(shù)據(jù)。 |

| 1 | 1 | 該模式指的是SCK引腳在空閑狀態(tài)下為高電平,并且在第二個時鐘邊沿(上升沿)采集數(shù)據(jù),在第一個時鐘邊沿(下降沿)來修改數(shù)據(jù)。 |

通過這兩位可以得到四種不同的組合,就被作為SPI總線的工作模式( 模式0~模式3 ),到底要選擇哪種模式,主機的工作模式必須根據(jù)從設(shè)備的數(shù)據(jù)手冊的說明進行設(shè)置。

在實際的開發(fā)過程中,使用最多是模式0和 模式3 ,比如2.4G無線通信模塊NRF24L01采用模式0來通信。

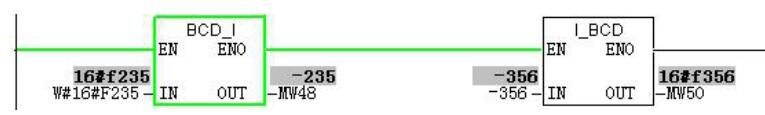

3.2 數(shù)據(jù)幀格式

- 根據(jù)SPI_CR1寄存器中的LSBFIRST位,輸出數(shù)據(jù)位時可以MSB(高位先出)在先也可以LSB(低位先出)在先。主機的數(shù)據(jù)格式必須要根據(jù)從機的數(shù)據(jù)格式進行設(shè)置。

- 根據(jù)SPI_CR1寄存器的DFF位,每個數(shù)據(jù)幀可以是8位或是16位。所選擇的數(shù)據(jù)幀格式對發(fā)送和/或接收都有效。

DFF :數(shù)據(jù)幀格式 (Data frame format)

- 0:使用8位數(shù)據(jù)幀格式進行發(fā)送/接收;

- 1:使用16位數(shù)據(jù)幀格式進行發(fā)送/接收。

注:只有當SPI禁止(SPE=0)時,才能寫該位,否則出錯

LSBFIRST :幀格式 (Frame format)

- 0:先發(fā)送MSB;

- 1:先發(fā)送LSB。

注:當通信在進行時不能改變該位的值。

4 通信速率

5 使用流程

The SPI HAL driver can be used as follows:

(#) **Declare a SPI_HandleTypeDef handle structure**, for example:

`SPI_HandleTypeDef hspi`;

(#)**Initialize the SPI low level resources** by implementing the `HAL_SPI_MspInit()` API:

(##) **Enable the SPIx interface clock**

(##) **SPI pins configuration**

(+++) Enable the clock for the SPI GPIOs

(+++) Configure these SPI pins as alternate function push-pull

(##) **NVIC configuration if you need to use interrupt process**

(+++) Configure the SPIx interrupt priority

(+++) Enable the NVIC SPI IRQ handle

(##) **DMA Configuration if you need to use DMA process**

(+++) Declare a DMA_HandleTypeDef handle structure for the transmit or receive Stream/Channel

(+++) Enable the DMAx clock

(+++) Configure the DMA handle parameters

(+++) Configure the DMA Tx or Rx Stream/Channel

(+++) Associate the initialized hdma_tx(or _rx) handle to the hspi DMA Tx or Rx handle

(+++) Configure the priority and enable the NVIC for the transfer complete interrupt on the DMA Tx or Rx Stream/Channel

(#) **Program the Mode, BidirectionalMode , Data size, Baudrate Prescaler, NSS

management, Clock polarity and phase, FirstBit and CRC configuration in the hspi Init structure.**

(#) **Initialize the SPI registers by calling the** `HAL_SPI_Init() API`:

(++) This API configures also the low level Hardware GPIO, CLOCK, CORTEX...etc)

by calling the customized HAL_SPI_MspInit() API.

簡述如下:

- 聲明一個

SPI_HandleTypeDef句柄結(jié); - 通過

HAL_SPI_MspInit()初始化 SPI 低級資源;- 使能 SPIx 接口時鐘

- SPI 引腳配置

- 如果需要使用中斷進程,配置NVIC

- 如果需要使用DMA進程,配置DMA

- 在hspi初始化結(jié)構(gòu)體中配置Mode, BidirectionalMode , Data size, Baudrate Prescaler, NSS, management, Clock polarity and phase, FirstBit and CRC

- 通過調(diào)用

HAL_SPI_Init()初始化 SPI 寄存器:

-

接口

+關(guān)注

關(guān)注

33文章

8575瀏覽量

151015 -

STM32

+關(guān)注

關(guān)注

2270文章

10895瀏覽量

355743 -

SPI總線

+關(guān)注

關(guān)注

4文章

103瀏覽量

27586 -

同步通信

+關(guān)注

關(guān)注

0文章

28瀏覽量

9155

發(fā)布評論請先 登錄

相關(guān)推薦

STM32單片機中的C語言基礎(chǔ)知識

SPI總線協(xié)議的基礎(chǔ)知識

CAN協(xié)議基礎(chǔ)知識

單片機原理及應(yīng)用教程之單片機基礎(chǔ)知識概述

STM32的SPI相關(guān)知識

STM32基礎(chǔ)知識:SPI總線概述

STM32基礎(chǔ)知識:SPI總線概述

評論