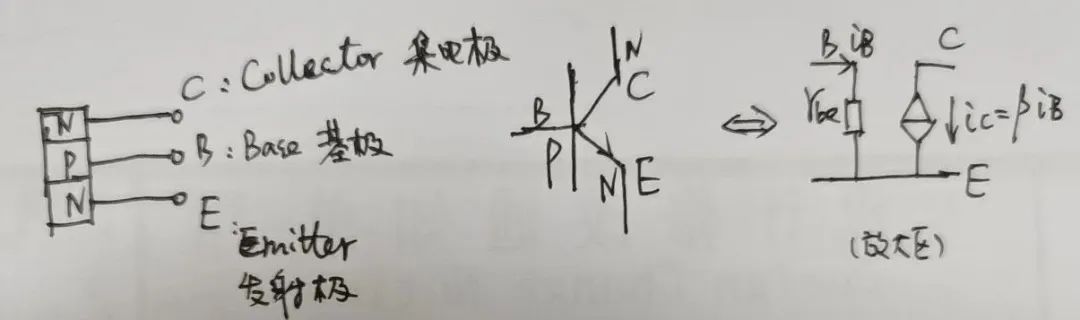

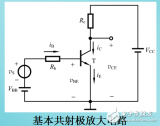

一 NPN和PNP晶體管

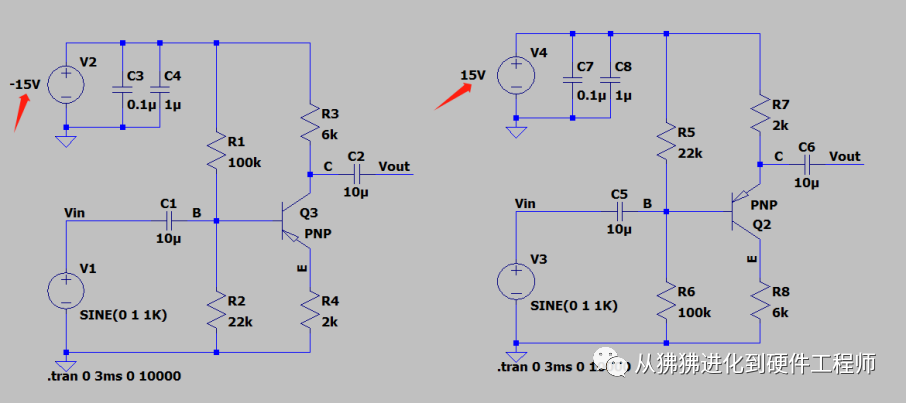

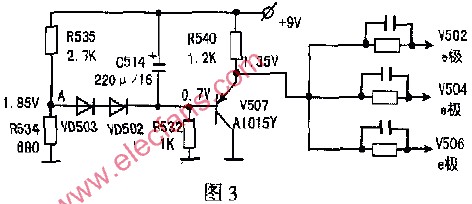

晶體管有NPN和PNP兩種類型。上篇展示的電路都是NPN晶體管搭建的放大電路。使用PNP晶體管搭建電路,因為電流流動方向相反,所以偏置電壓方向也要反過來,因此將電源和GND進行交換。如下是使用PNP晶體管搭建的兩種放大電路。

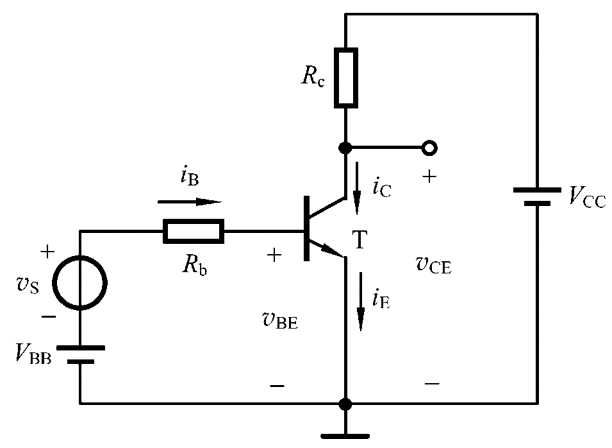

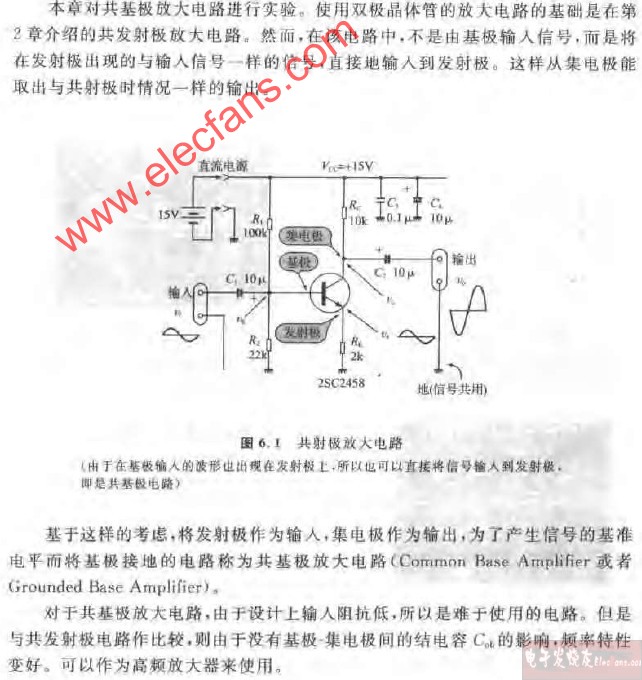

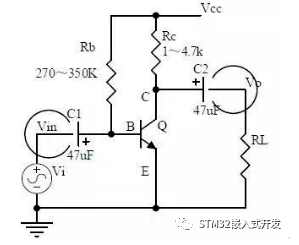

二 設計一個共射極放大電路

讓我們基于如下產品需求設計一個共射ji極放大電路:

電壓增益:3倍

最大輸出電壓:6Vpp

頻率特性:暫不考慮

輸入輸出阻抗:暫不考慮

第一步:確定電源電壓V2

基于最大輸出電壓,選擇電源電壓V2。為了獲得不失真的6Vpp,電源電壓必須比信號最大電壓高。同時要考慮,為了使發射極有電流流過,在發射極上需要有電壓。因此電源電壓要大于信號電壓+發射極電壓的和。

而對發射極來說,我們期望它的電壓在2V以上。因為雖然Vbe≈0.6V,不過它有個溫度特性,元件溫度每升高一度,Vbe減小2.5mV。這樣的話,隨著電路工作時間變長,Vbe的電壓會減小,導致Ve的電壓會減小。因此我們期望Re的直流電壓在2V以上。

基于以上的考慮,電源電壓V2應該在8V以上。我們選擇15作為V2的輸出電壓。

第二步:選擇晶體管

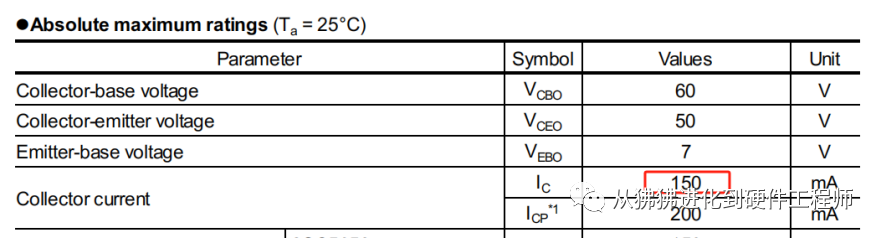

晶體管的特性決定了放大電路的最終性能(噪聲、高頻特性等)。另外晶體管的最大額定電壓不能超過放大電路要求的。例如如果我們選擇電源(V2)是15V,,那么在集電極和基極之間、集電極和發射極之間有可能施加最大15V的電壓,因此選擇晶體管時,Vcbo和Vceo要大于15V。如下是ROHM的2SC2414K的spec,我們選擇它設計放大電路。

第三步:確定發射極工作電流

在確定發射極電流之前,先介紹一個參數fT。在上面的spec中出現。它是晶體管的特征頻率,表示交流電流放大系數為1時的頻率。它的值和發射極電流有關聯。如下圖。如果希望用此晶體管設計的放大電路頻率特性最好,必須是IE=30mA。

另外,放大電路的噪聲也和發射極電流有關。需要注意的是,同一顆晶體管頻率特性最好的IE和噪聲特性最好的IE是不一樣的。

如果放大電路對頻率和噪聲沒有嚴格要求,那么IE取值范圍就比較寬松了,只要不大于spec定義的最大額定電路150mA(下圖)即可。

我們取IE=1mA,方便后續計算。

第四步:確定集電極電阻和發射極電阻

前一篇提到此放大電路的放大倍數是由集電極電阻和發射極電阻的比值決定的。因此如果Av=3,則R3:R4=3。

前面也提到我們設定VE=2V,

因此得到R4=VE/IE=2V/1mA=2KR

R3=Av x R4=6KR

VCE=VC-VE=V2 - IC x R3 - IE x R4 =15V - 1mA x 6KR -1mA x 2KR=7V

同時得到晶體管的集電極損耗Pc為

Pc=VCE x IE =4V x 1mA =4mW

它低于元件spec定義的Pd=200mW最大值。

另外,集電極電阻R3的取值也會影響輸出波形。如果R3取值太大,在其自身的壓降變大,集電極電位下降,在輸出大振幅信號時,輸出波形的下側會失真。最好是將集電極電位設置在V2和VE的中點。

注:V2的電壓會影響VE電壓和IE。如果V2不是15V,例如是12V,則VE不是2V,IE也不是1mA。

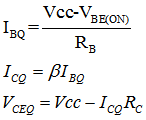

第五步:確定基極偏置電路

因為已經設定VE=2V,又因為VBE=0.6V,因此VB=2.6V。

VB的電壓是由R1和R2分壓得到。如果VB,也即R2上的分壓為2.6V,那么R1上的壓降為V2-VB=12.4V。

這顆晶體管的hFE在120~390之間,取個中間值hFE=200,那么基極電流大約在5uA。我們希望流過R1和R2的電流比基極電流大的多(10倍以上就可以),因此設定流過R1的電流是100uA,那么就可以得到R1和R2的阻值

R1=12.4V/100uA=124KR

R2=2.6V/100uA=26KR

不過這兩個電阻在電阻系列中不多見(E24系統數列),選擇和它倆比值一樣的另一組電阻100KR和22KR。不改變R1和R2的比值,是因為比值變了,VB就會變。

通過以上幾步,電路的基本框架就搭出來了。

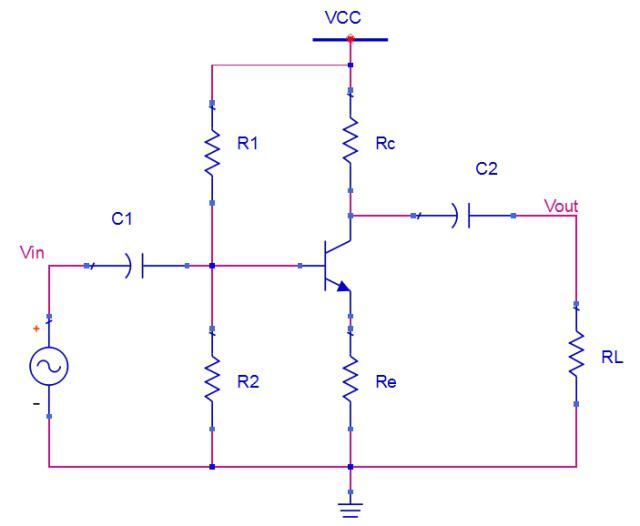

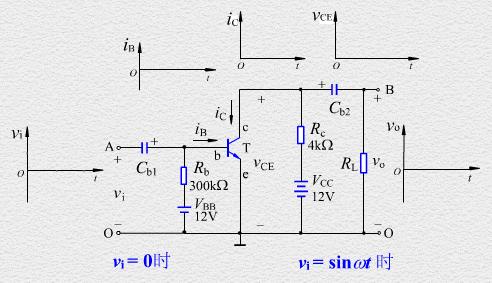

如下圖是電路和它的各個直流電壓和電流,與計算基本一致。

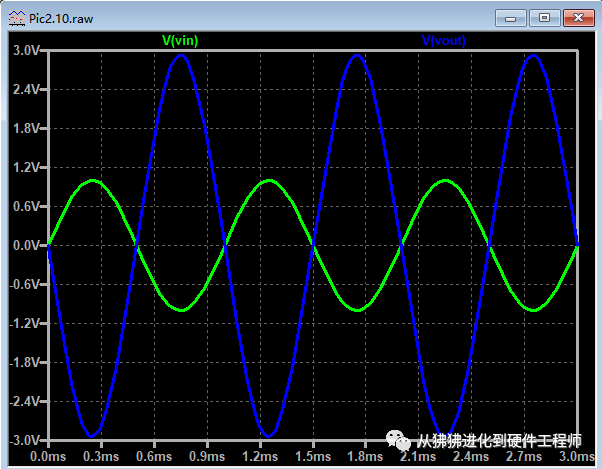

信號放大比例是3倍

C1和C2的作用是將基極/集電極的直流電壓擋住,只讓交流信號輸入/輸出。C1和電路的輸入阻抗、C2和負載分別組成高通濾波器。

輸入阻抗是R1和R2的并聯,因為從交流信號的角度,電源和地是一樣的,又因為基極電流非常小,可以認為晶體管本身的輸入阻抗非常大,因此輸入阻抗是R1和R2的并聯。輸出阻抗是由C2和RL構成。

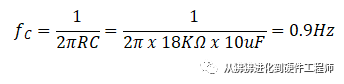

當C1和C2取值太小時,會導致截止頻率太高,在濾波效果上使低頻信號難于通過,此處選擇C1=C2=10uF

輸入端的高通濾波器截止頻率fC為:

第七步:電源去耦電容C3和C4的選擇

C3和C4是電源的去耦電容,降低電源和GND之間的交流阻抗,也稱為旁路電容。如果沒有這些電容存在,電路的交流特性會變差,嚴重時電路會產生振蕩。

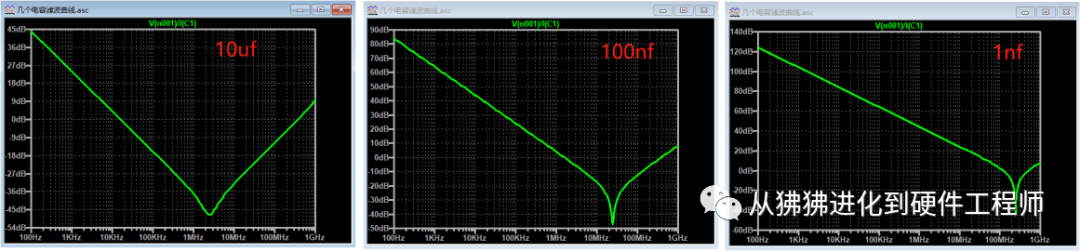

電容的阻抗值是1/2πfC,信號頻率越高,阻抗越低。現實中,由于電容結構中寄生電感的影響,當超過某一頻率時,電容阻抗反而會上升。如下圖三種不同容值的電容,它們各自的阻抗曲線。

在電源設計時,并聯容值大小不同的電容,使整個電源網絡對GND的交流阻抗在一定的頻率段內都比較小。具體的頻率范圍,可以看負載端的需求。以TI的SOC J6為例,它的spec中對200MHz以內的電源網絡交流阻抗有明確要求。

將這三顆電容并聯之后的阻抗曲線如下:可以看到在很寬的頻率范圍內都下降了。小容值電容要布置在電源附近。否則寄生電感變大,影響阻抗和濾波效果。

至此,一個基本的共射極放大電路就搭建好了。

-

放大電路

+關注

關注

104文章

1787瀏覽量

106662 -

電路設計

+關注

關注

6673文章

2451瀏覽量

204168 -

晶體管

+關注

關注

77文章

9682瀏覽量

138084 -

pnp

+關注

關注

11文章

297瀏覽量

51775 -

共射極放大電路

+關注

關注

0文章

39瀏覽量

3347

發布評論請先 登錄

相關推薦

共射極放大電路設計步驟

共射極放大電路設計步驟

評論