今天來(lái)聊聊我們常用的邏輯電路是如何通過(guò)MOS管實(shí)現(xiàn)的。

如果你還沒(méi)開(kāi)始接觸CMOS管也不用著急,我會(huì)用簡(jiǎn)單的結(jié)論來(lái)描述我要用到的MOS管的功能,只需要把CMOS管看作一個(gè)受電壓控制的開(kāi)關(guān)就可以了。

下面我們直接進(jìn)入實(shí)例。

1.反相器 (INV)

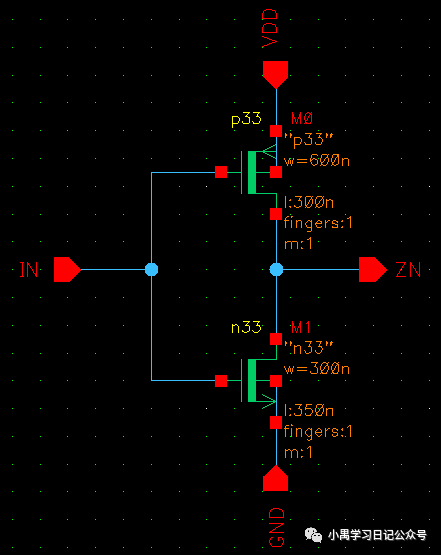

反相器的MOS管實(shí)現(xiàn)

如圖,這個(gè)反相器可以理解為是由兩個(gè)電壓控制的開(kāi)關(guān)組成。

(眼細(xì)的朋友可能會(huì)發(fā)現(xiàn),這兩個(gè)MOS管的右端不止有兩個(gè)端口,在正中間還有一個(gè)接口,我們暫時(shí)不考慮這個(gè)接口,只需要記住絕大部分情況下把它與MOS管的源極連接的就行了。)

到此,基本講完了MOS管的開(kāi)關(guān)功能,那么我們來(lái)分析一下這個(gè)電路的功能。

可見(jiàn),電路由一個(gè)NMOS管和一個(gè)PMOS連接而成,上面的PMOS管源極連接電源電壓 VDD ,下滿的NMOS管源極連接地電壓 GND ,然后兩個(gè)MOS管的漏極同時(shí)連接輸出端口 ZN ,兩個(gè)MOS管的柵極同時(shí)接在輸入端 IN 。

當(dāng)IN時(shí)低電平時(shí),PMOS管導(dǎo)通,NMOS管關(guān)閉,因此這個(gè)電路可以理解為輸出端ZN通過(guò)導(dǎo)線直接連接電源電壓 VDD ,因此輸出端ZN直接輸出高電壓 VDD ;

當(dāng)IN時(shí)低電平時(shí),NMOS管導(dǎo)通,PMOS管關(guān)閉,因此這個(gè)電路可以理解為輸出端ZN通過(guò)導(dǎo)線直接連接地電壓 GND ,因此輸出端ZN直接輸出低電壓 GND ;

由此可見(jiàn),這個(gè)電路的功能是使輸入的低電壓轉(zhuǎn)換成高電壓,使輸入的高電壓轉(zhuǎn)換成低電壓。用數(shù)字電路的語(yǔ)言就是, 輸入0,PMOS管導(dǎo)通,NMOS管關(guān)閉,則輸出1;輸入1,NMOS管導(dǎo)通,PMOS管關(guān)閉,則輸出0 。因此我們稱這個(gè)電路為反相器或者 非門(mén) 。此外還能看出一個(gè)結(jié)論,輸出低電壓時(shí)是NMOS在工作PMOS不工作,輸出高電壓時(shí)是PMOS管在工作NMOS不工作。

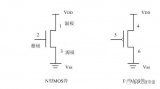

反相器Symbol

我們一般會(huì)在電路中用這個(gè)符號(hào)來(lái)表示非門(mén),三角形表示一個(gè)類(lèi)似于導(dǎo)線的東西,專業(yè)點(diǎn)的稱呼好像是叫BUFF,然后三角形末端的圓表示一個(gè)“負(fù)號(hào)”(“翻轉(zhuǎn)”)的意思。

理解了反相器(非門(mén)),那么我們就想來(lái)通過(guò)MOS管實(shí)現(xiàn)更多的邏輯運(yùn)算,而這些邏輯運(yùn)算的基本就是,或、與、非三種基本運(yùn)算,而在MOS管中能直接實(shí)現(xiàn)的是與非門(mén)、或非門(mén),通過(guò)把與非、或非組合一個(gè)非門(mén)我們就能有基本的或與非三種邏輯運(yùn)算了。下面我們接著來(lái)介紹通過(guò)MOS管搭建與非門(mén)、或非門(mén)、異或門(mén)。

2.與非門(mén)(NAND)

與非門(mén)的MOS管實(shí)現(xiàn)

一般結(jié)論的理論分析:

條件:

a.NMOS管柵極接高電壓才導(dǎo)通,且負(fù)責(zé)輸出低電壓;

b.PMOS管柵極接低電壓才導(dǎo)通,且負(fù)責(zé)輸出高電壓;

(可見(jiàn)POMS電路塊和NMOS電路塊是一個(gè)互補(bǔ)的關(guān)系;)

c.要求NMOS端導(dǎo)通帶來(lái)低電壓時(shí)PMOS端不能導(dǎo)通出高電壓,反之亦然;

分析:

要保證電路滿足上面c.條件,我們只需要保證PMOS塊和NMOS塊實(shí)現(xiàn)的邏輯功能是一個(gè)等價(jià)的邏輯運(yùn)算式就可以了。

考慮我們這個(gè)實(shí)例,與非門(mén):

Y=~(A&&B) =(~A)||(~B)

NMOS塊我們考慮實(shí)現(xiàn)邏輯式

Y=~(A&&B)

因?yàn)镹MOS管是柵極高電壓導(dǎo)通,這正好符合這個(gè)式子A,B高電平有效,即直接對(duì)A,B進(jìn)行運(yùn)算,且當(dāng)式子 (A&&B)=1時(shí),輸出低電平,即正好滿足NMOS管的負(fù)責(zé)低電平且輸入要求高電平有效,由此只需要實(shí)現(xiàn) A,B兩信號(hào)的邏輯與關(guān)系就可以了。這個(gè)關(guān)系邏輯與關(guān)系,可以直接通過(guò)MOS開(kāi)關(guān)串聯(lián)的思路實(shí)現(xiàn)。即當(dāng)A=1時(shí)開(kāi)關(guān)A閉合,當(dāng)B=1時(shí)開(kāi)關(guān)B閉合,兩者串聯(lián)就是要求A,B同時(shí)等于1時(shí)這個(gè)線路才導(dǎo)通,如下圖所示,且這里NMOS管的導(dǎo)通會(huì)把NMOS管源極的低電平導(dǎo)通過(guò)來(lái),因此這個(gè)正好對(duì)應(yīng)關(guān)系式Y=~(A&&B) ;所以我們只需要串聯(lián)兩個(gè)NMOS管就可以實(shí)現(xiàn)NMOS塊了,如圖(與非門(mén)的MOS管實(shí)現(xiàn))所示。

與開(kāi)關(guān)邏輯

PMOS塊我們考慮實(shí)現(xiàn)這個(gè)邏輯式

Y= (~A)||(~B)

因?yàn)镻MOS管是低電平導(dǎo)通,正好符號(hào)這個(gè)式子A,B低電平有效,即直接對(duì) (~A),(~B) 進(jìn)行運(yùn)算,然后PMOS輸出的是高電平,這個(gè)式子也是,此外在這個(gè)式子是邏輯或的關(guān)系,因此只需要要并聯(lián)兩個(gè)PMOS管就可以了。

或開(kāi)關(guān)邏輯

最后把PMOS塊和NMOS塊連接到相同的輸出端口就能實(shí)現(xiàn)邏輯運(yùn)算了。

與非門(mén)Symbol

3.或非門(mén)(NOR)

或非門(mén)的MOS管實(shí)現(xiàn)

或非門(mén)邏輯關(guān)系式:

Z= ~(A||B) = (~A)&&(~B)

理解了我對(duì)與非門(mén)的分析,那么或非門(mén)也能很快自己搭建出來(lái)。

用NMOS管并聯(lián)實(shí)現(xiàn)對(duì) A,B 的邏輯或功能,用PMOS管串聯(lián)實(shí)現(xiàn)對(duì) (~A),(~B) 的邏輯與功能,如上圖(或非門(mén)的MOS管實(shí)現(xiàn))所示。

或非門(mén)Symbol

4.異或門(mén)(XOR)

異或門(mén)的MOS管實(shí)現(xiàn)

有了基本的或與非邏輯單元,我們就能實(shí)現(xiàn)復(fù)雜的邏輯功能了。在這里展示一下異或門(mén)的實(shí)現(xiàn)。有邏輯運(yùn)算基礎(chǔ)的同志能很快地分析完這個(gè)電路,故不做贅述。

異或門(mén)Symbol

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42609 -

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1295瀏覽量

103918 -

MOS管

+關(guān)注

關(guān)注

108文章

2410瀏覽量

66760 -

反相器

+關(guān)注

關(guān)注

6文章

311瀏覽量

43289 -

電源電壓

+關(guān)注

關(guān)注

2文章

989瀏覽量

23969

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

邏輯電路芯片-組合邏輯電路芯片-時(shí)序邏輯電路芯片

MOS管的主要電路邏輯

【原創(chuàng)】組合邏輯電路詳解、實(shí)現(xiàn)及其應(yīng)用

組合邏輯電路常見(jiàn)的類(lèi)型

常見(jiàn)的組合邏輯電路分析

在FPGA開(kāi)發(fā)板中點(diǎn)亮LED燈實(shí)現(xiàn)時(shí)序邏輯電路的設(shè)計(jì)

數(shù)字系統(tǒng)的基本算法與邏輯電路實(shí)現(xiàn)

鐘控傳輸門(mén)絕熱邏輯電路和SRAM的設(shè)計(jì)

CPLD邏輯電路

組合邏輯電路的設(shè)計(jì)說(shuō)明

與非門(mén)邏輯電路功能測(cè)試的原理圖免費(fèi)下載

與非門(mén)搭接的邏輯電路原理圖免費(fèi)下載

硬件工程師必看的技能之MOS管構(gòu)成的基本門(mén)邏輯電路

模擬IC設(shè)計(jì)原理圖1:邏輯電路是如何通過(guò)MOS管實(shí)現(xiàn)的

模擬IC設(shè)計(jì)原理圖1:邏輯電路是如何通過(guò)MOS管實(shí)現(xiàn)的

評(píng)論