來源:《半導體芯科技》雜志

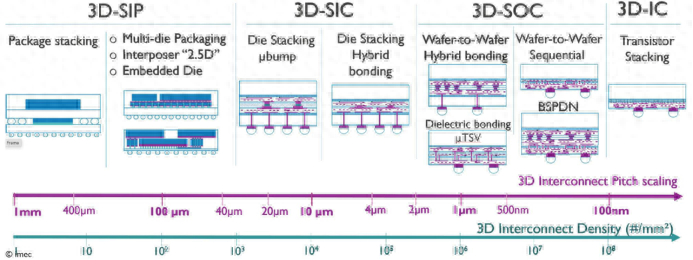

隨著人工智能(AI)、無人駕駛、增強現實/虛擬現實(AR/VR)和5G等前沿應用的快速發展,半導體制造商需要在不增加生產成本的前提下開發出高帶寬、高性能、低功耗設備。隨著傳統的二維硅片微縮技術達到其成本極限,半導體行業正轉向異構集成技術。異構集成是指不同特征尺寸和材質的多種組件或晶片的制造、組裝和封裝,使其集成于單個器件或封裝之中,以提高新一代半導體器件的性能。

經過集成式晶片到晶圓鍵合后附在晶圓上的獨立晶片

晶圓到晶圓(W2W)混合鍵合涉及不同生產線的晶圓堆疊和電連接處理,是異構集成的核心工藝,在CMOS圖像傳感器以及各類內存以及邏輯技術應用中表現出色。然而,在組件或晶片尺寸不相同的情況下,晶片到晶圓(D2W)混合鍵合更適用于異構集成。憑借新型D2W鍵合解決方案和市場領先的W2W混合鍵合解決方案,加之異構集成能力中心(Heterogeneous Integration Competence Center?)帶來的豐富行業合作經驗,EV集團(EVG)為D2W鍵合應用提供有力支持。

01融熔和混合鍵合技術

融熔或直接晶圓鍵合可以通過每個晶圓表面上的介電層實現永久連接,用于工程基板或層轉移,例如背照式CMOS圖像傳感器。

混合鍵合擴展了融熔鍵合,在鍵合界面中嵌入金屬焊盤,允許晶圓的面對面(face-to-face)連接。混合鍵合的主要應用是先進的三維(3D)器件堆疊。

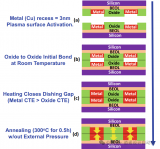

融熔或直接晶圓鍵合允許介電層和更精確活化的官能團懸垂,在氫橋鍵(hydrogen bridge bond)的幫助下在晶圓之間橋接。該預粘合步驟在室溫和大氣條件下進行。只有在隨后的退火步驟中,低能氫橋鍵才會變成共價鍵。

融熔鍵合傳統上用于工程基板,最近用于使用全面積電介質的堆疊晶圓。由于在環境條件下進行預鍵合,小于100nm的高精度對準允許3D集成場景使用晶圓到晶圓融熔鍵合。此外,銅焊盤可以與介電層并行加工,允許在環境溫度下預粘合介電層,而電接觸可以在退火期間通過金屬擴散鍵合實現。這種特殊情況稱為混合鍵合。混合鍵合的主要應用包括CMOS圖像傳感器、存儲器以及3D片上系統(SoC)。

02D2W融熔和混合鍵合

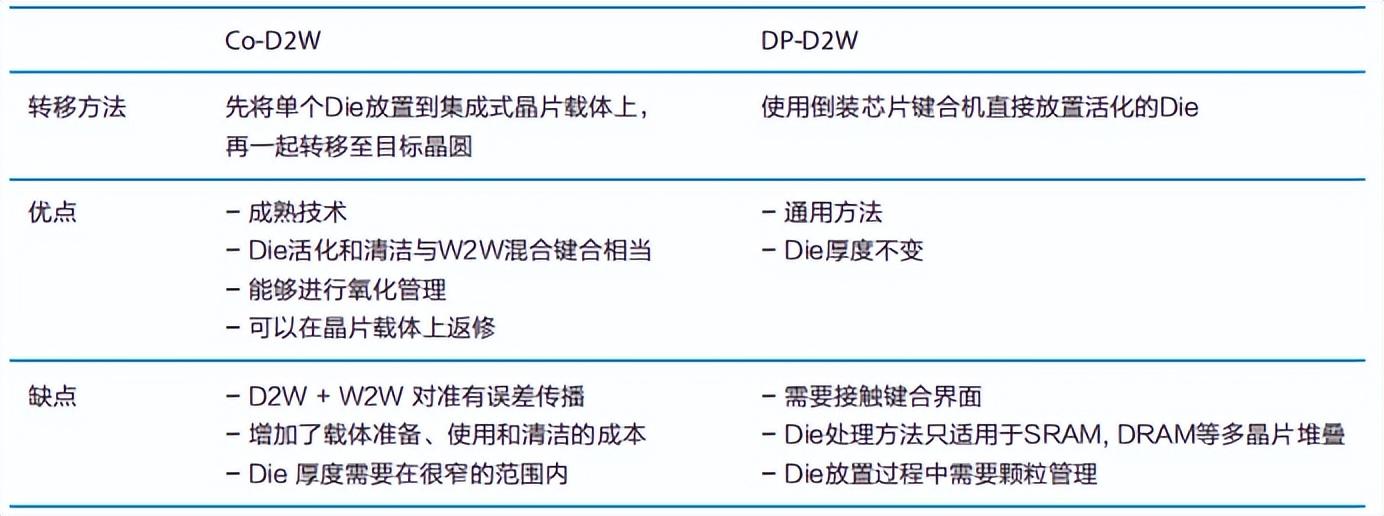

作為異構集成的核心工藝,W2W混合鍵合,已經在CMOS圖像傳感器和各種存儲器、邏輯技術方面獲得良好的成功記錄。然而,由于許多小芯片(chiplet)的尺寸不一定相同,因此D2W混合鍵合方法可能更實用。異構集成有幾種不同的D2W鍵合方法,包括集成式D2W(Collective D2W,Co-D2W)和直接放置D2W(Direct Placement,DP-D2W)鍵合,每種方法都有各自的優點和缺點,如表1所示。

△表1:Co-D2W和DP-D2W兩種鍵合方法對比

03Co-D2W鍵合

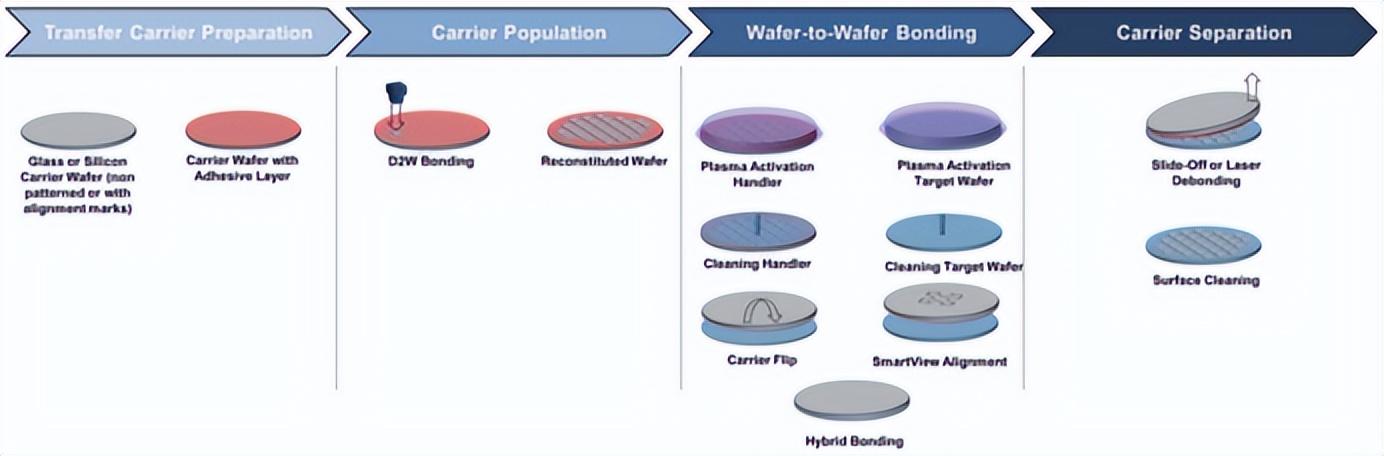

在過去幾年中,Co-D2W鍵合已經在硅光子學等應用中有限批量生產中實施。在Co-D2W鍵合中,是在單個工藝步驟中將多個晶片一次轉移到最終晶圓上。Co-D2W鍵合工藝的制造流程如圖1所示,包括四個主要部分:晶片載體(晶圓)制備、載體填充(在載體上放置晶片)、晶圓鍵合(臨時和永久)和載體分離。

△圖1:Co-D2W鍵合工藝的制造流程。

04DP-D2W鍵合

用于異構集成的另一種混合D2W鍵合方法是DP-D2W鍵合,其中使用拾放式倒裝芯片鍵合機將晶片逐一單獨鍵合到目標晶圓上。圖2顯示了DP-D2W鍵合工藝的制造流程,其成本包括三個主要部分:載體填充(在載體上放置晶片,為清潔做準備)、晶片清潔和活化、直接貼裝倒裝芯片。

圖2:DP-D2W鍵合工藝的制造流程。

目前有多種D2W鍵合技術和設備可供使用,可以根據應用和客戶要求進行選擇。在Co-D2W鍵合中,單個晶片放置于集成式晶片載體之上,再送至目標晶圓進行晶片轉移,此時可使用W2W混合鍵合系統(如GEMINI FB)完成晶片與目標晶圓的鍵合。在DP-D2W鍵合中,則使用拾放式倒裝晶片鍵合機將單個晶片逐一鍵合至目標晶圓上。等離子體活化和處理器芯片上的晶片表面清潔是在晶片和目標晶圓之間建立高產量鍵合和電界面的關鍵步驟。而這一步正是EVG? 320D2W活化系統發揮作用的重要舞臺。

05利用EVG的異構集成能力中心?加速技術開發

為了應對異構集成技術挑戰,EVG建立了異構集成能力中心?(HICC)。該中心致力于幫助客戶充分利用EVG工藝解決方案和專業知識,通過系統集成和封裝技術的進步,加速開發創新產品和應用。

2022年7月,EVG宣布在D2W熔融與混合鍵合領域取得重大技術突破。EVG在單次轉移過程中使用GEMINI? FB自動混合鍵合系統,在完整3D SoC中對不同尺寸芯片實施無空洞鍵合,良率達到100%。直至今天,此類鍵合仍是D2W鍵合領域面臨的關鍵挑戰,也是降低異構集成成本的主要障礙。EVG的異構集成技術中心(HICC ?)取得了這一重大技術突破。

混合鍵合的接口呈固態,采用嵌入式金屬焊盤,以實現晶圓和芯片的直接電氣連接,因此D2W混合鍵合需要達到與前端半導體制造工藝類似的清潔度標準和制造公差。在這一趨勢的推動下,高精度計量在控制混合鍵合對準和工藝良率方面開始發揮更為重要的核心作用,反過來又推動了D2W鍵合和計量工藝集成為統一生產線。

GEMINI? FB自動化Co-D2W鍵合系統

此外,目前數種不同的D2W混合鍵合工藝流程正在接受評估,每種工藝流程都有其獨特優勢和要求。自兩年前成立以來,HICC發揮了重要作用,幫助客戶和合作伙伴開發及優化D2W混合鍵合工藝,滿足給定器件設計和應用的獨特需求,并在開發中綜合考慮多種因素,如芯片尺寸、芯片厚度、總堆疊高度,以及觸點設計和密度等接口考慮因素。HICC還配備了先進的潔凈室,其潔凈度標準與多家領先半導體工廠相當,使EVG有能力滿足D2W和W2W混合鍵合工藝開發的嚴格要求。

EVG業務發展總監托馬斯·烏爾曼(Thomas Uhrmann)博士表示:“混合鍵合需要完全不同于標準封裝工藝的制造技術,它更接近前端制造——特別是在清潔度、顆粒控制、對準和計量精度方面。我們在W2W混合鍵合領域處于市場領先地位。在此基礎上,我們將繼續擴展D2W混合鍵合解決方案,優化設備,為重要的上下游工藝提供支持,包括等離子活化和清潔技術,以加快部署和完善D2W混合鍵合技術。數年之前,EVG的GEMINI FB技術已配置用于D2W集成流程,滿足D2W鍵合需求。EVG? 320 D2W晶片準備和活化系統則用于D2W鍵合的直接貼裝,提供與D2W鍵合機的直接接口。EVG? 40 NT2套刻計量系統使用AI、前饋和反饋回路進一步提高混合鍵合良率。在這些技術之外,EVG又推出完整的端到端混合鍵合解決方案,以加速部署3D/異構集成。”

參考文獻

1.EV集團實現芯片到晶圓熔融和混合鍵合技術突破多芯片3D片上系統的芯片轉移良率達到100%.

2.EVG's die-to-wafer fusion and hybrid bonding technologies - supporting collective die-to-wafer as well as direct die-to-wafer process flows.

3.EV集團(EVG)在中國國際半導體展上展示新型晶片到晶圓混合鍵合活化解決方案,旨在加快3D-IC/異構集成技術的發展

審核編輯 黃宇

-

傳感器

+關注

關注

2550文章

51035瀏覽量

753077 -

晶圓

+關注

關注

52文章

4890瀏覽量

127931 -

封裝

+關注

關注

126文章

7873瀏覽量

142893 -

AI

+關注

關注

87文章

30728瀏覽量

268886 -

人工智能

+關注

關注

1791文章

47183瀏覽量

238255

發布評論請先 登錄

相關推薦

三維堆疊封裝新突破:混合鍵合技術揭秘!

混合鍵合推動異構集成發展

混合鍵合推動異構集成發展

評論