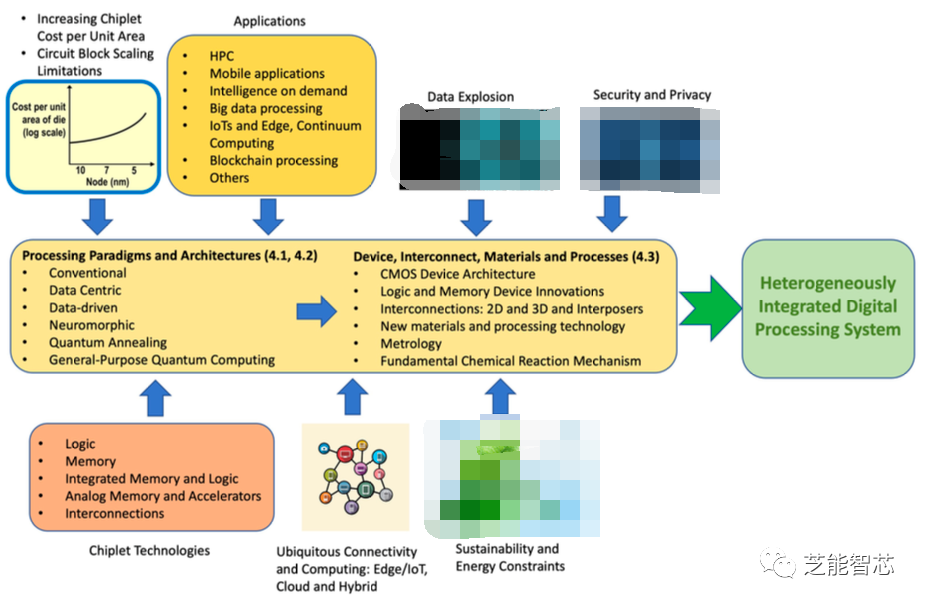

數(shù)字處理技術(shù)的路線(xiàn)圖探討了當(dāng)前和新興的數(shù)字處理驅(qū)動(dòng)因素,以及處理范式中所需的創(chuàng)新。這些要求決定了數(shù)字處理、內(nèi)存、支持芯片、互聯(lián)、以及整體系統(tǒng)架構(gòu)所需的技術(shù)和架構(gòu)。

主要分為三部分

●芯片和互連架構(gòu)定義了設(shè)備、互連,以及化學(xué)和化學(xué)處理技術(shù)的要求。

●化學(xué)處理需要對(duì)物理和化學(xué)反應(yīng)機(jī)制有深入的了解,整合到產(chǎn)品中。

●系統(tǒng)級(jí)集成數(shù)字處理系統(tǒng)所需的附加要求和解決方案,以及與整體安全性、功率轉(zhuǎn)換/傳遞、系統(tǒng)可靠性和運(yùn)行時(shí)管理需求相關(guān)的系統(tǒng)級(jí)考慮。

主要障礙和挑戰(zhàn) 在實(shí)現(xiàn)異構(gòu)集成數(shù)字處理系統(tǒng)時(shí),需要解決一些障礙和挑戰(zhàn),包括:

●解決數(shù)據(jù)移動(dòng)的成本問(wèn)題,包括性能(延遲和帶寬)和隨著數(shù)據(jù)量和速率呈指數(shù)增長(zhǎng)而增加的每比特傳輸?shù)目偰芰肯摹?/p>

●限制系統(tǒng)級(jí)別的總能量消耗,極大提高數(shù)字處理系統(tǒng)的能效,以處理數(shù)據(jù)洪流和對(duì)此類(lèi)數(shù)據(jù)的必要處理。

●解決當(dāng)前使用的架構(gòu)和系統(tǒng)中的系統(tǒng)級(jí)封裝(SiPs)所固有的縮放限制,這些限制受到總功率、功率分配、中間層和互連的影響。改善未來(lái)設(shè)備制造的物理和化學(xué)過(guò)程的基本理解,包括先進(jìn)圖案制備、原子尺度薄膜沉積、刻蝕、區(qū)域選擇性沉積和其他選擇性材料處理。

●解決異構(gòu)集成數(shù)字處理系統(tǒng)日益增長(zhǎng)的安全性和可靠性需求,包括監(jiān)視和解釋所有必要信息以確保安全和可靠操作。

●解決并改善端到端的可持續(xù)性,包括前期設(shè)計(jì)、設(shè)計(jì)、制造、使用和最終處理/回收。

●提供高級(jí)設(shè)計(jì)工具,允許將功能解聚為多芯片體系結(jié)構(gòu),并在多個(gè)參數(shù)之間進(jìn)行同時(shí)優(yōu)化;在需要探索的大型設(shè)計(jì)空間中進(jìn)行優(yōu)化提出了需要基于機(jī)器學(xué)習(xí)的解決方案的挑戰(zhàn)。

接下來(lái)需要分三部分來(lái)講解

●第一部分討論應(yīng)用需求如何推動(dòng)數(shù)據(jù)處理范式

●第二部分討論了這在系統(tǒng)級(jí)別的體系結(jié)構(gòu)上產(chǎn)生的影響,以及相關(guān)的挑戰(zhàn)、實(shí)施和技術(shù)需求。

●第三部分系統(tǒng)級(jí)體系結(jié)構(gòu)需求轉(zhuǎn)化為設(shè)備、互連、材料和化學(xué)處理挑戰(zhàn),以及有望的解決方案。

數(shù)字處理范式、系統(tǒng)級(jí)架構(gòu)和數(shù)字處理設(shè)備/材料的路線(xiàn)圖

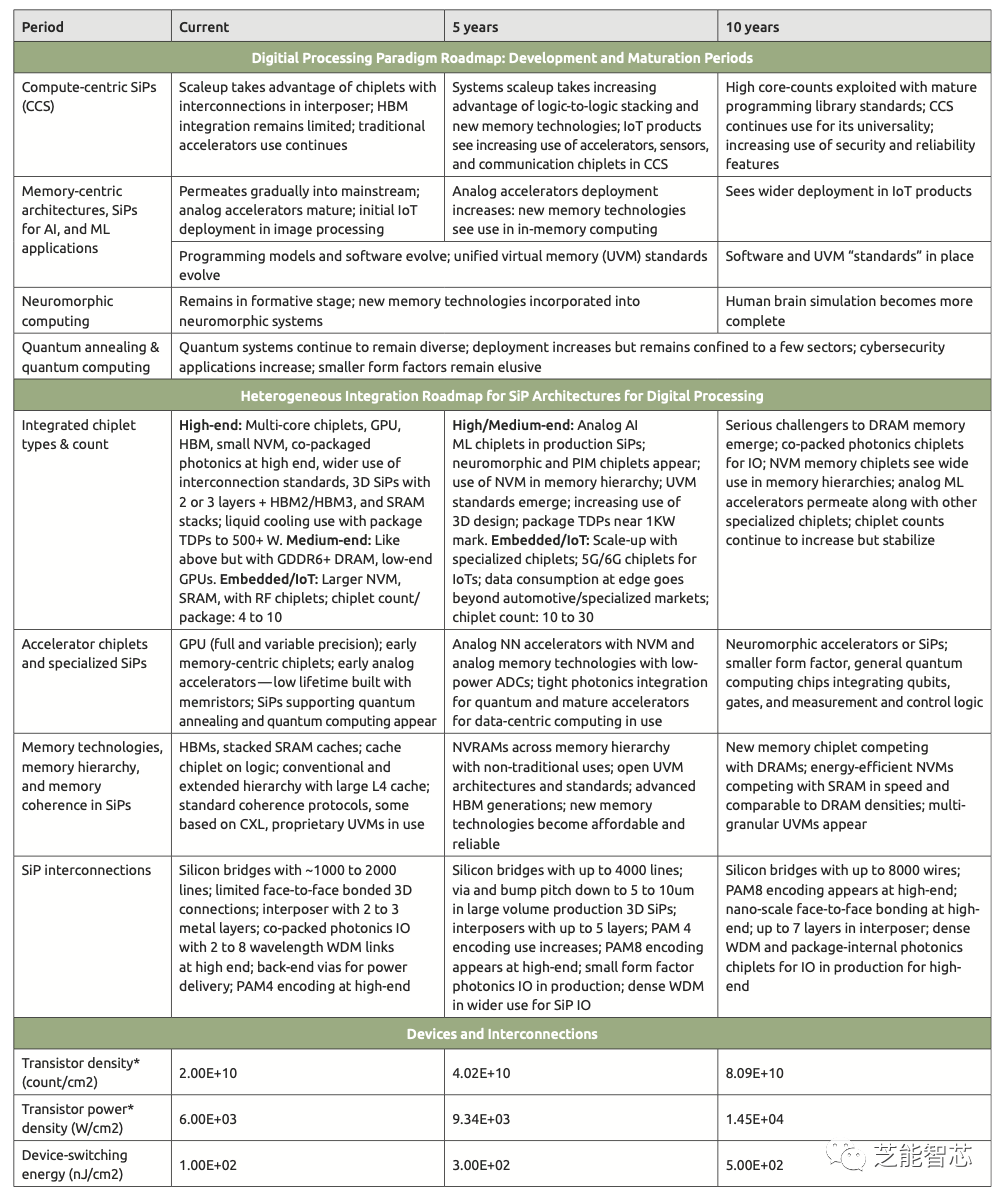

1)基于計(jì)算為中心的系統(tǒng)集成(CCS)

利用在晶片上具有互聯(lián)連接的芯片片(chiplets);高帶寬內(nèi)存(HBM)集成仍然受到限制;傳統(tǒng)加速器的使用持續(xù)增加。

◎隨著系統(tǒng)規(guī)模的擴(kuò)大,邏輯對(duì)邏輯堆疊和新的內(nèi)存技術(shù)得到了越來(lái)越多的應(yīng)用;在CCS中,物聯(lián)網(wǎng)產(chǎn)品越來(lái)越多地使用加速器、傳感器和通信芯片片。

◎成熟的編程庫(kù)標(biāo)準(zhǔn)被用來(lái)充分發(fā)揮高核心數(shù)的優(yōu)勢(shì);CCS由于其通用性繼續(xù)被使用;安全性和可靠性特性的應(yīng)用也在增加。

2)以?xún)?nèi)存為中心的架構(gòu),用于人工智能和機(jī)器學(xué)習(xí)應(yīng)用的系統(tǒng)集成(SiPs)

◎內(nèi)存為中心的架構(gòu)逐漸滲透到主流市場(chǎng);編程模型和軟件不斷發(fā)展;統(tǒng)一虛擬內(nèi)存(UVM)標(biāo)準(zhǔn)不斷完善。

◎模擬加速器技術(shù)成熟;模擬加速器的應(yīng)用范圍擴(kuò)大:初步在物聯(lián)網(wǎng)中應(yīng)用于圖像處理

◎在物聯(lián)網(wǎng)產(chǎn)品中的應(yīng)用范圍擴(kuò)大。軟件和UVM的“標(biāo)準(zhǔn)”已經(jīng)制定。

3)集成芯片片的類(lèi)型和數(shù)量

◎高端:多核心芯片片、圖形處理單元(GPU)、高帶寬內(nèi)存(HBM)、小型非易失性?xún)?nèi)存(NVM)、在高端使用共封裝光子器件、更廣泛地使用互連標(biāo)準(zhǔn)、帶有2或3層3D SiPs + HBM2/HBM3和SRAM疊層;使用液冷技術(shù),功耗上限提高至500瓦以上。

◎中端:類(lèi)似于高端配置,但使用GDDR6+ DRAM,低端GPU。

嵌入式/IoT:較大的非易失性?xún)?nèi)存(NVM)、SRAM,搭配射頻(RF)芯片片;每個(gè)封裝中的芯片片數(shù)量:4至10個(gè)。

◎高/中端:模擬人工智能(AI)和機(jī)器學(xué)習(xí)(ML)芯片片在生產(chǎn)中的SiPs中廣泛應(yīng)用;神經(jīng)形態(tài)和處理器內(nèi)存(PIM)芯片片開(kāi)始出現(xiàn);在內(nèi)存層次結(jié)構(gòu)中使用非易失性?xún)?nèi)存(NVM);統(tǒng)一虛擬內(nèi)存(UVM)標(biāo)準(zhǔn)開(kāi)始出現(xiàn);3D設(shè)計(jì)的使用增加;封裝功耗上限接近1千瓦。

◎嵌入式/IoT:使用專(zhuān)用芯片片進(jìn)行擴(kuò)展;為物聯(lián)網(wǎng)設(shè)計(jì)的5G/6G芯片片;邊緣數(shù)據(jù)處理需求超越汽車(chē)/專(zhuān)業(yè)市場(chǎng);每個(gè)封裝中的芯片片數(shù)量:10至30個(gè)。

DRAM內(nèi)存的嚴(yán)峻挑戰(zhàn)者出現(xiàn);具有共封裝光子學(xué)芯片片的輸入/輸出解決方案;內(nèi)存層次結(jié)構(gòu)中廣泛使用非易失性?xún)?nèi)存(NVM)芯片片;模擬ML加速器和其他專(zhuān)用芯片片逐漸滲透;芯片片數(shù)量繼續(xù)增加但趨于穩(wěn)定。

4)加速器芯片片和專(zhuān)用系統(tǒng)集成(SiPs)

◎GPU(全精度和可變精度);早期的以?xún)?nèi)存為中心的芯片片;早期的模擬加速器。低壽命的構(gòu)建,使用憶阻器;支持量子退火和量子計(jì)算的SiPs開(kāi)始出現(xiàn)。

◎帶有NVM和模擬存儲(chǔ)技術(shù)以及低功耗ADC的模擬神經(jīng)網(wǎng)絡(luò)(NN)加速器;為量子計(jì)算和數(shù)據(jù)中心計(jì)算中的成熟加速器提供緊密的光子學(xué)集成。

◎神經(jīng)形態(tài)加速器或SiPs;較小的尺寸,集成了量子比特、門(mén)電路和測(cè)量與控制邏輯的通用量子計(jì)算芯片。

5)內(nèi)存技術(shù),內(nèi)存層次和內(nèi)存一致性在SiPs中的應(yīng)用

◎HBMs,疊加的SRAM高速緩存;邏輯上的緩存芯片片;帶有大型L4緩存的傳統(tǒng)和擴(kuò)展層次結(jié)構(gòu);標(biāo)準(zhǔn)的一致性協(xié)議,其中一些基于CXL,使用專(zhuān)有的UVM。

◎在內(nèi)存層次結(jié)構(gòu)中使用NVRAM,用于非傳統(tǒng)的用途;開(kāi)放的UVM架構(gòu)和標(biāo)準(zhǔn);先進(jìn)的HBM技術(shù);新的內(nèi)存技術(shù)變得更加經(jīng)濟(jì)實(shí)惠和可靠。

◎新的內(nèi)存芯片片與DRAM競(jìng)爭(zhēng);高效能NVM與SRAM競(jìng)爭(zhēng)速度,并且具有與DRAM相媲美的密度;出現(xiàn)多顆粒度的UVM。

6)SiP的互連技術(shù):

◎硅橋,具有大約1000到2000條線(xiàn);有限的面對(duì)面粘合的3D連接;帶有2到3個(gè)金屬層的中間層;高端配置下,共封裝的光子學(xué)IO具有2到8個(gè)波長(zhǎng)的波分復(fù)用(WDM)鏈路;用于電力傳遞的后端通孔;高端配置下使用PAM4編碼。

◎具有最多4000條線(xiàn)的硅橋;大規(guī)模生產(chǎn)的3D SiPs中通孔和翹邊間距減小至5到10微米;中間層最多5層;高端配置下PAM4編碼的使用增加;高端配置下出現(xiàn)PAM8編碼;生產(chǎn)中使用小尺寸光子學(xué)IO;更廣泛地用于SiP IO的密集WDM。

◎最多8000條線(xiàn)的硅橋;高端配置下出現(xiàn)PAM8編碼;高端配置下納米級(jí)面對(duì)面粘接;中間層最多7層;用于高端產(chǎn)品的密集WDM和封裝內(nèi)部光子學(xué)芯片片的IO正在生產(chǎn)中。

編輯:黃飛

-

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4789瀏覽量

101596 -

SiP

+關(guān)注

關(guān)注

5文章

508瀏覽量

105611 -

adc

+關(guān)注

關(guān)注

99文章

6567瀏覽量

546717 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3081瀏覽量

74592 -

數(shù)字處理

+關(guān)注

關(guān)注

0文章

29瀏覽量

14983

原文標(biāo)題:數(shù)字處理(Digital Process)路線(xiàn)圖

文章出處:【微信號(hào):QCDZSJ,微信公眾號(hào):汽車(chē)電子設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

嵌入式學(xué)習(xí)路線(xiàn)圖

嵌入式學(xué)習(xí)路線(xiàn)圖

靠譜不?分析師自制蘋(píng)果2013年產(chǎn)品路線(xiàn)圖

求STM32的成長(zhǎng)路線(xiàn)圖

嵌入式學(xué)習(xí)路線(xiàn)圖分享

物聯(lián)網(wǎng)學(xué)習(xí)路線(xiàn)圖

Intel公布2021年CPU架構(gòu)路線(xiàn)圖及封裝技術(shù)

嵌入式學(xué)習(xí)路線(xiàn)圖怎么學(xué)

白熾燈淘汰路線(xiàn)圖

OLED產(chǎn)品技術(shù)路線(xiàn)圖國(guó)際研究

未來(lái)10年智能傳感器怎么發(fā)展?美國(guó)發(fā)布最新MEMS路線(xiàn)圖

探討數(shù)字處理技術(shù)的路線(xiàn)圖

探討數(shù)字處理技術(shù)的路線(xiàn)圖

評(píng)論