**1 **ESD Scheme

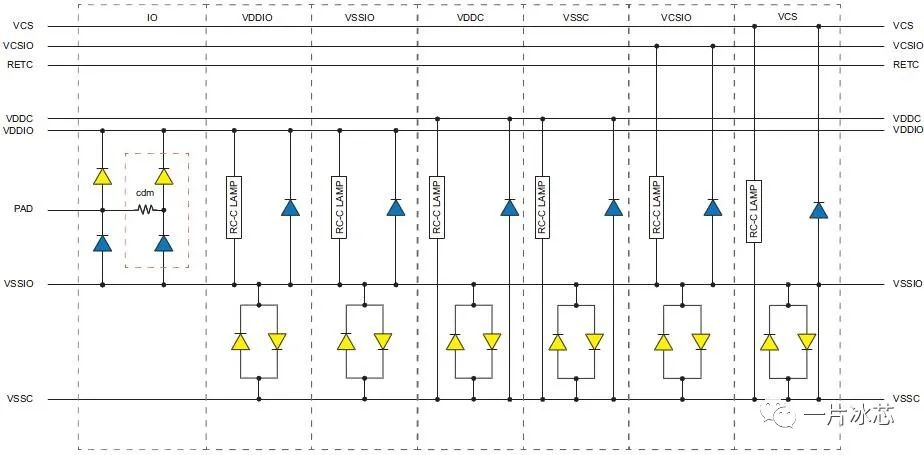

一般多電源軌的ESD方案如圖1所示。最左側兩個diode用于HBM(Human Body Model)保護,與其相鄰的電阻(250Ω)及diode用于CDM(Charge Device Model)保護,PAD和VDDIO之間的P-diode用于正向ESD放電,PAD和VSSIO之間的N-diode用于負向ESD放電,當正向ESD發生時電源地之間的RC-CLAMP觸發,當負向ESD發生時電源地之間的N-diode觸發,VSSIO和VSSC之間的背靠背diode提供雙向ESD放電通路。

Fig1. ESD Scheme

再跟大家啰嗦兩句,你有沒有好奇過圖2所示,我們手中的micro-SD card,為什么會有兩個腳突出來呢?其實這兩個腳就是芯片的電源和地,當芯片插入卡槽過程中突出的引腳會率先與卡槽接觸,實現預放電,達到ESD保護的目的,哈哈,是不是很有意思。

無規矩不成方圓,ESD當然也有專門的標準,如HBM的ANSI/ESDA/JEDECJS-001-2017標準,CDM的ANSI/ESDA/JEDECJS-002-2014標準以及MM(Machine Model)的ANSI/ESDSTM5.2-2012標準等。工業、軍品、汽車(HBM一般要達到8000V)、宇航ESD標準不一,你的芯片對應哪個市場就follow哪個啦。

圖1所示的RC-CLAMP要滿足以下條件:

① DC狀態各PVT下有較小的leakage;

② HBM、CDM、MM下各晶體管不得出現耐壓問題;

③ 各電源上下電時保證RC-CLAMP的功率管關斷。

我似乎跑題了,ESD內容太多了,以后有機會再跟大家聊吧,下面書歸正傳。

**2 **Latch up

2.1 bulk工藝中的latch up

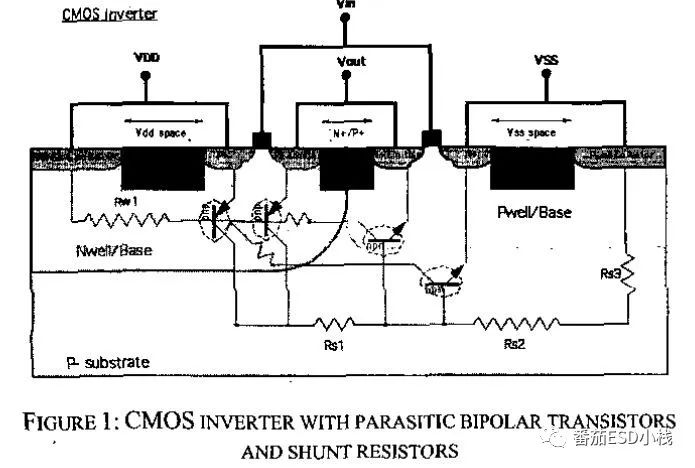

bulk工藝中的latch up原理及觸發機理就不啰嗦了,請自行找度娘學習,我這邊只貼一張圖。

Fig3. inverter的剖面圖及寄生模型

可見bulk工藝中的latch up跟寄生電阻密切相關,layout時要特別注意有源區到阱邊界距離,不同電位阱之間的距離(通常要求1.5倍以上最小線寬),過孔和通孔數量等問題。

2.2 SOI工藝中的latch up

SOI(Silicon-on-Insulator),在摩爾定律的延續一講中給大家介紹過,沒接觸這個工藝的先自己學習一下。SOI中的耗盡層夾在兩層氧化層之間,類似于三明治,圖4給出了SOI和bulk工藝的剖面圖,圖中左面的埋藏氧化層厚度只有20nm左右而且平整度要求非常高,能提供這種晶圓的寥寥無幾,價格也相對較高。

Fig4. SOI和bulk工藝CMOS晶體管的剖面圖

SOI工藝通過超薄埋氧實現了器件隔離,因此寄生BJT也不存在,從而實現latch up immune。那么本章為什么還要提SOI工藝中的latch up呢?在SOI工藝中并不是所有器件都做在超薄埋氧中,如diode、varactor電容、ldmos等,因此也會有latchup薄弱點。

下面以Invecas公司在22nm FDSOI中遇到的問題 ^[1]^ 為例進行latch up分析。

據我了解,Globalfoundries 22nm FDSOI工藝一次full mask的價格現在的價格約1000萬RMB,因此這個latch up問題可能讓Invecas公司損失1000萬RMB甚至更多。

論文中的3.3V RC-CLAMP,正如圖1中VDDIO和VSSIO之間的RC-CLAMP,Invecas設計的第一版3.3V RC-CLAMP電路如圖5所示。其中VDD3V3為3.3V電源,EGNCAP為體硅器件,內部所有器件(電阻除外)任意兩端電壓(背柵除外)不得超過1.8V,因此這是一種用1.8V device設計的耐壓結構RC-CLAMP。

Fig5. 第一版3.3V RC-CLAMP

latch up測試出現問題是在圖1中的PAD抽負電流時引起GPIO相鄰位置的RC-CLAMP的N2和N3管(圖5)導通,芯片熱點分析如圖6所示。

Fig6. 芯片熱點分析

該latch up不同于傳統體硅中npnp(圖3),它是由GPIO PAD(圖1和圖6)上的負電流latch up測試引起的寄生npn導通(為了與傳統npnp latch up區分,這里叫pseudo latch up),如圖7所示。主要原因是圖5中的大電容采用了EGNCAP,EGNCAP是做在Hybrid region,是一種varactor電容,有源區做在了N阱中,剖面圖如圖8所示。

正常工作時P_BIAS處于中間電位(VDD3V3/2),當負latch up電流注入IO PAD時P_BIAS中的N阱會收集電子,導致P_BIAS電位降低,進而開啟N2和N3管,導致電源和地之間出現大電流,即使移除負向latchup測試電流,N2和N3管仍會保持開啟。

Fig7. Trigger path from IO PAD to neighboring nwell of EGNCAP from supply cell

Fig8. EGNCAP剖面圖

針對以上問題,對Invecas對RC-CLAMP電路進行了修改,修改后的電路如圖9所示。最明顯的一個特征就是用EGNFET替換了EGNCAP電容,EGNFET是SOI器件,徹底消除了前邊提到的中間電位N阱(P_BIAS)收集電子的問題。還有其他小的修改,限于篇幅請自行閱讀論文。

Fig9. 第二版3.3V RC-CLAMP

3 Consideration anddiscussion

RC-CLAMP中的RC常數及管子尺寸該如何選取?這里提到的EGNCAP是一種varactor電容,不同于傳統MOS電容,其C-V曲線呈單調變化,什么地方會用到它呢?

-

ESD保護

+關注

關注

0文章

449瀏覽量

27389 -

CDM

+關注

關注

0文章

30瀏覽量

12391 -

CMOS晶體管

+關注

關注

0文章

11瀏覽量

10287 -

GPIO

+關注

關注

16文章

1251瀏覽量

53459 -

寄生電阻

+關注

關注

1文章

20瀏覽量

2371

發布評論請先 登錄

評論