FIFO為什么不能正常工作?復(fù)位信號有效長度不夠,接口時序不匹配,可看下面這篇文章。

本文將介紹:

非DFX工程如何確保異步FIFO自帶的set_max_delay生效?

DFX工程如何確保異步FIFO自帶的set_max_delay生效?

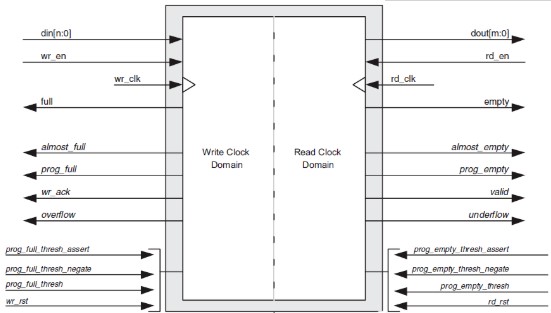

對于異步FIFO,復(fù)位信號的使用要特別注意,如下圖所示。復(fù)位信號必須和wr_clk同步,如果異步,要在wr_clk時鐘下同步釋放,否則會出現(xiàn)數(shù)據(jù)無法寫入FIFO的情形。

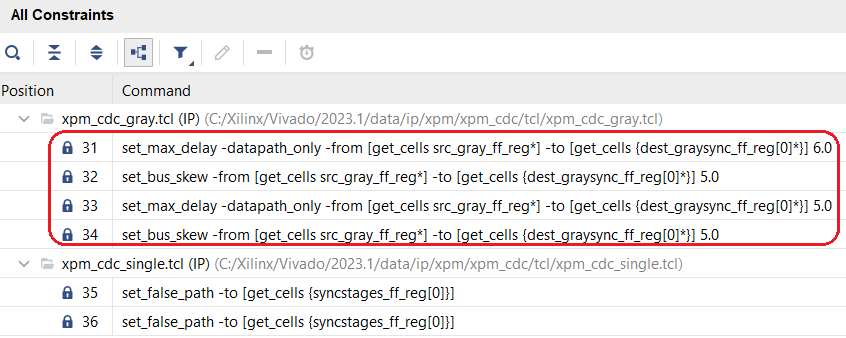

在FPGA設(shè)計中,我們會經(jīng)常用到異步FIFO進行跨時鐘域隔離。作為已經(jīng)非常成熟的設(shè)計,AMD提供了兩種使用方式:一種是使用IP,一種是使用XPM_FIFO。無論是使用哪種方式,都會生成自帶的約束,如下圖所示。可以看到使用了set_max_delay和set_bus_skew,這是因為異步FIFO的控制邏輯涉及到二進制碼和隔離碼的轉(zhuǎn)換,本質(zhì)上是讀/寫指針的跨時鐘域傳遞,這兩個約束正是針對這部分邏輯電路。

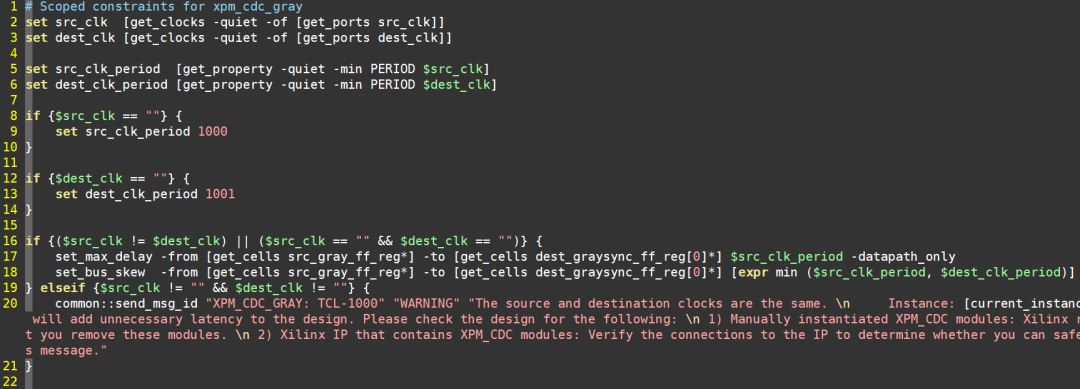

從上圖中還可以看到,圖中紅色方框標記的約束來自于xpm_cdc_gray.tcl文件。該文件可在Vivado安裝目錄下找到,這里我們給出該文件的部分內(nèi)容,如下圖所示。從圖中代碼第2行和第3行可以看到,該約束文件在執(zhí)行前需要獲取兩個時鐘src_clk和dest_clk,第5行和第6行則會分別獲取這兩個時鐘的時鐘周期。從這里我們可以判斷該文件是在用戶約束文件之后編譯的。

我們可以打開綜合后的設(shè)計,通過命令report_compile_order -constraints查看約束文件的編譯順序,會生成如下圖所示的報告,在其中的Processing_Order列可以看到用戶約束文件的值為NORMAL,而FIFO自帶約束文件的值為LATE,這就表明FIFO自帶約束文件是在用戶約束文件之后進行編譯的。原因就是FIFO自帶的約束文件依賴于用戶約束文件提供的時鐘周期。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613918 -

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

27129 -

fifo

+關(guān)注

關(guān)注

3文章

400瀏覽量

44602 -

時序

+關(guān)注

關(guān)注

5文章

397瀏覽量

37771 -

異步FIFO

+關(guān)注

關(guān)注

0文章

20瀏覽量

8512

原文標題:你的FIFO為什么不能正常工作?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

VIPM不能正常工作

不能從FIFO引腳獲得輸出數(shù)據(jù)

BurnRead函數(shù)不能正常工作

Slave fifo無法正常工作

ASCII不能正常工作

如何處理電腦不能正常關(guān)機故障

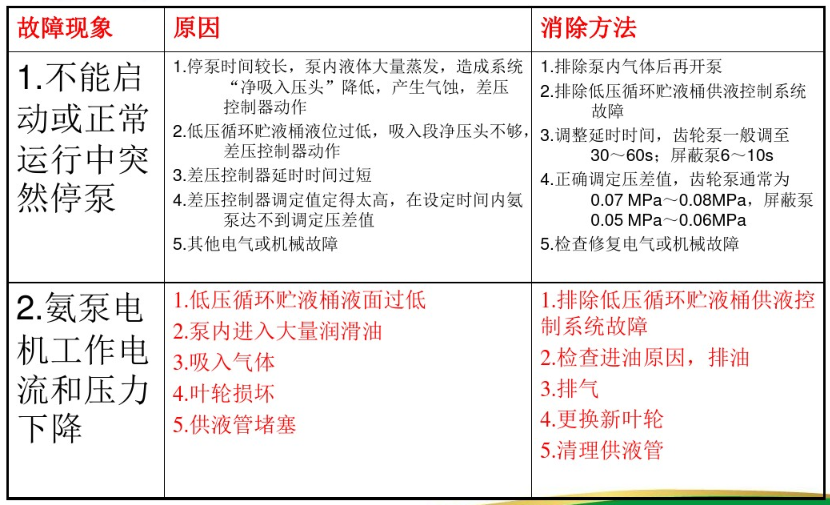

氨泵不能正常工作_風(fēng)機故障的現(xiàn)象及處理

單片機正常工作的三大條件

為什么有時候FIF不能正常工作?

IAR 的 Go to Definition of不能正常使用

同步FIFO和異步FIFO區(qū)別介紹

評論