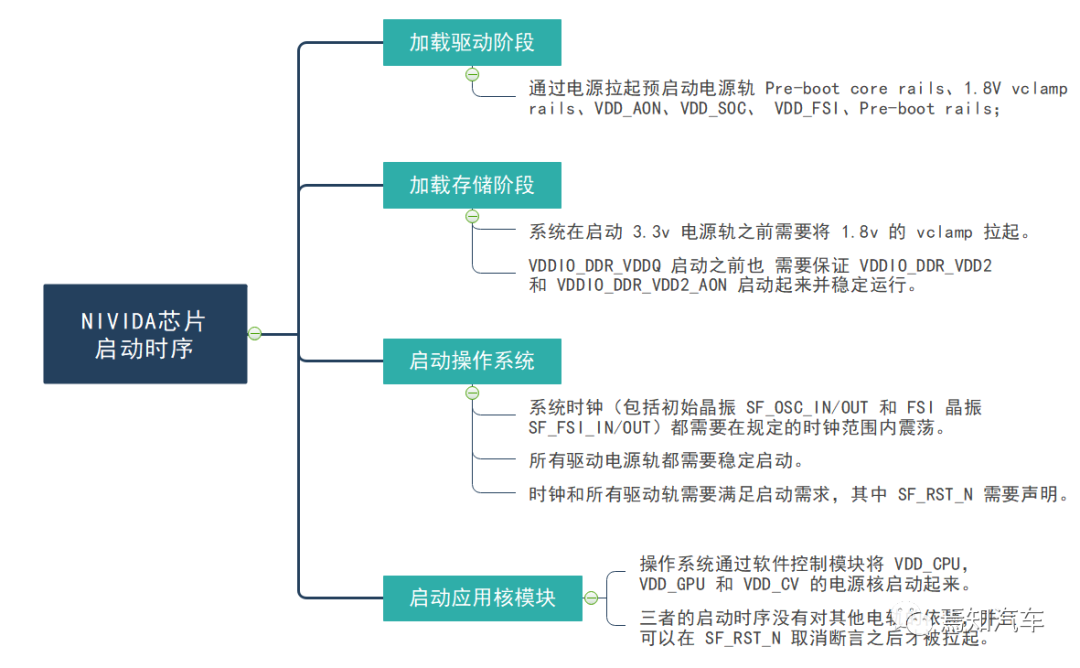

本文所闡述的整個狀態定義還處于頂層狀態,也不能表征 Orin 系列內部的所有狀態細節和事件。Orin系列芯片啟動 ROM 執行并最終通過控制到系統依賴的軟件。整個 Orin 啟動分為加載驅動、加載存儲、啟動操作系統、調用應用核模塊幾個大方向。

如下圖所示,各時序圖所表示的整個 SOC 芯片啟動時序。

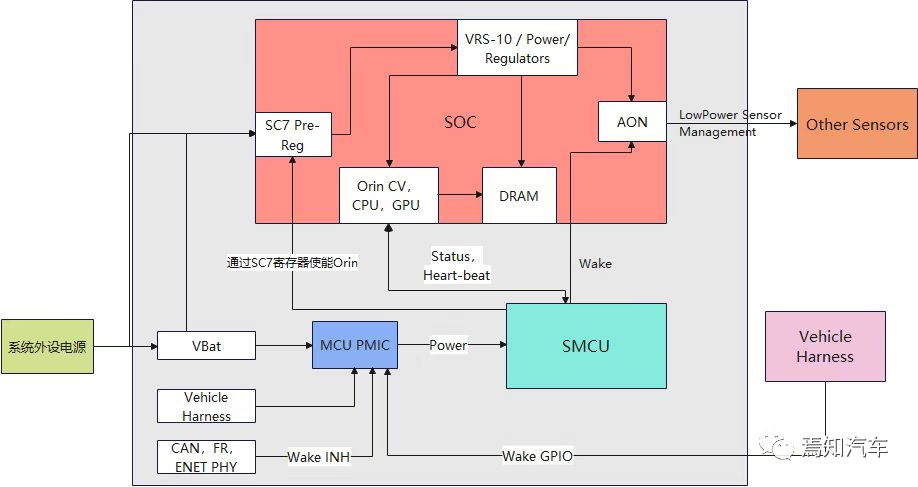

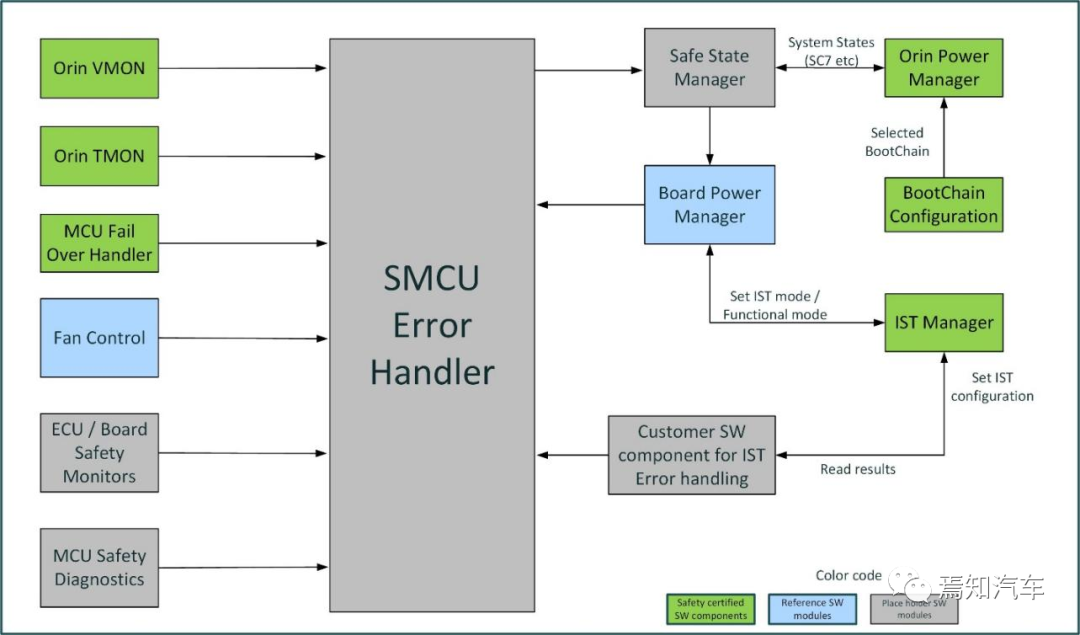

通常,Orin 系列芯片所能實現的高階駕駛輔助系統架構通常需要引入單獨的 MCU 芯片對其規劃的執行指令做執行仲裁,其他系統電源軌由SMCU進行監控。這樣不僅可以提升相應的安全等級,也是作為低電壓控制的關鍵策略。在Orin功能安全島中可以運行OEM跟功能安全相關的算法,如車控算法、比對算法、傳感器后融合算法等。通過運行Safety框架,對Orin芯片對Orin系列芯片和Drive OS軟件進行監控。

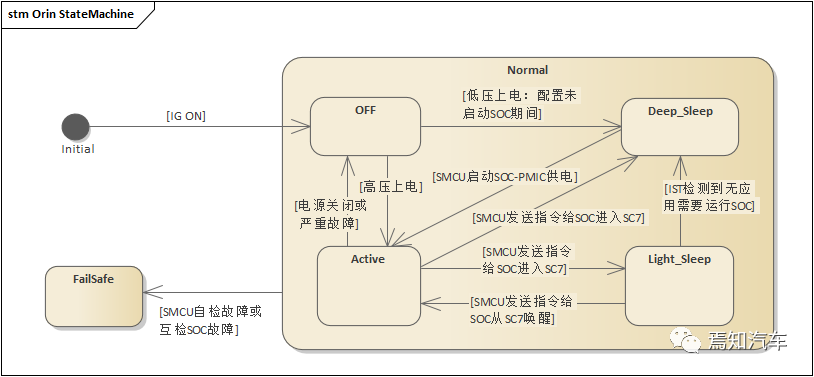

Orin系列芯片支持各種電源狀態包含Active(SC0)、Deep Sleep(SC7)、OFF SC7 電源狀態,同時也被稱為掛起到存儲狀態,這種設置是在用于從深度睡眠(SC7)狀態到激活(Active)的快速重啟中,SC7 在這種狀態下一直處于低電量消耗的睡眠狀態。

不僅 SC7 進入和退出需要專門的電源供給時序,同時也需要操作系統(這里指英偉達專門的操作系統 Drive OS)支持從掛起狀態中重啟。這個過程涉及兩個子過程“Suspend-to-Memory” (即懸置到存儲態),再從“Memory-to-Resume”(從存儲態到重啟)。這里的存儲(memory) 單元實際就是系統的動態隨機存取內存(DRAM)。

英偉達系列芯片的功耗模式主要有四種電源狀態,且這四種狀態之間可以進行有效的狀態跳轉。

如下表表示了典型的電源轉換表。

| 電源狀態 | Orin PMIC狀態 | MCU PMIC狀態 | 使用場景 |

| OFF | OFF SC7 | OFF | 系統關閉(KL30 未連接上) |

| Deep_Sleep | Deep Sleep(SC7) | Standby | 深睡眠狀態,可通過 PHY 線、SC7 故障或者整車電源喚醒 |

| Light_Sleep | Deep Sleep(SC7) | ON | 待機狀態,可通過 PHY 或整車 電源(GPIO)喚醒 |

| Active | Active(SC0) | ON | 整個系統被開啟且具備完整 的功能(電源連接至 KL30) |

| FailSafe | FailSafe | FailSafe | MCU PMIC/Orin PMIC的失效模式狀態表示 當嚴重錯誤被檢測到 |

當然,如上的系統狀態是通過SYS_VIN_LV VRS_10/12 VDD和SYS_VIN_HV VRS_11/VDD進行同步監測的。

對于 Deep_Sleep和Light_Sleep兩種狀態,可以通過特定設置來決定 PHY 的電源狀態,他們可以選擇將自己的待機模式放在上面,也可以將完整的電源關閉。Tier1 或主機廠需求也可以決策如何通 過 PHY 線來進行喚醒。例如,如果整車線束的 GPIO 口可以用來作為喚醒源,則所有 PHY 可 以在Deep_Sleep和Light_Sleep狀態下完全關閉。

以上每個狀態之間還有中間狀態,可以被區分為 a、b 兩種子狀態,從 a 到 b 的兩種子狀態轉換會發生在 MCU 所連接的固件啟動沒有其他額外觸發事件的情況下,這些固件包括攝像頭的子系統和其他系統設備電源供給。當然,這些固件是可以通過 MCU 通過內部啟動模塊進行單獨啟停控制。當 MCU PMIC 或Orin PMIC出現嚴重錯誤時,系統將進入 FailSafe狀態,MCU 的整個電源狀態將被置位為故障狀態。

接下來將對Orin系列中的電源每個子模塊進行詳細說明。

1)AON(Always on Cluster)群集

可以提供所有可能的硬件特征用于支持低電壓傳感器管理和喚醒使用場景。這些集群指令包含一個 ARM Cortex-R5 的緊耦合內存的處理器核,可以支持周邊件(如時鐘、中斷控制器),不同的 I/O 控制端,路由邏輯。AON 模塊中的 Cortex-R5 處理器也可以被當做傳感器處理引擎(SPE)。

AON Cortex-R5 可以實現:

ARM V7-R ISA 完整指令集和數據緩存緊耦合存儲(TCM)接口用于局部 SRAM

向量中斷支持

64 位 AXI/32 位 AHB 初始化接口,可分別用于 DRAM 需求和 MMIO 需求

32 位 AHB 初始化接口可以用于 ARM 向量中斷控制器接入

AXI 目標接口用于 DMA 接入到局部 SRAM

2)SC7-深度睡眠

SC7 是用于在最低可能的電源輸入下來進行快速重啟。該狀態下所有 CPU 核被關閉,且大多數的 I/O 和內部模塊都被關閉了,軟件執行被掛起。系統狀態被保存在 DRAM 中,并且總是處于自更新模式。

芯片從淺睡眠轉移到深睡眠的狀態需要滿足如下條件:

凍結所有正在運行的應用

同步文件系統內容到存儲設備

掛起各自的設備驅動,保存 DRAM 中的其他狀態

將 DRAM 放到自刷新模式中

當需要在 SC 之前運行時,斷電序列也與系統內測試有關。

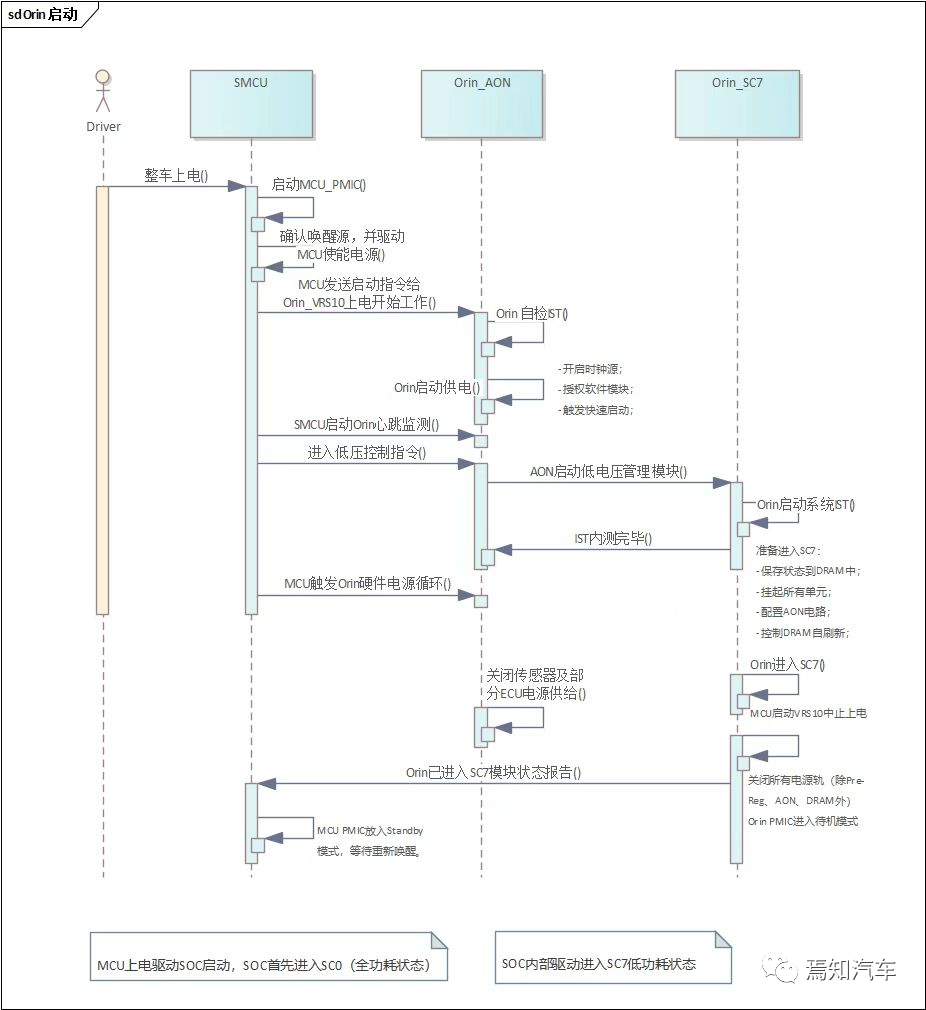

如下圖表示了整個系統進入和退出低功耗模式的電源啟動時序圖(其中,如下左圖表示 SC7 內側進入時序)。

進入退出低功耗時序圖

進入退出低功耗時序圖

對如上時序概括起來將,Orin-x 進入深度睡眠(SC7)實際是間斷性的關閉一些高功耗模塊。其中,包含如下完整的處理步驟:

首先,通過電源管理軟件模塊關閉最高功耗模塊:VDD_CPU、VDD_GPU 和 VDD_CV 電源軌, 從而為進入 SC7 深睡眠模式做準備;

其次,SC7 進入固件將 DRAM 置于自刷新過程中;

然后,SC7 進入前需要將固件配置時鐘節拍完成后才進入電源深度休眠狀態。在進入電源深度休眠前,軟件需要確保IO 狀態不會和任何其他平臺需求(比如拉高拉低需求,額外的元器件需求)相沖突,從而確保 IO 漏洞盡可能最小化;

Orin 芯片的使能端 SF_PWR_SOC_EN 被 PMC 固件和其中的電源軌會被逐步取消斷言;

平臺依賴 IO 電源軌和 PLL 電源軌將被選擇性的關閉;

兩個存儲控制端口 VDDIO_DDR_VDD2 和 VDD_DDR_VDDQ 電源軌將被關閉;

基于芯片正常電壓和特征參數而變化的邏輯軌 VDD_SOC 和功能安全控制電源軌 VDD_FSI 將 被關閉;

接下來是系統如何退出低功耗模式。

當系統斷電后,系統硬件會將電源和時鐘給到 Orin-x 芯片。注意可能有其他的系統層限制(比如 LPDDR5 存儲電源時序限制)出現。

整體上退出低功耗模式SC7是有整車傳遞過來的指令輸入。首先,需要完成包含MCU PMIC電源管理程序后,由MCU控制觸發SC7退出指令,同時控制VRS10開始正常上電工作,隨即Orin芯片開始進行自檢后控制退出SC7并開啟時鐘源、授權軟件模塊、觸發快速驅動,最后進入下一個待命狀態。MCU端則開始與Orin之間啟動對應的心跳監測。

3)系統內檢(IST)

Orin系列芯片會提供一種機制來檢測由系統內測(IST)所產生的永久的故障,IST 應該在 Orin-x 功能安全系統中使用期間被啟動。IST 需要以特定的規則來配置零部件的軟硬件。IST 可以配置來執行一個在單 Orin-x 或者 Orin-x 外加一個 dGPU 的模式組成智駕系統。整個錯誤(Failsafe)處理機制如下:

①當系統無錯誤時,標準的電源時序會通過特定的 I/O 端或總線(CAN/Flexray/Ethernet PHYs) 喚醒整個系統。這也包含啟動所有 SC7 斷電域,然后是支持從內存恢復的操作系統 DRIVE OS,以結束正在運行的活動狀態。其中,啟動的快慢取決于內存的自恢復能力。

②當 SC7 模塊失效或 Timeout 時會產生相應的失效時序,芯片內部錯誤、溫度異常導致的宕機、低壓/過壓等都是這些失效模式之一。整體來說,如果芯片處于失效狀態時,實際是首先喚醒 MCU 后,通過內部檢測機制確認是否進入 SC7 。已經 timeout 或故障時,需要控制 VRS-10 關閉所有的 SC7 電源軌,只留下喚醒 PHY 線處于低電壓供電狀態。MCU 最終會將PMIC 模塊至于待機狀態后將MCU 關閉。

此外,系統內測程序 ITS 還需要檢測 Orin 是否長期維持在低功耗狀態 SC7下,如果是,則系統將會退出該低功耗SC7模式。并且在下一個系統自檢過程中判斷是否有重新進入低功耗SC7模式的需求。

對于IST系統內側應用而言,NVIDIA Orin 專門配置了相應的IST管理器來實現如下一些功能子項:

①提供一個用于設置IST配置的接口。

將用戶應用程序設置的配置與NVIDIA DRIVE Orin通信? 以太網上的軟件(IST客戶端)(用于鑰匙打開/關閉Orin IST)。

②提供一個用于讀取IST結果的接口。

提供接口,平臺電源管理器可以使用這些接口查詢是否必須執行Keyon/KeyOff IST,并查詢IST是否已完成。

③在引導過程中,決定NVIDIA Orin應處于IST模式還是正常模式。

④通過GPIO斷言觸發IST,監控NVIDIA Orin上IST的執行,并通過超時檢測IST卡住的場景。

⑤提供一個中止IST執行的接口。

⑥檢測并處理以下硬件錯誤情況。

在某些情況下,IST的執行會受阻,且該阻塞會由基于GPT的硬件計時器檢測到,該計時器具有可配置的超時。與 DRIVE Orin的通信? SoC由具有可配置超時的軟件計時器進行監控。這取決于MCU和Orin之間的活動以太網(VLAN200)連接。客戶應用程序應使用NvMCU_ISTManager提供的接口,在每個電源循環期間設置有效的IST配置。這是使用串行控制臺外殼命令完成的。

總結

本文從芯片內部到芯片外部詳細分析了整個芯片工作的啟動時序流程、狀態跳轉、系統監控能力等。相對于單SOC芯片啟動而言,基于SOC+MCU的自動駕駛系統架構可更好的利用兩芯片各自的優勢進行互補,同時其按照基礎的驅動原理也可以由SMCU很好的對整個電源管理和啟動時序進行管控和監測。考慮Orin系列芯片在后續智駕系統的不斷深入應用,這些前期的設計分析過程必將成為后期系統架構和硬件架構設計中不可或缺的一環。

審核編輯:劉清

-

傳感器

+關注

關注

2552文章

51341瀏覽量

755518 -

ROM

+關注

關注

4文章

575瀏覽量

85882 -

SoC芯片

+關注

關注

1文章

616瀏覽量

34982 -

英偉達

+關注

關注

22文章

3827瀏覽量

91609 -

自動駕駛

+關注

關注

784文章

13910瀏覽量

166760

原文標題:利用英偉達系列芯片設計的高階自動駕駛的系統啟動時序

文章出處:【微信號:阿寶1990,微信公眾號:阿寶1990】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英偉達系列芯片設計的高階自動駕駛系統啟動時序流程

英偉達系列芯片設計的高階自動駕駛系統啟動時序流程

評論