DSK-PCIE系列高速夾具

PCI Express(PCIe)技術是服務器中最重要的高速串行總線。由于其高帶寬和低延遲特性,PCI Express架構廣泛應用于各種服務器互連場景,包括:

服務器內部:CPU與GPU的連接,CPU與網絡接口卡的連接,CPU與加速器的連接,CPU與SSD的連接。

機架內部:通過板對板連接器或電纜,CPU與JBOG及JBOF的連接新興GPU與GPU或加速器與加速器的互連。

與此同時,隨著異構計算的快速發展,服務器系統中的數據吞吐量要求越來越高。在發布PCIe4.0規范兩年后,PCIe5.0規范于2019年5月正式發布。PCIe5.0技術仍然使用相同的128b/ 130b編碼方案,符號速率從16GT/s增加到32GT/s。為了遵循傳統,PCIe5.0規范與低速度PCIe世代兼容。

PCIe Gen5的設計要求主要來源于: 《PCI Express Base Specification Revision 5.0, Version 1.0》 《PCIe_CEM_SPEC_R5_V0.9_11092020_NCB》 其中,Base主要針對芯片端的定義,CEM針對系統端及Add in Card。如果做系統端的設計,兩份定義需要結合著使用。

Base_SPEC

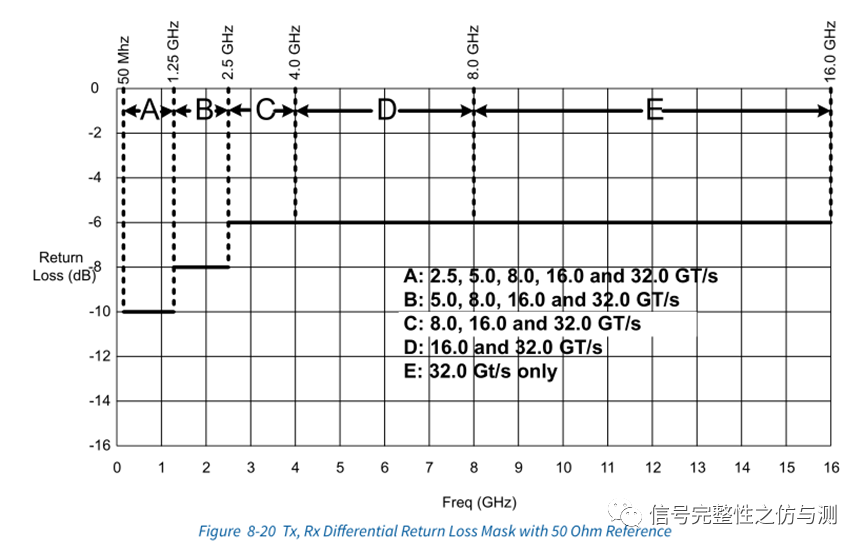

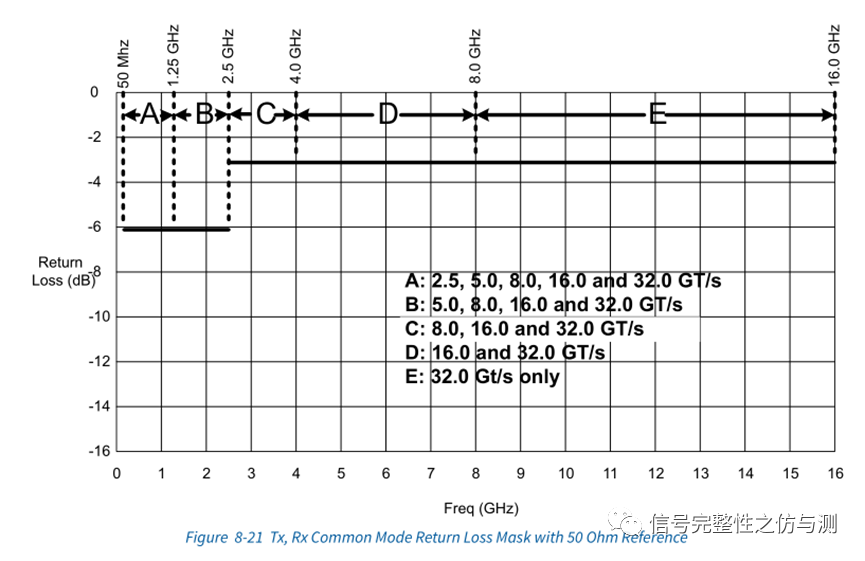

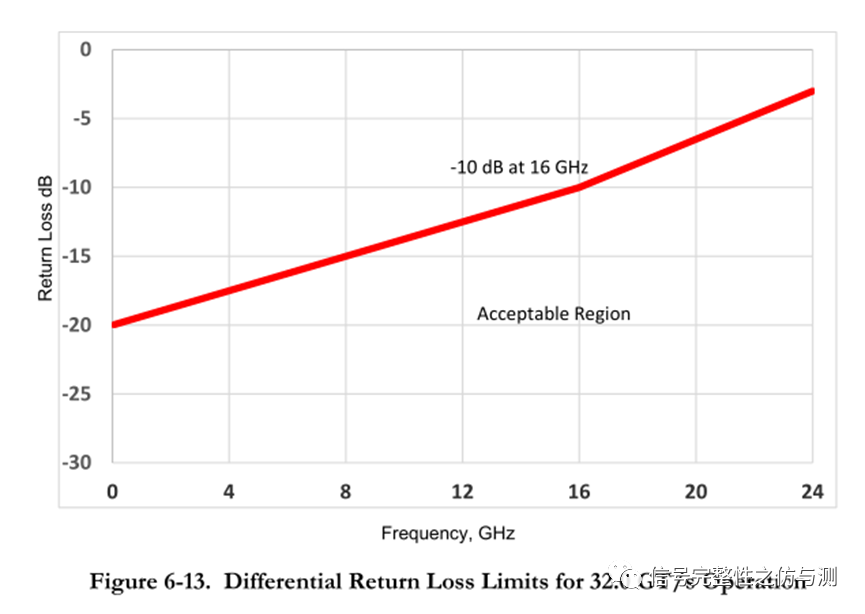

規范里面給的是回損指標,設計時要注意整個鏈路的阻抗一致性。

時域要求:

眼圖模板

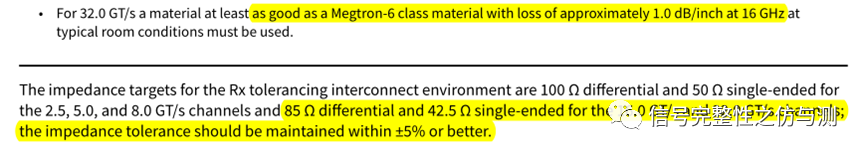

阻抗和材料要求

規范中的這段話顯示了在PCIE1.0 2.0 3.0中我們采用的單線50歐姆,差分100歐姆,但是到了PCIE 4.0 5.0我們就采用了單線42.5歐姆,差分85歐姆。而且要特別注意一點,阻抗公差控制不是在+-10%,要求最好在+-5%,保證PCB阻抗的平滑。

要注意的是,規范中說的分別是芯片的測試板和校準通道才需要控制阻抗+-5%,網上很多地方就認為PCIe5.0系統設計的阻抗都需要控制到+-5%,這明顯是一種誤導。要知道,對于一個大板,+-5%的阻抗控制PCB板廠要加不少錢都還不敢給你保證。PCIe5.0系統端設計按照85±10%的阻抗控制即可。

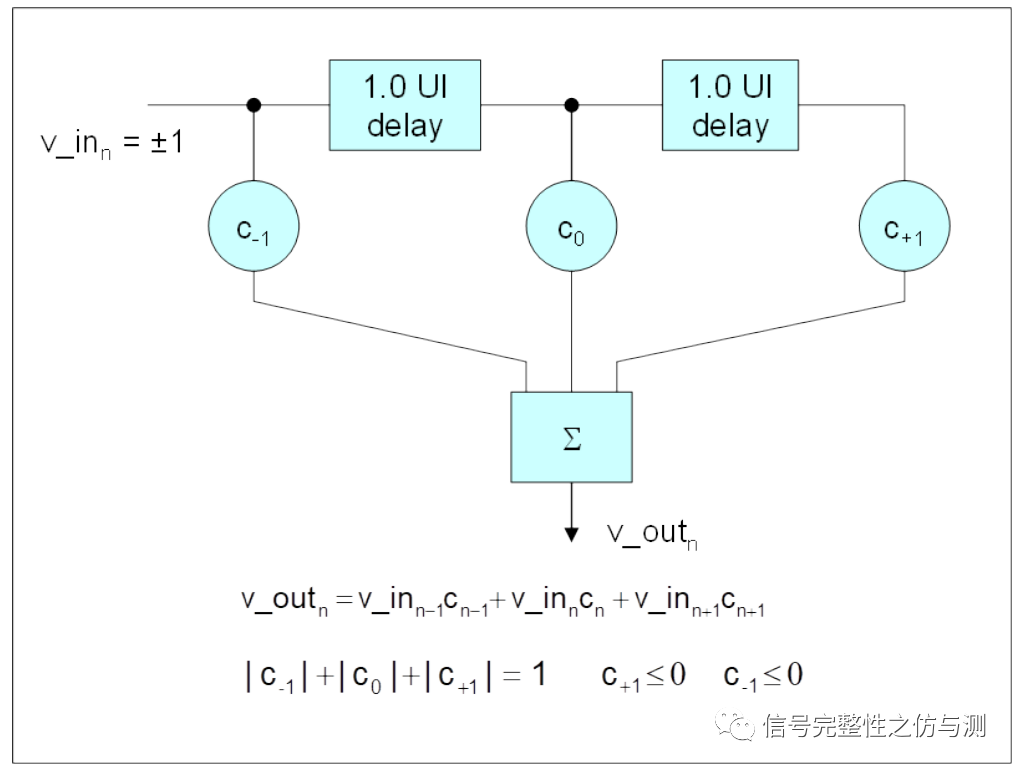

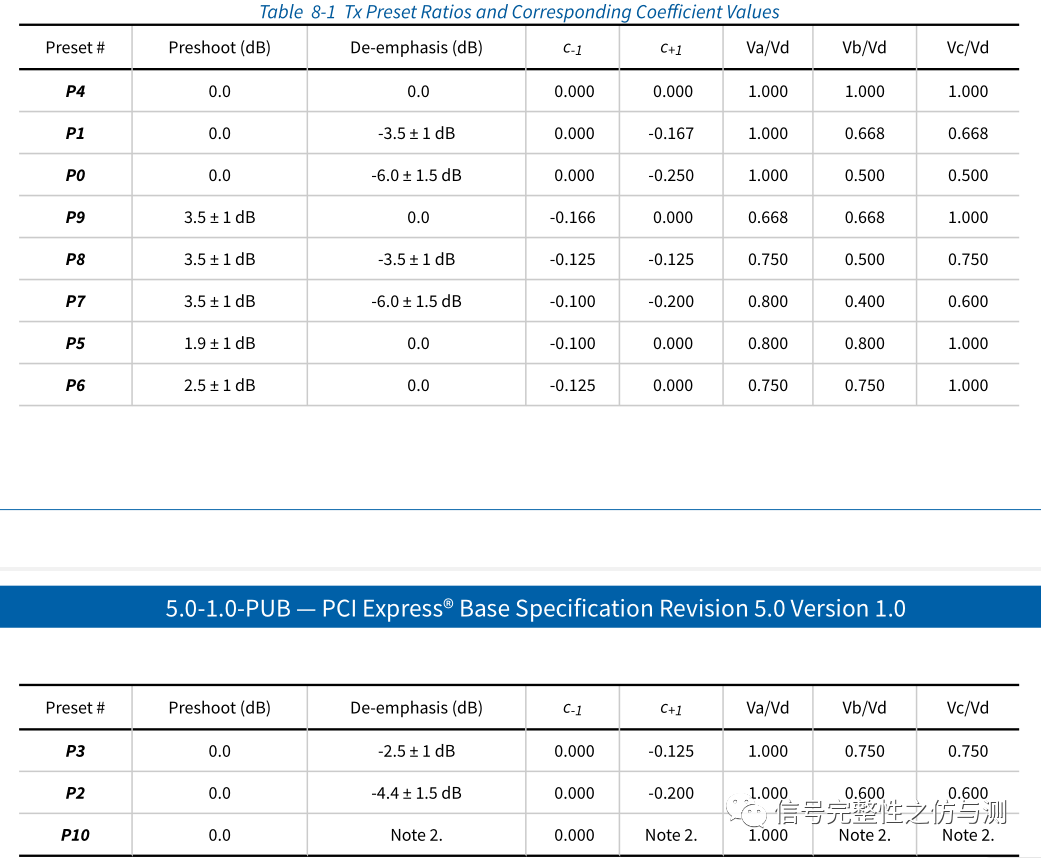

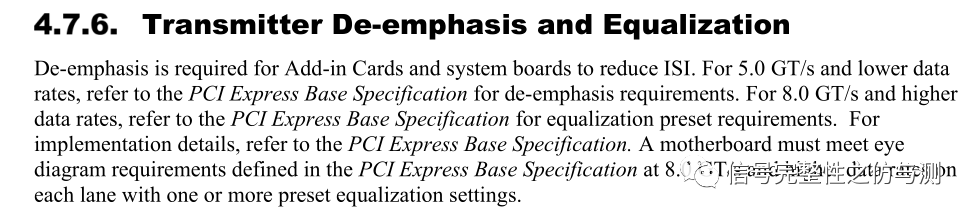

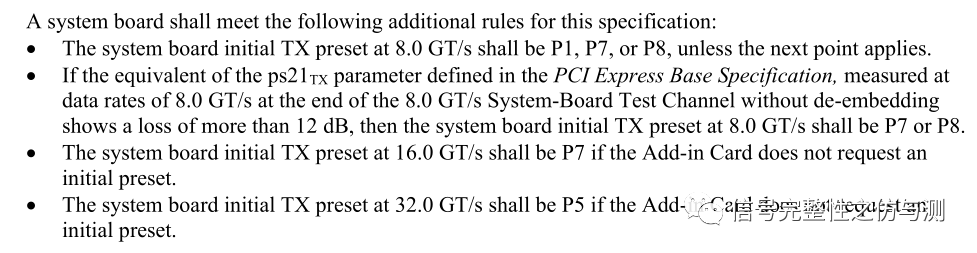

Tx Equalization Presets

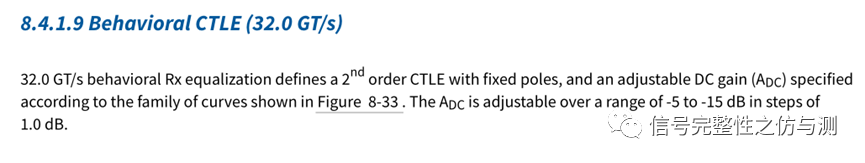

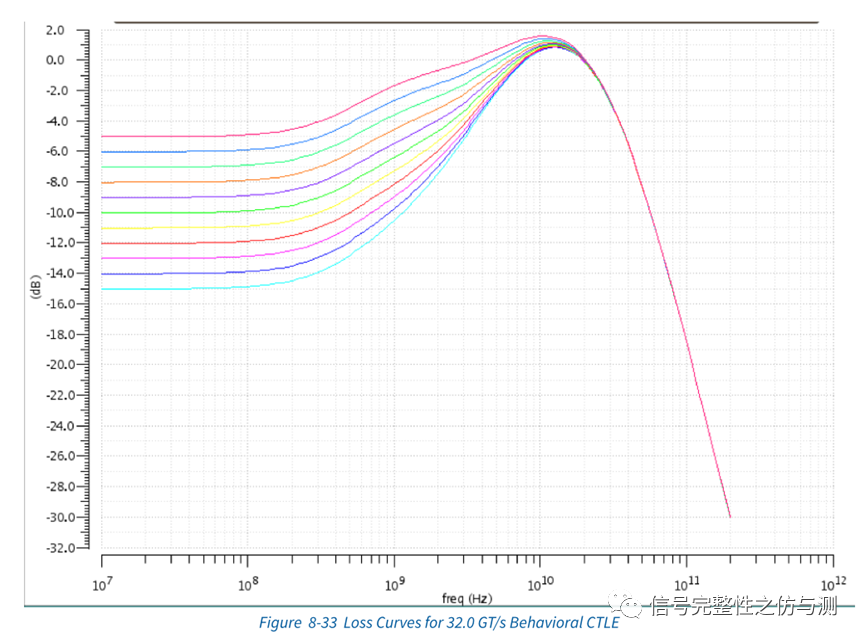

CTLE要求

32.0 GT/s速率下,Rx均衡定義了具有固定極點的二階CTLE,以及可調直流增益(ADC)。ADC可在-5到-15 dB的范圍內以1.0 dB為步長進行調整。

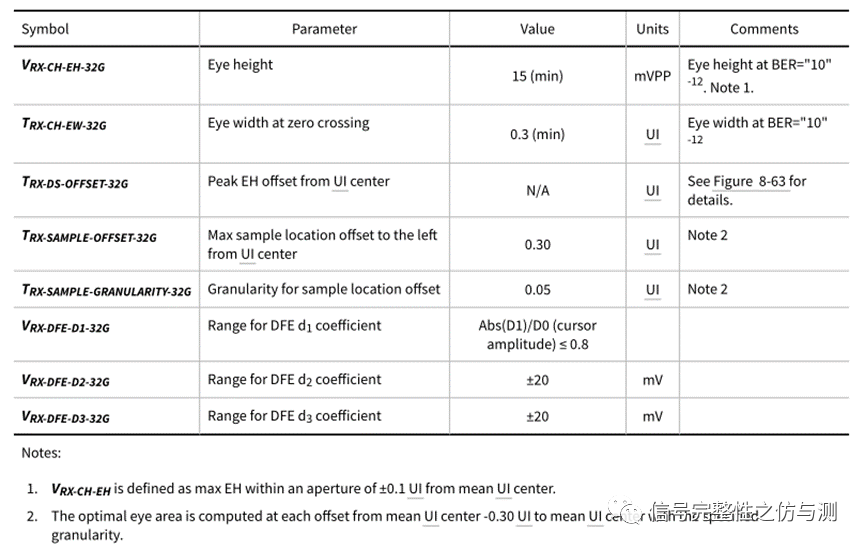

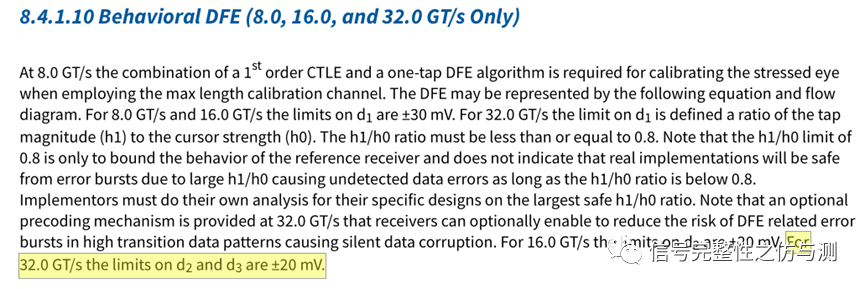

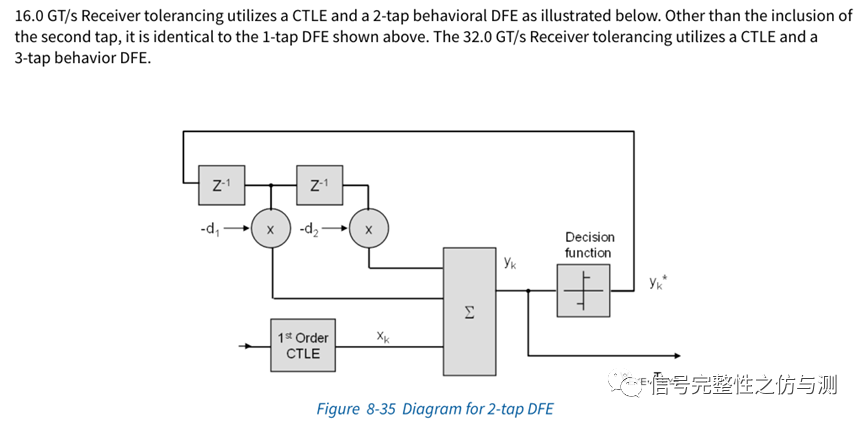

DFE要求

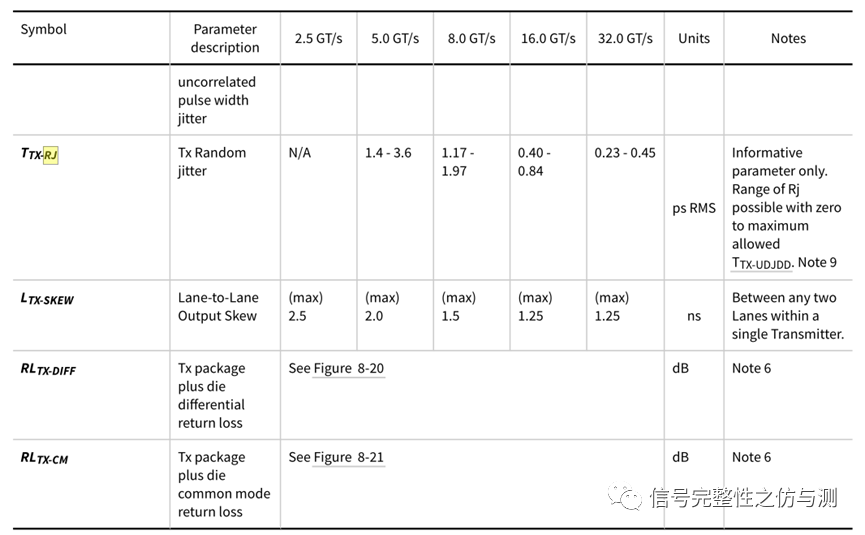

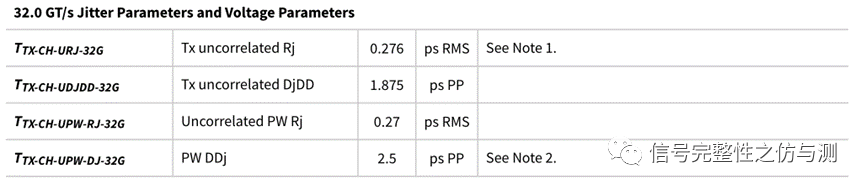

Rj要求

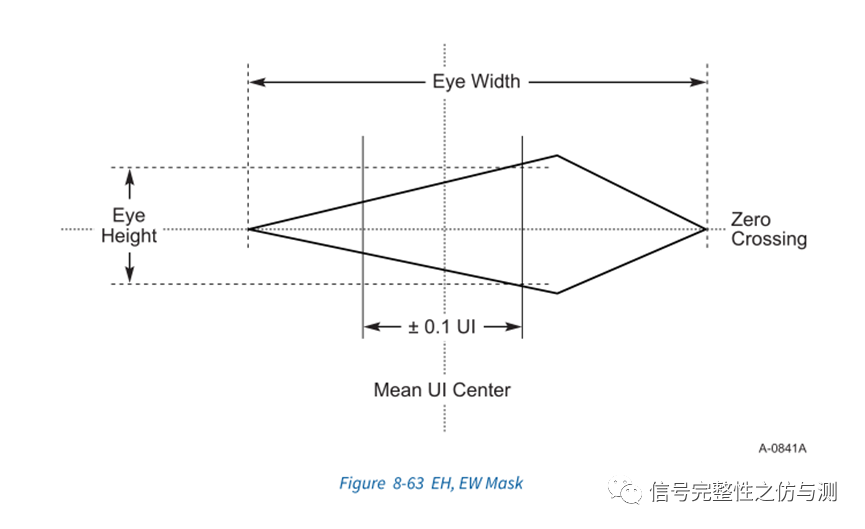

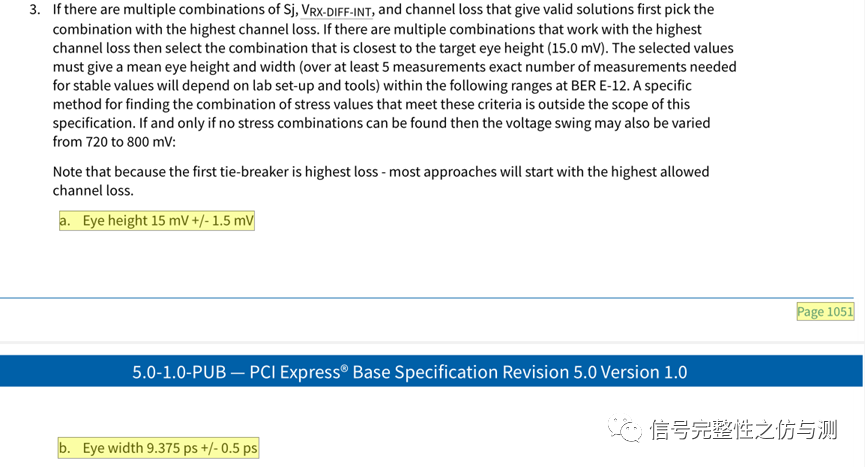

1E-12 BER眼圖要求

CEM_SPEC

均衡參考Base Spec

Preset預設值

Intra-pair Skew

4.7.7 Skew within the Differential Pair

The skew within the differential pair givesrise to a common-mode signal component, which can, in turn, increaseElectromagnetic Interference (EMI). Thedifferential pair shall be routed such that the skew within differential pairsis less than 0.064 mm (2.5 mil) for the Add-in Card and 0.127 mm (5 mil) forthe system board.

差分對內的偏斜會產生共模信號分量,從而增加電磁干擾(EMI)。差分對的布線應確保差分對內的偏斜對于插件卡小于0.064 mm(2.5 mil),對于系統板小于0.127 mm(5 mil)。

4.7.8 Differential Data Trace Impedance

The PCB trace pair differential impedancefor a 5.0 GT/s capable data pair must be in the range of 68 Ω to 105 Ω. The PCB trace pair differential impedance foran 8.0 GT/s capable data pair must be in the range of 70 Ω to 100 Ω. The PCBtrace pair differential impedance for 16.0 GT/s and higher data rate capabledata pair must be in the range of 72.5 Ω to 97.5 Ω. These limits apply to boththe Add-in Card and the system board.

具有5.0 GT/s功能的數據對的PCB差分阻抗必須在68Ω至105Ω的范圍內。8.0 GT/s數據對的PCB差分阻抗必須在70Ω至100Ω的范圍內。16.0GT/s和更高數據速率數據對的PCB差分阻抗必須在72.5Ω至97.5Ω的范圍內。這些限制適用于外接卡和系統板。

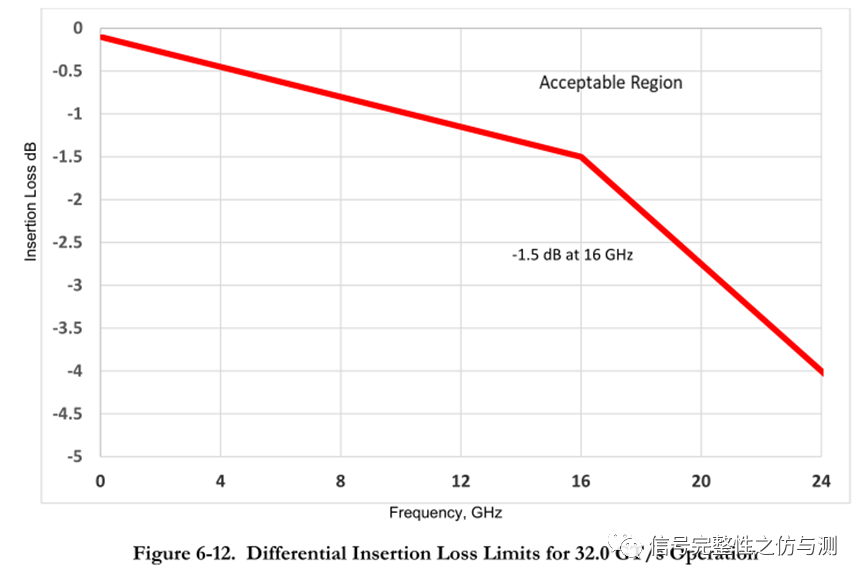

4.7.11 Add-in Card Insertion Loss Limit for 32.0 GT/s

The insertion loss from the top of theedge-finger to the silicon die pad must not exceed -9.5 dB at 16 GHz. This requirement applies to boththe transmitter and receiverinterconnect and the total loss includes PCB insertion loss, vias (if any), ACCapacitors (applicable to transmitter interconnect), and silicon packageincluding the effective die capacitance.

在16 GHz時,從金手指頂部到硅管芯片焊盤的插入損耗不得超過-9.5 dB。此要求適用于發送器和接收器互連,總損耗包括PCB插入損耗、過孔(如有)、AC電容器(適用于發送端互連)和包括有效硅芯片電容的封裝。

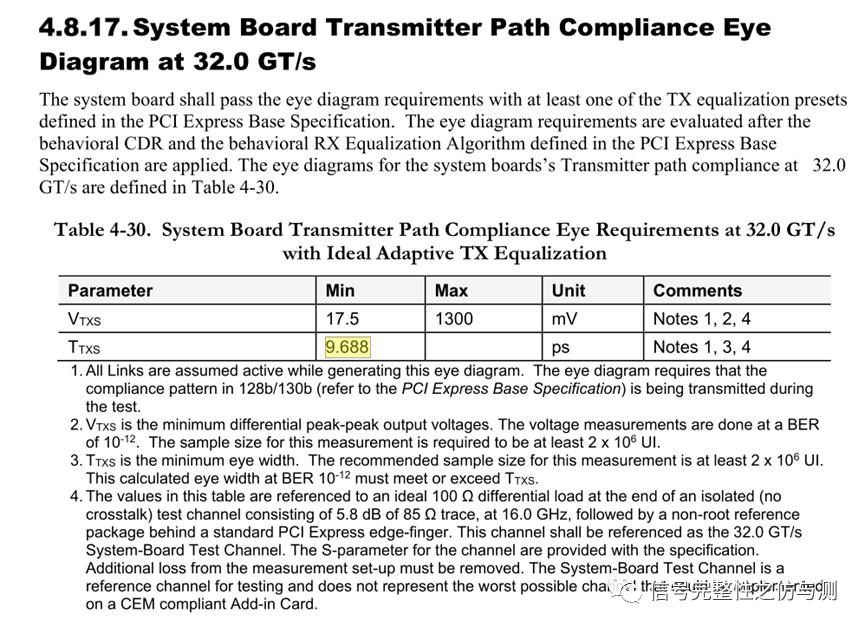

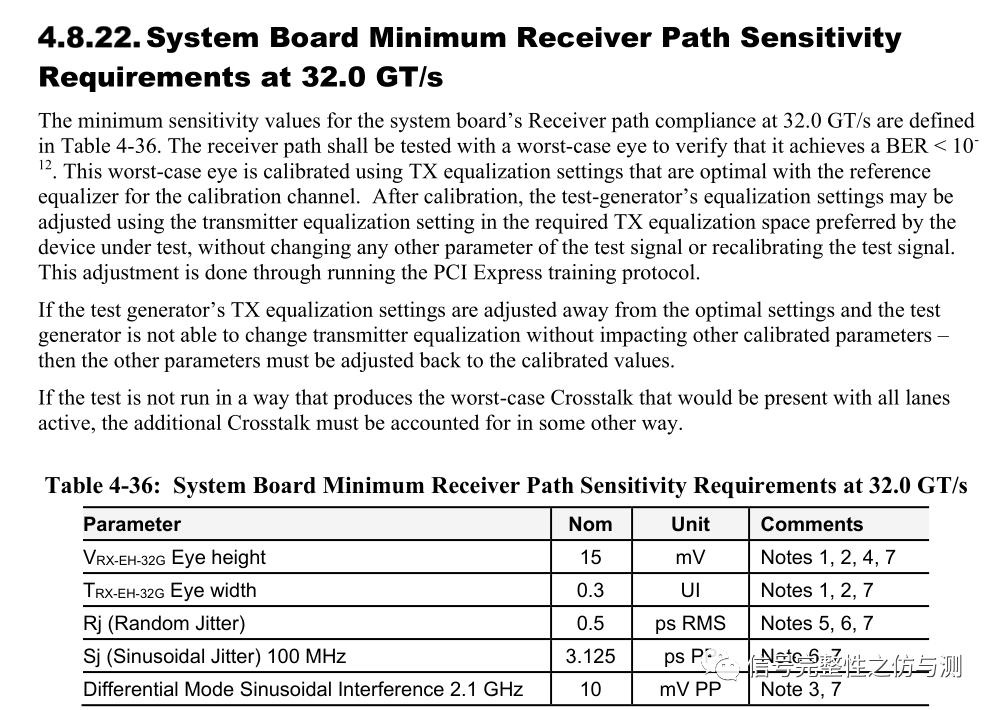

眼圖要求

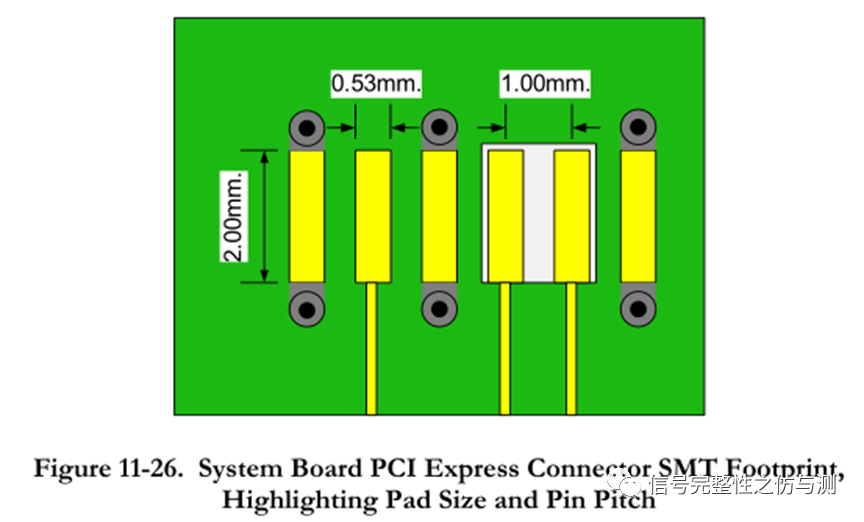

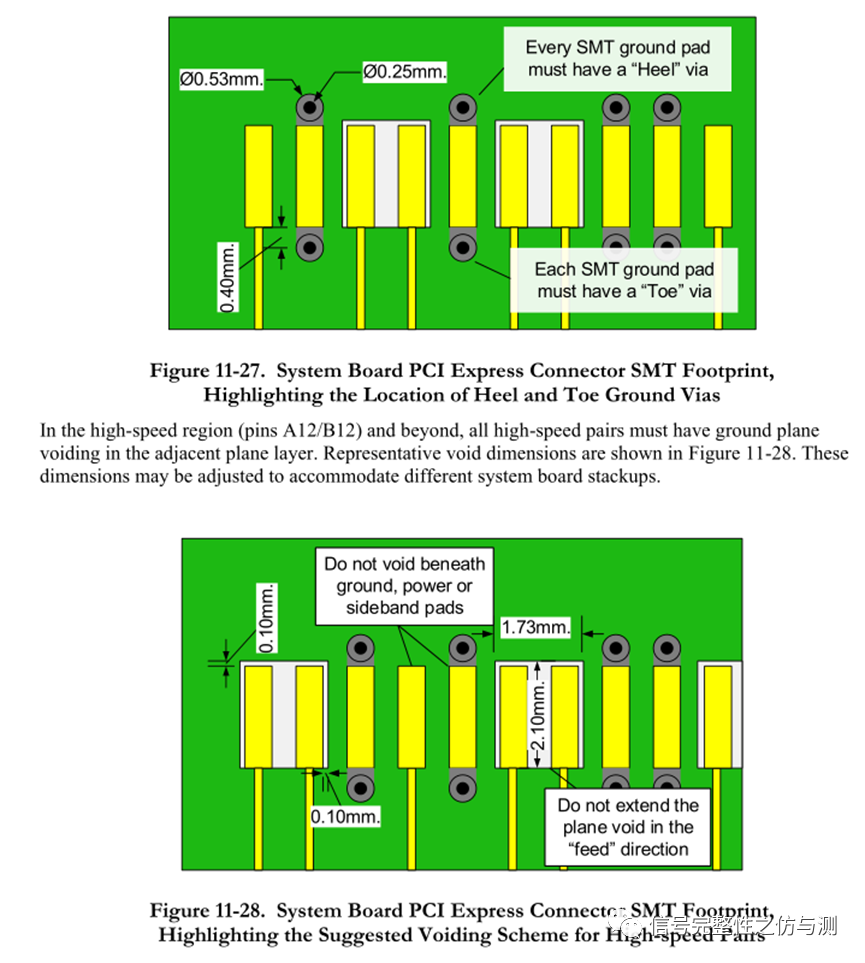

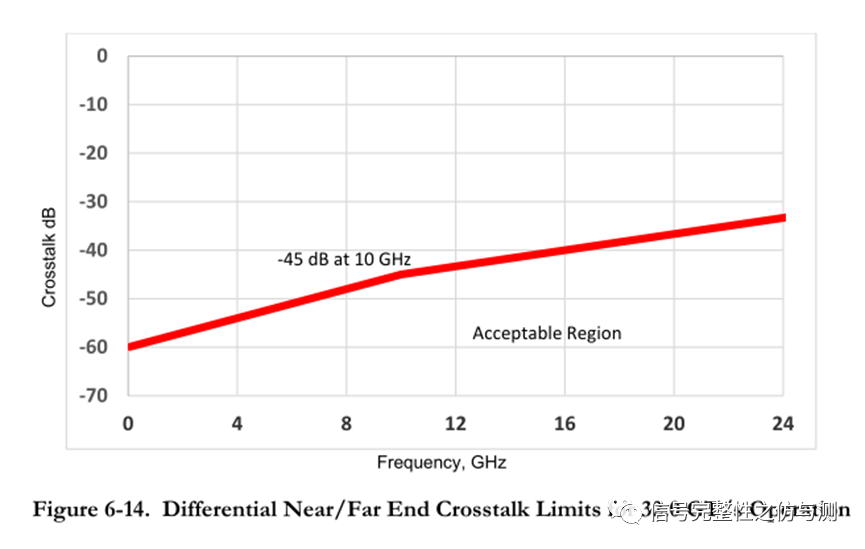

11.3.2 System Board Requirements for 32.0 GT/s Operation

Every system board that supports 32.0 GT/soperation must mount surface mount (SMT) PCI Express connectors. Through holeconnectors are only used at 16.0 GT/s and below. Surface mount connectors mayalso be used at data rates of 16.0 GT/s and below.

CEM 5.0 introduces the surface mountconnector footprint that has multiple updates and newrequirements. The pin field lies on a 1.0mm pitch, with pad dimensions of 0.53 x 2.00 mm.

每個支持32.0 GT/s的系統板都必須安裝表貼(SMT)PCI Express連接器。通孔連接器僅用于16.0 GT/s及以下。表貼連接器也可以以16.0GT/s及以下的數據速率使用。CEM 5.0引入了表貼連接器封裝,該封裝具有多項更新和新要求。引腳間距為1.0mm,焊盤尺寸為0.53 x 2.00 mm。

Connector需要滿足1.5dB損耗

PHY Test

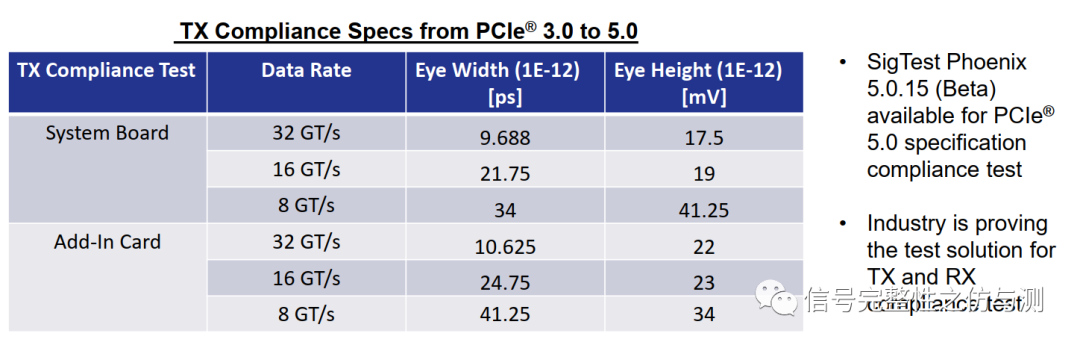

如果SigTest分析程序表明外推的眼睛寬度(在1e-12處)大于或等于9.688 ps,外推的眼睛高度(在1e處)大于等于17.5 mV,則測試通道的電氣符合性測試通過,否則測試失敗。如果測試失敗,則應選擇下一個Preset(通過按下順應性切換按鈕),并重復本測試程序,直到系統板通過其中一個Preset(預設0至預設9)已被測試。

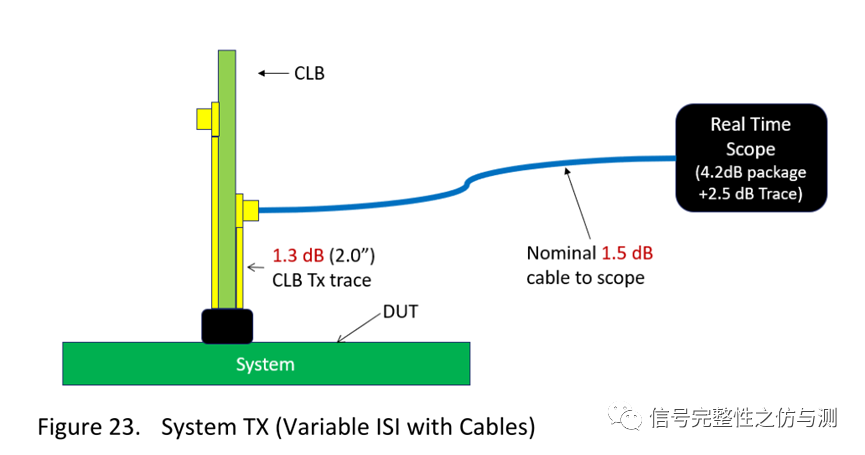

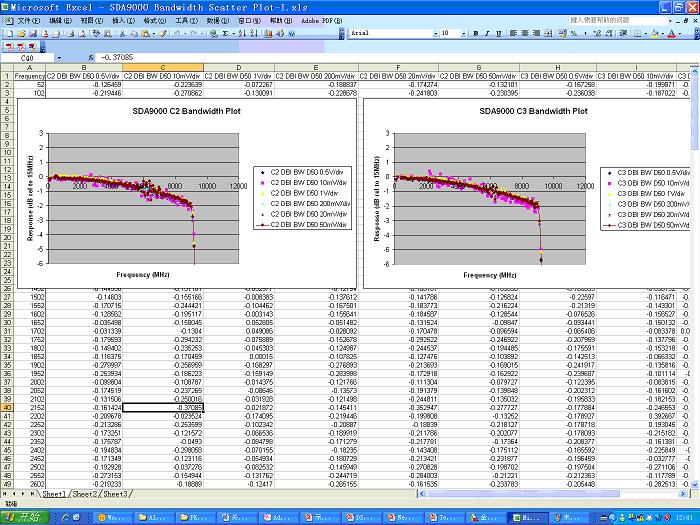

B.12 Target Loss Values –TX SignalQuality

Determine target loss and find correct s4pfile to embed in scope. A set of s4p files aredistributed with this specification. Theprocedure below outlines steps to select a specific s4pfile. Refer to the CEM 5.0 FixtureCharacterization spread sheet attached with this specification.

System TXsignal quality test

Target loss = 9.5 dB – (CLB Loss/Inch * CLBTX trace length)- 3 ft 2.92-MMPX cable loss.

See Figure 23 for measurement setup.

? From the available s4p files:

Insertion loss at 16 GHz: (5 dB, 5.5 dB, 6.0dB, 6.5 dB, 7.0 dB and 7.5dB), select one that matches closely to theTarget loss calculated above.

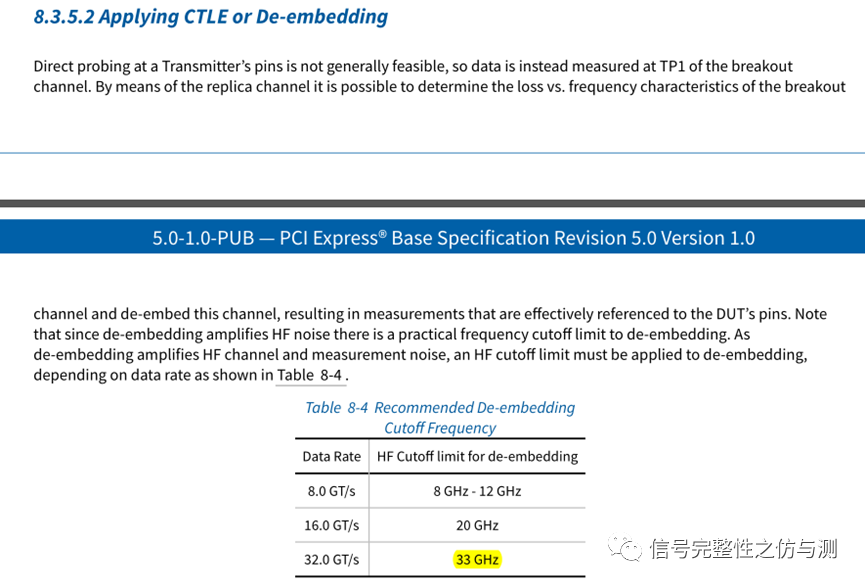

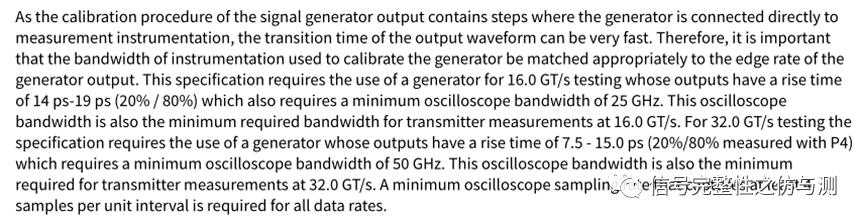

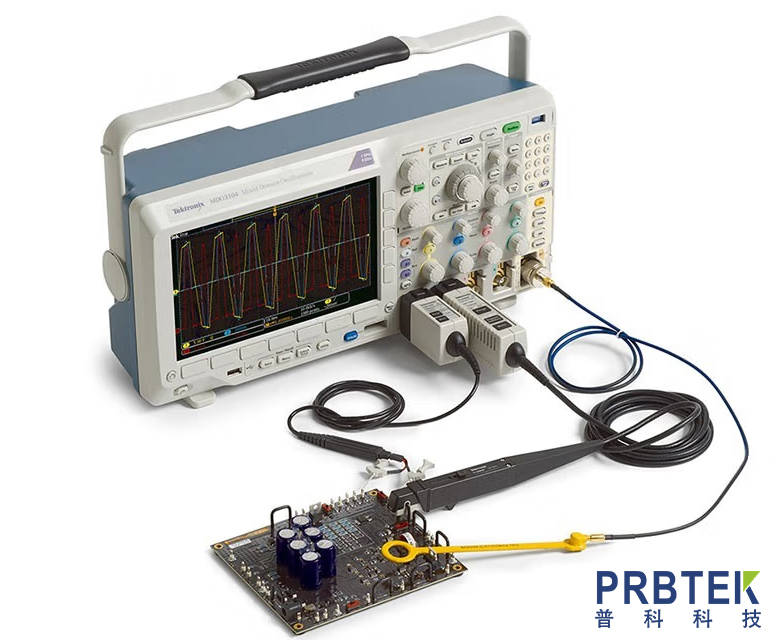

示波器帶寬要求

TX:33GHz RX:50GHz

PCIe 5.0 技術設計的挑戰

對于大于30 GT/s的其他標準,通常采用PAM-4調制方法,使得信號的奈奎斯特頻率等于數據速率的四分之一,但代價是9.5 dB的信噪比。然而,PCIe 5.0架構仍然采用非返回零(NRZ)信號傳輸方案,因此信號的奈奎斯特頻率等于數據速率的一半,即16 GHz。頻率越高,衰減越大。通道插入損耗(IL)引起的信號衰減是PCIe 5.0技術系統設計的最大挑戰。

PCIe 5.0規范為32 GT/s規定了36 dB的逐點插損允許范圍,并且誤碼率(BER)必須小于10-12。為了解決信號信號衰減的問題,PCIe 5.0規范定義了參考接收器,連續時間線性均衡器(CTLE)模型包括低至-15dB的ADC(可調直流增益),而16GT/s的參考接收器僅為-12dB。判決決策反饋均衡器(DFE)模型在32 GT/s下包含三階,而16GT/s下僅包含兩階。

此外,隨著數據傳輸速率達到32GT/s,串行鏈路上的錯誤可能性也變得更高。由于DFE電路在接收端的整體均衡中起著重要作用,與16GT/s相比,爆發性錯誤更有可能發生。為了應對這種風險,PCIe5.0架構引入了協議中的預編碼。在發送端啟用預編碼并在接收端進行解碼后,爆發性錯誤的機會大大減少,從而增強了PCIe5.0規范32GT/s鏈路的強健性。

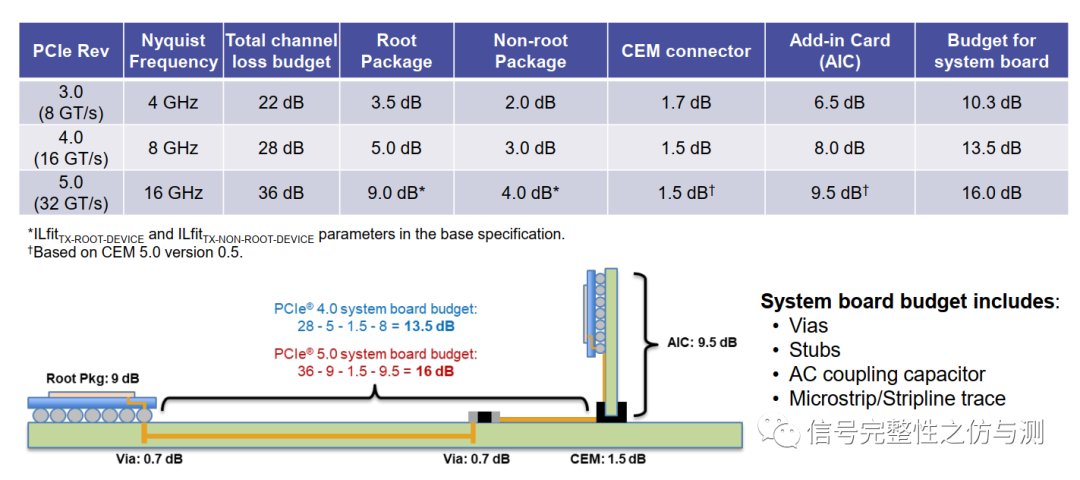

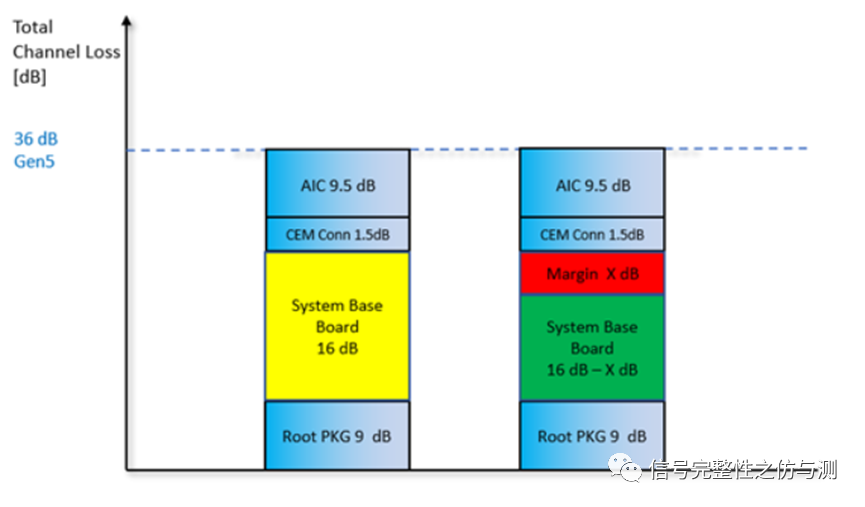

PCIe 5.0技術通道插入損耗預算

以典型的系統基板加上插卡(AIC)應用為例,比較PCIe 4.0架構(16GT/s)和PCIe 5.0架構(32 GT/s)的插入損耗預算。在32 GT/s的速率下,扣除CPU封裝的9 dB、AIC的9.5 dB和CEM連接器的1.5 dB后,系統基板的余量僅為16 dB。

然而,當考慮16-dB的系統基板預算時,還需要考慮以下因素:

1.隨著PCB溫度的升高,PCB線路的插入損耗也會增加。

2.在PCB制造過程中,工藝波動可能導致線寬稍微變窄或變寬,這可能導致插入損耗的波動。

3.柰奎斯特頻率信號(在32 GT/s NRZ信號傳輸中為16 GHz正弦波)在源端的幅度為800 mV峰峰值,經過36 dB的衰減后會降至約12.7 mV。這凸顯了在接收端留出一定的插入損耗余量的必要性,以考慮反射、串擾和電源噪聲等可能導致信噪比下降的因素。

因此,系統基板上的PCB走線所保留的IL預算應為16 dB,減去為上述因素所保留的一部分余量。許多硬件工程師和系統設計師傾向于將整體通道IL預算的10-20%保留為這些因素的余量。在36 dB的預算下,這相當于4-7 dB。

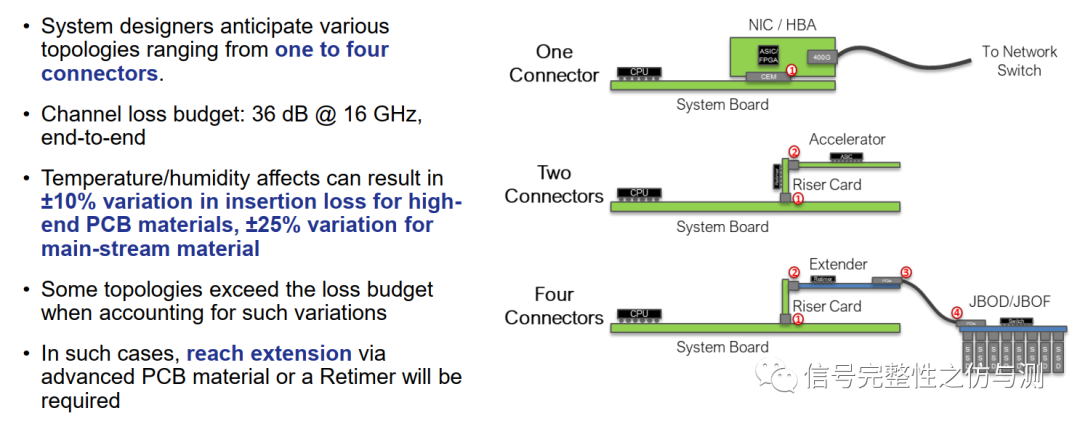

隨著對人工智能和機器學習的需求增加,PCIe 5.0技術將能夠實現更多的系統拓撲結構。從PCIe 4.0架構到PCIe 5.0架構的轉變將將通道IL預算從28 dB增加到36 dB,這將帶來新的設計挑戰。通過利用先進的PCB材料和/或PCIe 5.0中繼器來確保足夠的端到端設計余量,系統設計師可以確保平穩升級到PCIe 5.0架構。

審核編輯:湯梓紅

-

示波器

+關注

關注

113文章

6346瀏覽量

186658 -

gpu

+關注

關注

28文章

4832瀏覽量

129797 -

帶寬

+關注

關注

3文章

976瀏覽量

41268 -

信號完整性

+關注

關注

68文章

1418瀏覽量

95891 -

PCIe

+關注

關注

15文章

1284瀏覽量

83724

原文標題:示波器帶寬要求

文章出處:【微信號:si-list,微信公眾號:高頻高速研究中心】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

示波器帶寬要求解析

示波器帶寬要求解析

評論