01

先說“ 阻抗 ”和“ 阻抗匹配 ”的概念

電路中存在的電阻、電容和電感對電流起到的阻礙作用就叫做阻抗。阻抗的單位為歐姆(Ω),用Z來表示,是一個表達式為:Z=R+i(ωL–1/(ωC))的復數。實部R為電阻,虛部***(ωL–1/(ωC))為電抗,其中ωL***為感抗,***1/(ωC)***為容抗。

像我們平時接觸到的耳機、喇叭,它的一個重要的參數就是阻抗,準確的說是在1KHz的正弦波信號電路中耳機所呈現的阻抗值。主要是電阻和感抗,沒有容抗。

阻抗匹配是指信號源、傳輸線和負載之間達到一種適合的搭配關系,從而提升能源效益。

02

低頻電路中的阻抗匹配

在直流電路中也就是理想化的純電阻電路中,由電容和電感引起的電抗基本可以忽略不計,此時電路中的阻抗主要是來自于電阻。

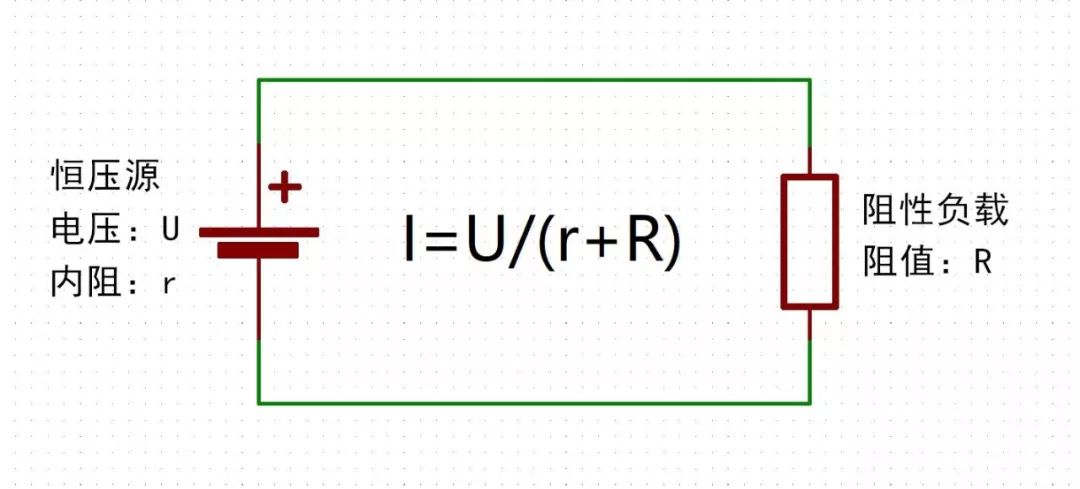

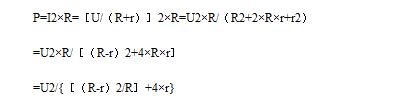

如下圖示,我們假設激勵源已定,那么負載的功率由兩者的阻抗匹配度決定。電路中的電流 I =U/(r+R),負載的功率P=**I**2R,我們整理得到P=(U2*R)/(r+R)2,**可以看出當R=r時負載的功率P最大=U2/4R。**

此結論在交流電路中引入容抗和感抗以后會稍有不同,在交流電路中負載的阻抗與信號源的阻抗共軛的時候能夠實現最大功率輸出。

在低頻電路中,我們一般不考慮傳輸線的匹配問題,只考慮信號源跟負載之間的阻抗匹配,因為低頻信號的波長相對于傳輸線來說很長,傳輸線可以看成是“短線”,反射可以不考慮,因為即使反射回來,跟原信號也是一樣的。

03

高頻電路中的阻抗匹配

我為什么把高頻電路單拉一個段落?因為在高頻電路中引入了一個非常重要的因素— 反射信號 。我們知道當信號頻率很高時,則信號的波長就很短。當波長和傳輸線長度同一量級時,反射信號疊加在原信號上將會改變原信號的形狀。

但是如果傳輸線的特征阻抗與負載阻抗相等(即阻抗匹配)時,就會有效的減少、消除高頻信號反射。

至于為什么阻抗不匹配會產生反射以及傳輸線的特征阻抗的算法,涉及到二階偏微分方程的求解,在這里我就不細說了,有興趣的朋友可以看一下高等教育出版社的教材《電磁場與電磁波》第四版的第七章<導型電磁波>的第6小結<傳輸線>,里面有詳細描述。

上面我們提到的傳輸線特征阻抗是一個很重要的概念,其數值只由傳輸線的結構和材料決定,與線的長度以及信號的頻率、幅值等無關。一些射頻設備所使用的同軸電纜的特征阻抗為50Ω,閉路電視的同軸線纜一般為75Ω。

如果阻抗不匹配那么不良后果有哪些呢?換句話說就是形成反射的不良后果,主要是會降低能量傳輸效率,形成駐波,導致傳輸線的有效功率容量降低。

如果是射頻設備的話就會影響信號傳輸距離、信號質量,甚至會損壞發射設備。如果是電路板上的高速信號線與負載阻抗不匹配時,就有可能產生震蕩、輻射干擾等。

04

阻抗匹配的應用場景

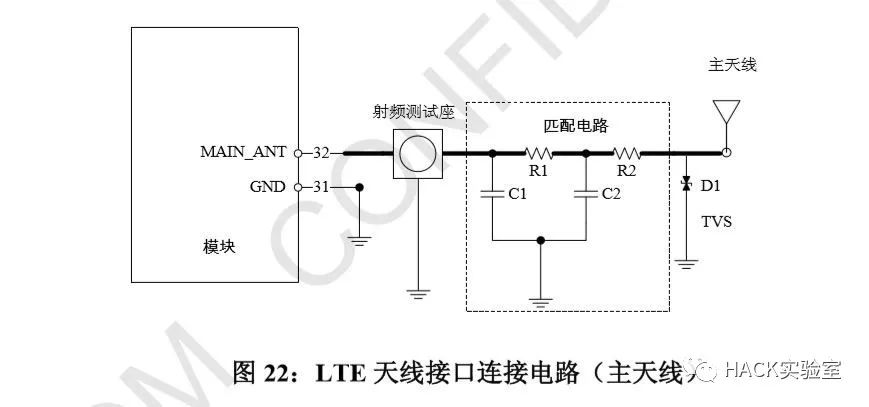

射頻天線部分的設計 ,這塊的要點在于天線和饋線間的阻抗匹配。發射信號時應使發射天線與饋線的特性阻抗相等,以獲得最好的信號增益。接收信號時天線與負載應做共軛匹配,接收機(負載)阻抗一般認為只有實數部分,因此需要用匹配網絡來除去天線的電抗部分并使它們的電阻部分相等。下圖為simcom公司的NB-IOT模塊天線部分的datasheet,使用網絡分析儀測量阻抗以確定R1、R2、 C1、C2的取值,完成阻抗匹配,可達到射頻最佳工作狀態。

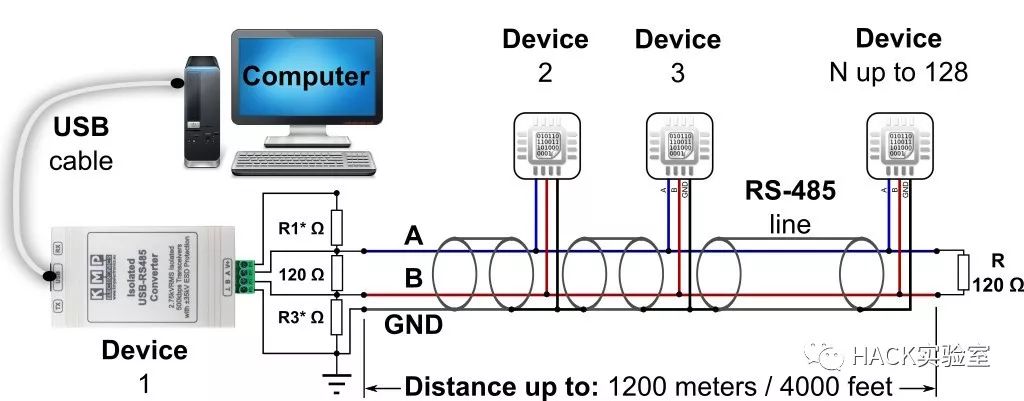

終端匹配電阻 ,在我們之前有一篇講485的文章中有詳細介紹,沒看過的小伙伴可以去閱讀一下,相信再結合本文會有一個更加深入的認知。雙絞線的特性阻抗一般為120Ω,若不加終端的電阻,當線纜長度很長而傳輸速率高即信號頻率高的時候就很容易發生我們上面所說的信號反射了。

PCB布線在低頻電路應用中基本可以不考慮阻抗匹配,但是在高頻電路中PCB走線的阻抗就需要重視了,一般在數字信號的邊沿時間小于1ns或模擬信號的頻率超過300MHz的時候我們就需要考慮走線的阻抗問題。

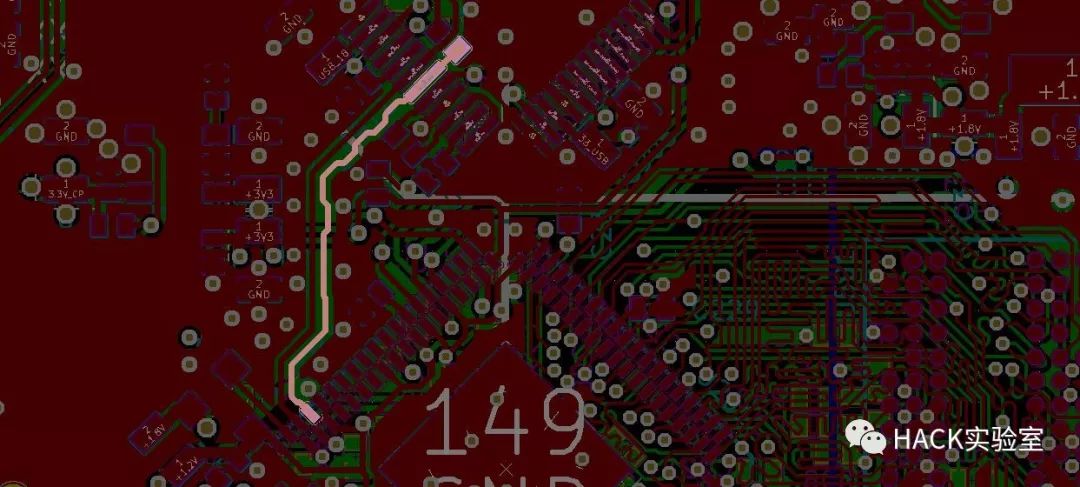

PCB走線阻抗主要來自寄生的電容、電阻、電感系數,主要因素有板厚、線寬、銅皮厚乃至過孔直徑等。PCB阻抗的范圍是 25 至120 歐姆,USB、HDMI、SATA等一般要做85~100Ω的阻抗控制。(下圖為之前設計的一款linux小主機的USB數據走線)

-

阻抗匹配

+關注

關注

14文章

353瀏覽量

30839 -

接收機

+關注

關注

8文章

1182瀏覽量

53529 -

PCB布線

+關注

關注

20文章

463瀏覽量

42080 -

寄生電容

+關注

關注

1文章

293瀏覽量

19266 -

傳輸線

+關注

關注

0文章

376瀏覽量

24049

發布評論請先 登錄

相關推薦

淺析阻抗匹配及其應用

什么是阻抗匹配原理?什么是負載阻抗匹配?

怎樣理解阻抗匹配_pcb阻抗匹配如何計算

如何理解阻抗匹配,阻抗變換?

說說“阻抗”和“阻抗匹配”的概念

說說“阻抗”和“阻抗匹配”的概念

評論