11 月 2 日-3 日,2023 國際集成電路展覽會暨研討會(IIC Shenzhen)在深圳成功舉行。會上,集成電路產(chǎn)業(yè)大咖聚集,共同洞見集成電路產(chǎn)業(yè)趨勢的風(fēng)向標(biāo)。

在中國 2023 全球 CEO 峰會上,Cadence 副總裁兼亞太區(qū)技術(shù)運(yùn)營總經(jīng)理陳敏發(fā)表了題為《泛 AI 加速——新時代的 EDA 進(jìn)化》的精彩演講,向與會者介紹了 AI 技術(shù)的發(fā)展現(xiàn)狀和未來趨勢,并分享了 Cadence AI 解決方案的特點(diǎn)和優(yōu)勢。

在隨后的 EDA/IP 與 IC 設(shè)計(jì)論壇上,Cadence 技術(shù)支持總監(jiān)李志勇也做了題為《適用大模型 Al 芯片的接口 IP》的精彩演講。

陳敏

泛 AI 加速——新時代的 EDA 進(jìn)化

在 IIC Shenzhen 的全球 CEO 峰會上,陳敏分享了 AI 技術(shù)發(fā)展所必不可少的高算力、高帶寬、低功耗半導(dǎo)體設(shè)計(jì)對 EDA 性能、效率的挑戰(zhàn),以及受益于 AI 技術(shù)的 EDA 在處理大數(shù)據(jù)量科學(xué)計(jì)算方面的機(jī)會,介紹了 Cadence 引領(lǐng)潮流的全棧 AI EDA 解決方案。

AI 技術(shù)的顛覆時刻已經(jīng)到來

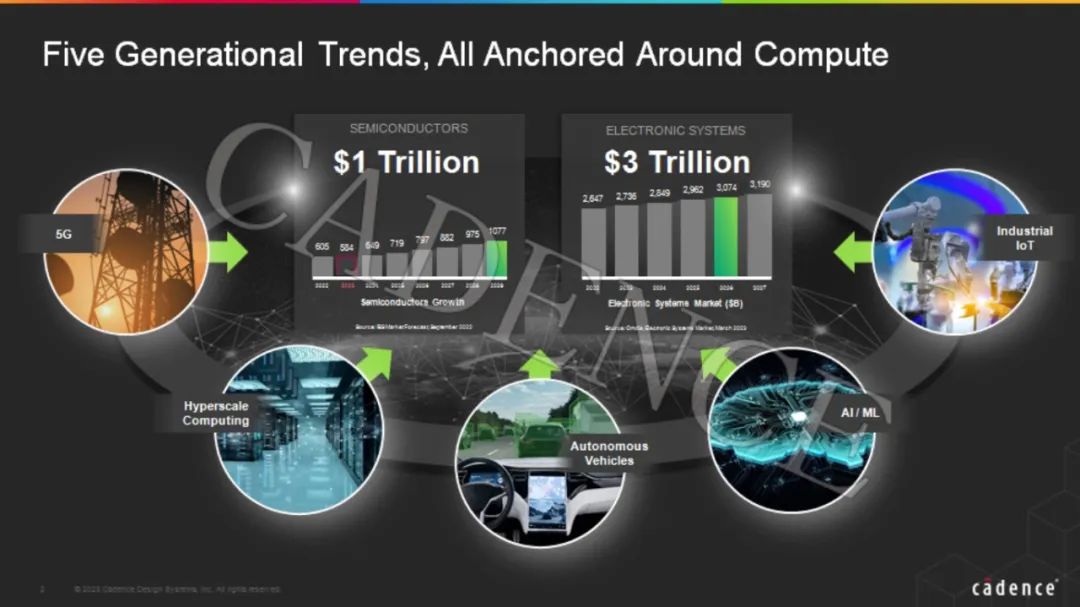

無處不在的 AI 正成為當(dāng)今世界最引人注目的話題之一。人工智能(AI)的廣泛應(yīng)用正在改變各個行業(yè)的運(yùn)作方式。EDA 行業(yè)也不例外,AI 的發(fā)展離不開高算力、高帶寬、低功耗的芯片,而此類芯片的設(shè)計(jì)對 EDA 的性能和效率也提出了更高的挑戰(zhàn)。反過來 EDA 作為處理大數(shù)據(jù)量的計(jì)算軟件,也天然受益于 AI 技術(shù)。 陳敏表示,從 5G 到云計(jì)算,再到物聯(lián)網(wǎng)的所有驅(qū)動力正在共同推動半導(dǎo)體行業(yè)的增長。預(yù)計(jì)在未來的 3 到 5 年,半導(dǎo)體市場規(guī)模將突破萬億美元,電子系統(tǒng)將達(dá)到 3 萬億美元。盡管短期的經(jīng)濟(jì)下行和地緣政治動蕩正在影響 2023 年的短期收入,但設(shè)計(jì)活動依然強(qiáng)勁,前景依然積極。

消費(fèi)者希望芯片具有更多的功能、更多的計(jì)算能力和更快的數(shù)據(jù)傳輸速度。這就使芯片復(fù)雜度越來越高,同時要設(shè)計(jì)的芯片種類也越來越多,這必將造成設(shè)計(jì)人員大量短缺。根據(jù)半導(dǎo)體行業(yè)協(xié)會數(shù)據(jù),2030 年設(shè)計(jì)工程師缺口將達(dá)到 35%。要解決人才短缺的挑戰(zhàn),一方面當(dāng)然是人才培養(yǎng),另一方面則是提高生產(chǎn)力。

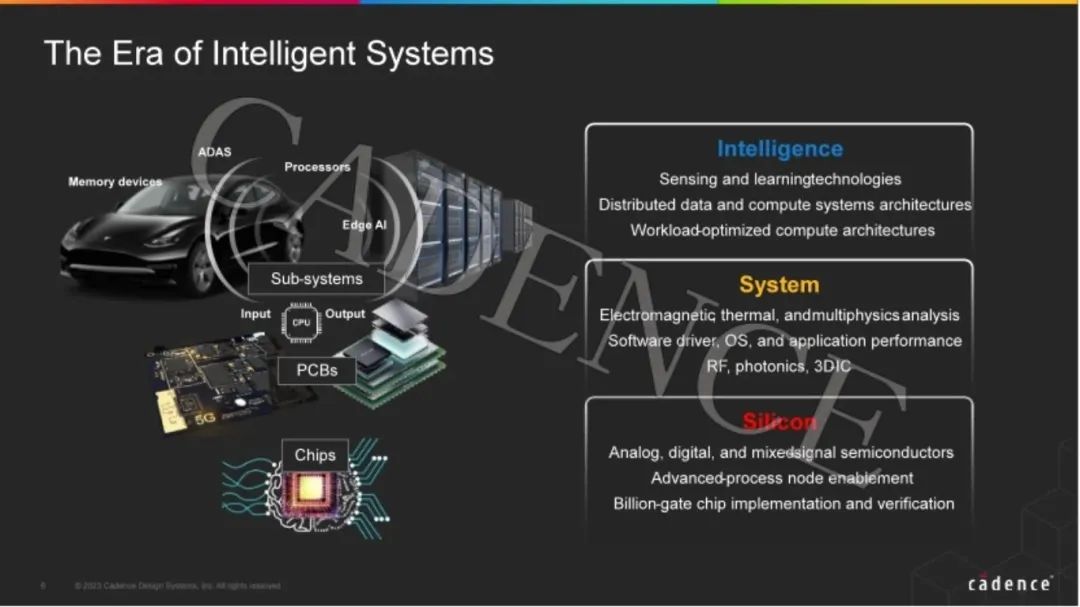

現(xiàn)在,全球每年制造數(shù)十億臺智能設(shè)備,預(yù)計(jì)到 2025 年,其潛在市場規(guī)模將達(dá)到 700 億美元左右。根據(jù)半導(dǎo)體行業(yè)協(xié)會的數(shù)據(jù),現(xiàn)代汽車可能擁有 8000 個或更多的半導(dǎo)體芯片和 100 多個電子控制單元,目前占車輛總成本的 35% 以上,預(yù)計(jì) 2025 年至 2030 年將超過 50%。

而設(shè)計(jì)這樣的智能系統(tǒng)對 EDA 提出了巨大的挑戰(zhàn),只有不斷提高生產(chǎn)力才能滿足設(shè)計(jì)需求。EDA 通過提升抽象層次,從晶體管級到單元級,再到 IP 的設(shè)計(jì)復(fù)用,以及現(xiàn)在基于 AI 的 EDA 或基于 AI 的自動化來提高生產(chǎn)力,同時有助于延續(xù)摩爾定律。

消費(fèi)者希望芯片具有更多的功能、更多的計(jì)算能力和更快的數(shù)據(jù)傳輸速度。這就使芯片復(fù)雜度越來越高,同時要設(shè)計(jì)的芯片種類也越來越多,這必將造成設(shè)計(jì)人員大量短缺。根據(jù)半導(dǎo)體行業(yè)協(xié)會數(shù)據(jù),2030 年設(shè)計(jì)工程師缺口將達(dá)到 35%。要解決人才短缺的挑戰(zhàn),一方面當(dāng)然是人才培養(yǎng),另一方面則是提高生產(chǎn)力。

現(xiàn)在,全球每年制造數(shù)十億臺智能設(shè)備,預(yù)計(jì)到 2025 年,其潛在市場規(guī)模將達(dá)到 700 億美元左右。根據(jù)半導(dǎo)體行業(yè)協(xié)會的數(shù)據(jù),現(xiàn)代汽車可能擁有 8000 個或更多的半導(dǎo)體芯片和 100 多個電子控制單元,目前占車輛總成本的 35% 以上,預(yù)計(jì) 2025 年至 2030 年將超過 50%。

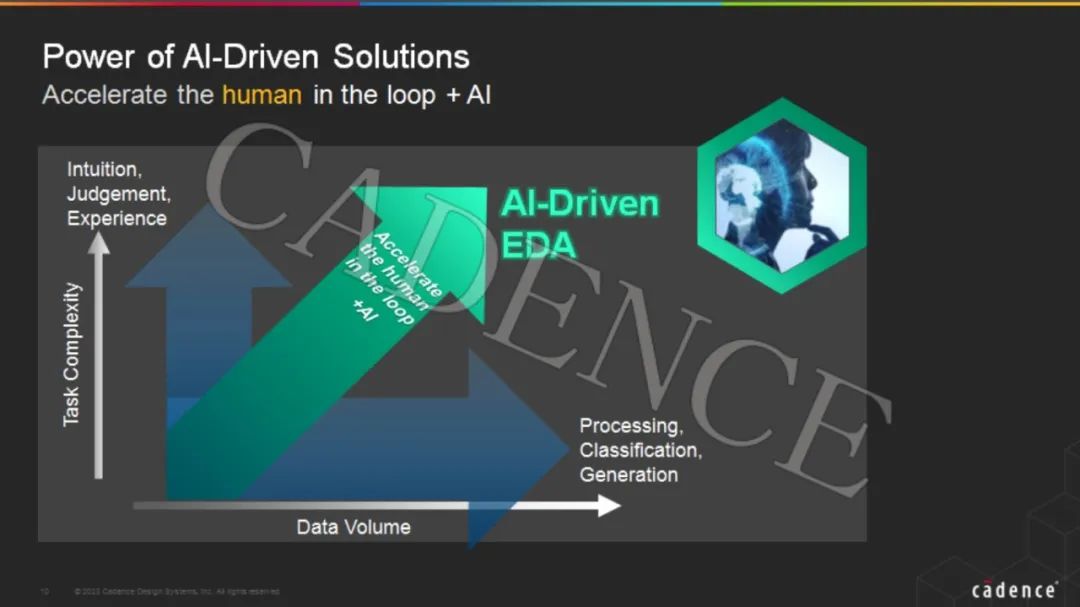

而設(shè)計(jì)這樣的智能系統(tǒng)對 EDA 提出了巨大的挑戰(zhàn),只有不斷提高生產(chǎn)力才能滿足設(shè)計(jì)需求。EDA 通過提升抽象層次,從晶體管級到單元級,再到 IP 的設(shè)計(jì)復(fù)用,以及現(xiàn)在基于 AI 的 EDA 或基于 AI 的自動化來提高生產(chǎn)力,同時有助于延續(xù)摩爾定律。 他認(rèn)為,工程師能夠創(chuàng)造性地解決復(fù)雜問題,但人不善于處理海量數(shù)據(jù)。而 AI 可以在算法指引下并行處理海量數(shù)據(jù),并在這個過程中找到規(guī)律。當(dāng)通過新一代 EDA 算法把人工智能和優(yōu)秀工程師的能力結(jié)合在一起時,就可以同時解決高復(fù)雜度和大數(shù)據(jù)量的設(shè)計(jì)難題,極大地提升智能系統(tǒng)的設(shè)計(jì)生產(chǎn)力。

他認(rèn)為,工程師能夠創(chuàng)造性地解決復(fù)雜問題,但人不善于處理海量數(shù)據(jù)。而 AI 可以在算法指引下并行處理海量數(shù)據(jù),并在這個過程中找到規(guī)律。當(dāng)通過新一代 EDA 算法把人工智能和優(yōu)秀工程師的能力結(jié)合在一起時,就可以同時解決高復(fù)雜度和大數(shù)據(jù)量的設(shè)計(jì)難題,極大地提升智能系統(tǒng)的設(shè)計(jì)生產(chǎn)力。

Cadence AI 解決方案引領(lǐng)潮流

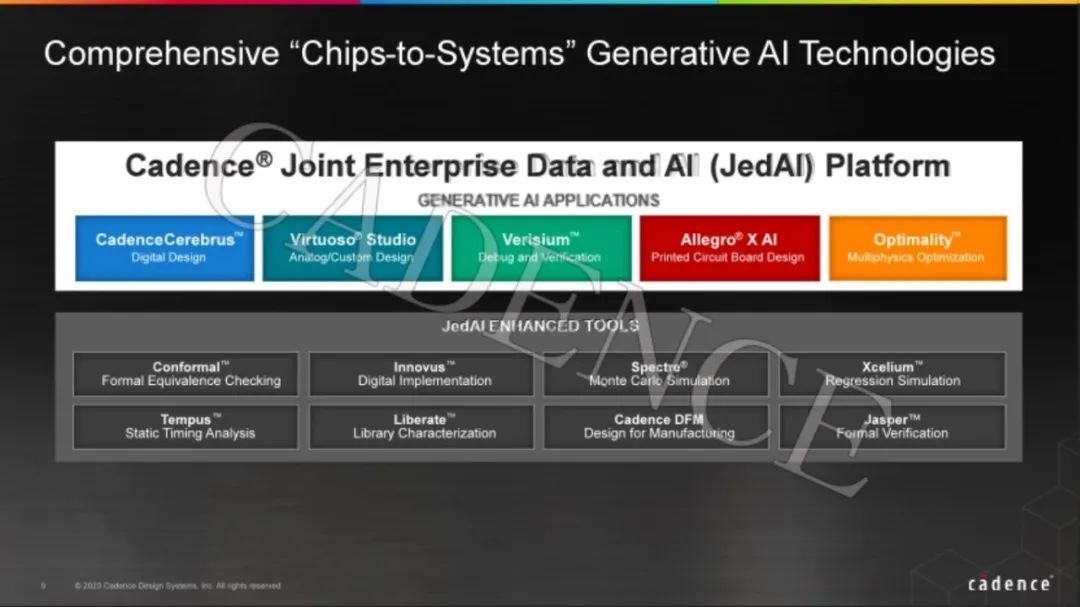

陳敏介紹說,Cadence 同時在兩個方面實(shí)現(xiàn)了 EDA 的 AI 改造,一是通過 AI 技術(shù)提升 EDA 核心解算器的效率;二是通過 AI 處理大量的設(shè)計(jì)數(shù)據(jù),提高人在環(huán)內(nèi)的設(shè)計(jì)效率,目前多個產(chǎn)品線都有了相應(yīng)的 AI 功能。 Cadence 全棧 AI 的 EDA 解決方案包括用于更快調(diào)試的 Verisium、用于更快更智能芯片設(shè)計(jì)的 Cerebrus、用于支持 AI 的多物理場系統(tǒng)分析優(yōu)化且是業(yè)界首個提供機(jī)器學(xué)習(xí)(ML)驅(qū)動的完整 PCB 綜合平臺 Allegro X 和提供 AI 驅(qū)動的自定義布局解決方案 Virtuoso AI,以及支持 AI 的大數(shù)據(jù)分析平臺——JedAI(聯(lián)合企業(yè)數(shù)據(jù)和 AI 平臺)。 Cadence 的領(lǐng)先技術(shù)有助于設(shè)計(jì)團(tuán)隊(duì)利用先進(jìn)的 AI 驅(qū)動解決方案套件優(yōu)化芯片性能,加速芯片設(shè)計(jì)并提高整個設(shè)計(jì)流程的效率,將更多時間用于創(chuàng)新,縮短進(jìn)入市場的時間。

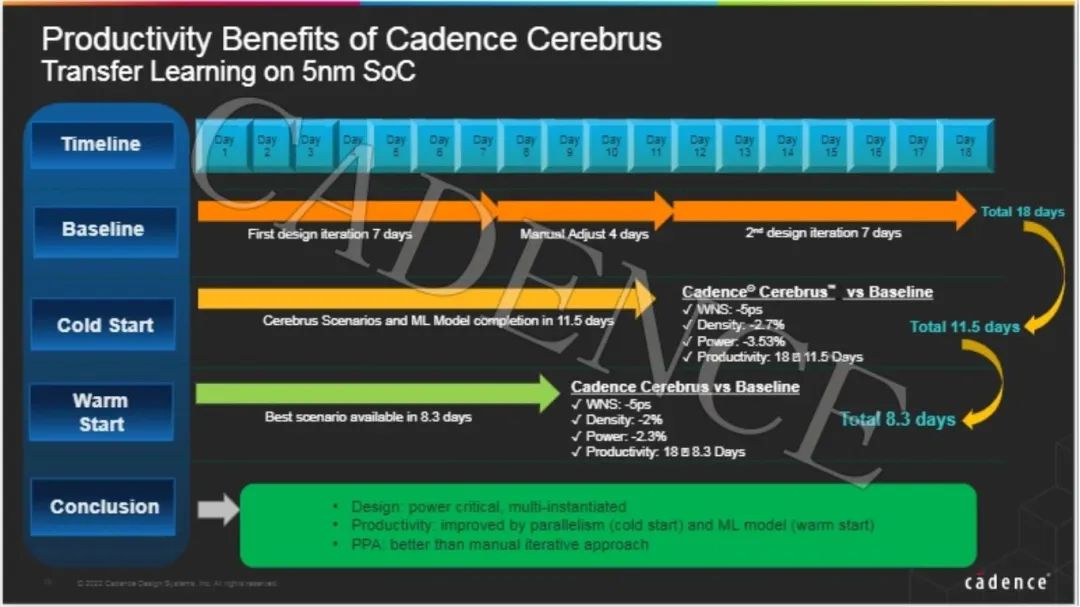

他還分享了 Cerebrus 工作流程讓客戶受益的案例——在臺積電 N5 SoC 上使用 Cerebrus 的客戶使用和不使用 ML 驅(qū)動優(yōu)化的設(shè)計(jì)周期時間表。手動優(yōu)化需要 18 天才能完成基線優(yōu)化,而使用 Cerebrus 冷啟動,優(yōu)化流程在 11.5 天內(nèi)完成,且 PPA 更好;使用ML模型,熱啟動僅在 8.3 天內(nèi)就完成了設(shè)計(jì)收斂,優(yōu)化周期時間縮短了 53%,功率、密度和 WNS 也得到了改善。

另外,作為 Cadence AI 戰(zhàn)略的一部分,其最近推出的 JedAI 可以使設(shè)計(jì)數(shù)據(jù)和 AI 訓(xùn)練信息在設(shè)計(jì)流程的不同部分和不同產(chǎn)品之間輕松傳輸。這是一項(xiàng)跨 Cadence 的計(jì)劃,隨著時間的推移,越來越多的 Cadence 產(chǎn)品將與 JedAI 原生連接。

AI 將賦能EDA 變革

陳敏指出,AI 將成為 EDA 的一項(xiàng)變革性技術(shù)。目前,每個區(qū)塊都需要大量的人工工程來實(shí)現(xiàn)所有的流片目標(biāo)。現(xiàn)在,設(shè)計(jì)師可以使用 Cerebrus AI 驅(qū)動的優(yōu)化來提高區(qū)塊收斂效率和 PPA 效果,不過每個區(qū)塊仍是獨(dú)立實(shí)施的。 未來,Cadence 的設(shè)計(jì)收斂將在子系統(tǒng)層面進(jìn)行,工程師只需研究一個完整的區(qū)塊子系統(tǒng)。為了實(shí)現(xiàn)這一點(diǎn),Cadence 正在開發(fā)一個完整的多塊設(shè)計(jì)中心。利用 AI 自動化,只需一個工程師就可以實(shí)現(xiàn)整個子系統(tǒng),或同時處理多個設(shè)計(jì)的系統(tǒng),實(shí)現(xiàn)單工程師、多設(shè)計(jì)、多運(yùn)行的解決方案。這將是芯片設(shè)計(jì)的未來。

李志勇

適用大模型 AI芯片的接口 IP

在 IIC Shenzhen 的 EDA/IP 與 IC 設(shè)計(jì)論壇上,李志勇分享了大語言模型巨大的應(yīng)用市場對 AI 芯片架構(gòu)設(shè)計(jì)提出的諸多挑戰(zhàn),介紹了 Cadence 提供的最先進(jìn)的 LLM AI SoC 接口 IP 解決方案。

大模型對 AI 芯片設(shè)計(jì)要求更高

李志勇表示,兩年來,以 ChatGPT 為代表的生成式 AI 呈現(xiàn)爆炸式增長,相關(guān)硬件需求迅速增加,據(jù) Bloomberg Intelligence 預(yù)測,未來 10 年相關(guān)產(chǎn)值將從 370 億美元增長到 6410 億美元。無論是數(shù)據(jù)中心還是邊緣側(cè),對 ASIC 的需求都將與日俱增。

大語言模型巨大的市場正在導(dǎo)致 AI 訓(xùn)練/推理芯片的變革,而 Transformer 網(wǎng)絡(luò)模型需要大量的參數(shù)來支撐,對 AI 芯片架構(gòu)設(shè)計(jì)提出了更高要求,其中高帶寬存儲接口、芯片互聯(lián)、小芯片(Chiplet)都需要高速高帶寬的接口 IP。

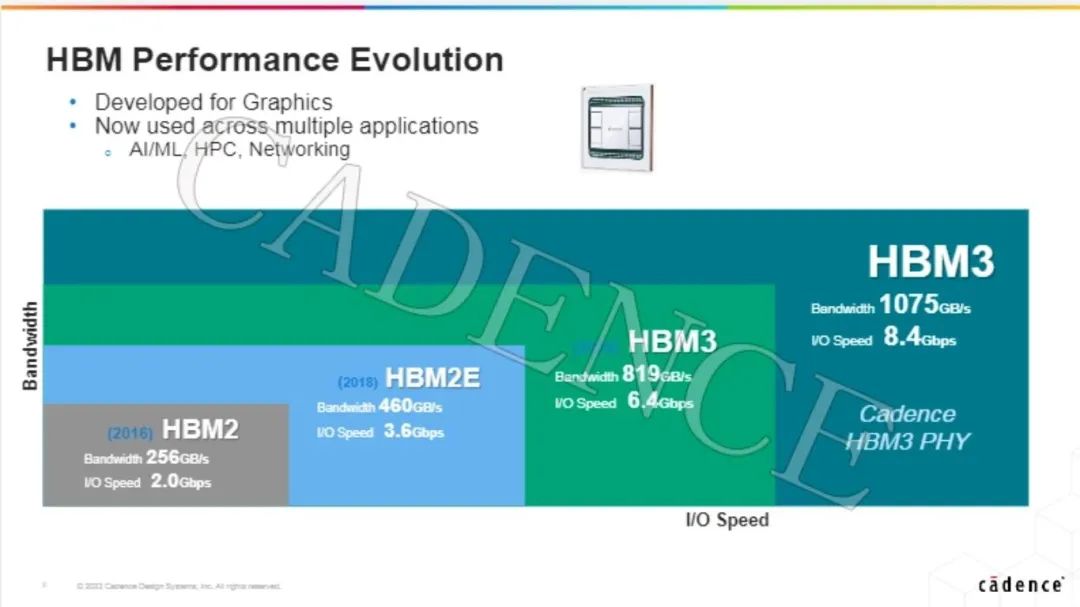

另外,不同 AI 應(yīng)用場景對內(nèi)存的要求不盡相同,如帶寬、成本和功耗;HBM IO 速率也在發(fā)生變化,IO 帶寬每三年將翻一番;PCIe 接口標(biāo)準(zhǔn)已演進(jìn)到 PCIe7,CXL功能也已升級到 3.0,高速以太網(wǎng)在數(shù)據(jù)中心已大量使用。

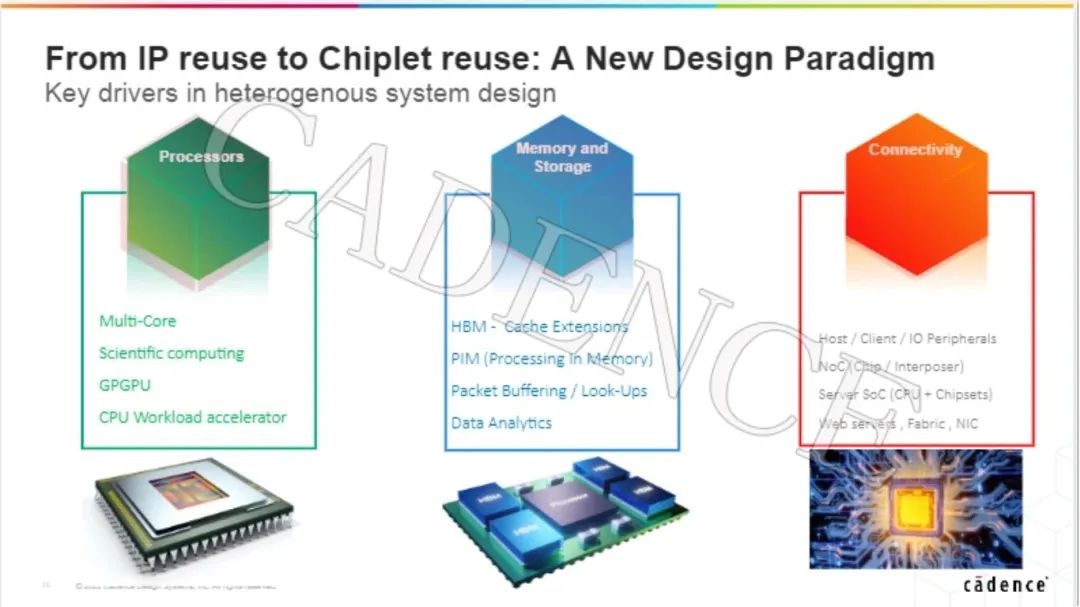

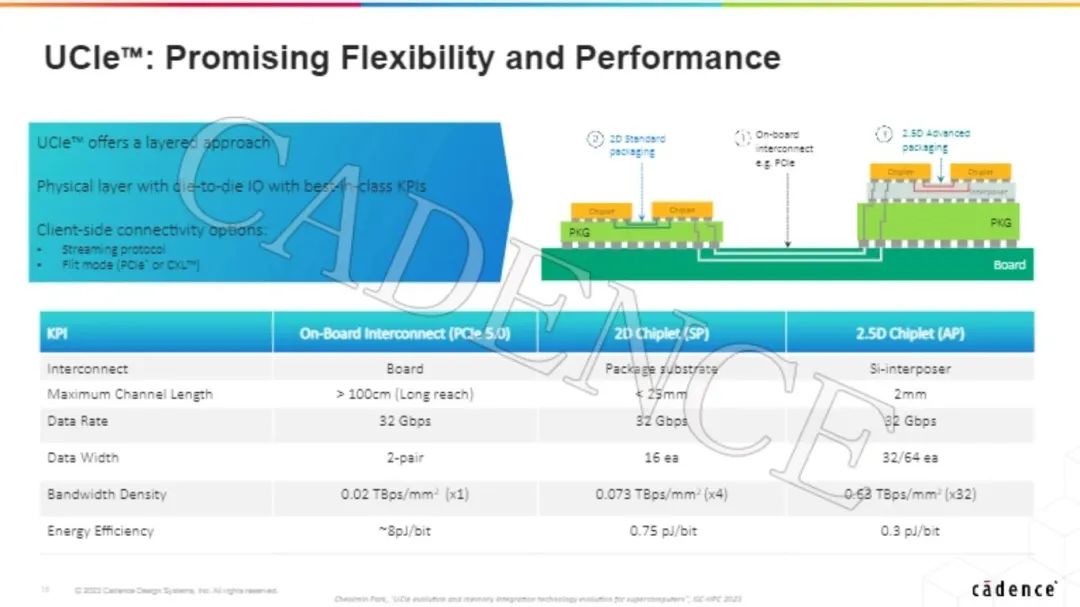

芯片設(shè)計(jì)方面,在異構(gòu)系統(tǒng)設(shè)計(jì)推動下,出現(xiàn)了一種新的設(shè)計(jì)范式——從 IP 復(fù)用到 Chiplet 復(fù)用。在 Chiplet 中,利用UCIe可以提高帶寬密度和功率效率,進(jìn)一步降低功耗。

李志勇認(rèn)為,當(dāng)前的挑戰(zhàn)有三,一是傳統(tǒng)芯片和封裝設(shè)計(jì) EDA 在尺寸/復(fù)雜性和先進(jìn)工藝節(jié)點(diǎn)、3D-IC 和高速模擬信號設(shè)計(jì);二是芯片以外的系統(tǒng),包括外殼/PCB/封裝/芯片電磁和熱設(shè)計(jì)、安全軟件的早期開發(fā)以及毫米波和微波射頻;三是系統(tǒng)融入智能的需求越來越多,必須提高設(shè)計(jì)質(zhì)量,使產(chǎn)品更具可擴(kuò)展性。

為要求苛刻的應(yīng)用

樹立先進(jìn)節(jié)點(diǎn)新標(biāo)準(zhǔn)

李志勇表示,Cadence 為要求苛刻應(yīng)用的先進(jìn)節(jié)點(diǎn)提供最先進(jìn)的接口 HPC/AI LLM IP 解決方案,如 PCIe5/6 和 CXL2 經(jīng)過硅驗(yàn)證的子系統(tǒng);112G PHY IP 和 224G PHY IP;硅驗(yàn)證的 LP5x-8533、24G 的 GDDR6 IP 和業(yè)界最快的 HBM3 8.4G;以及大規(guī)模商用的 Ultralink PHY IP 和最新 UCIe IP。

他介紹說,Cadence HBM3 內(nèi)存接口是具有 8.4Gbps 最高性能的 PHY IP 完整解決方案;中介層設(shè)計(jì)是 2.5D 系統(tǒng)設(shè)計(jì)的關(guān)鍵組件,可為所有 PHY 到 DRAM 連接提供相似的路由長度,以實(shí)現(xiàn)最高數(shù)據(jù)速率。

李志勇還展示了 Cadence 業(yè)界首個用于 PCIe 和CXL 的硅 IP 子系統(tǒng),以及 128G PCIe 7.0-ready SerDes IP,以及已在 Tier1 超標(biāo)量處理器和前沿初創(chuàng)公司大規(guī)模商用的 40G UltraLink D2D PHY+鏈路層。

助客戶成功一臂之力

李志勇強(qiáng)調(diào),UCIe 可以支持標(biāo)準(zhǔn)封裝和先進(jìn)封裝,Cadence 112G Serdes PHY 支持 1-112G 速率及以太網(wǎng)等多種協(xié)議。Cadence 在 CoWoS 方面的豐富經(jīng)驗(yàn)也有助于大芯片設(shè)計(jì)一次成功。

他最后總結(jié)道,Cadence 提供完整的 HPC IP 設(shè)計(jì)套件,包括業(yè)界領(lǐng)先的 DDR/HBM/GDDR IP、PCIe/CXL IP 和 D2D 以及 PAM4 IP。這些豐富的 IP 組合可以為各個先進(jìn)工藝節(jié)點(diǎn)提供更高性能的 IP。

關(guān)于 Cadence

Cadence 是電子系統(tǒng)設(shè)計(jì)領(lǐng)域的關(guān)鍵領(lǐng)導(dǎo)者,擁有超過 30 年的計(jì)算軟件專業(yè)積累。基于公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計(jì)概念成為現(xiàn)實(shí)。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計(jì)算、5G 通訊、汽車、移動設(shè)備、航空、消費(fèi)電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)九年名列美國財(cái)富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請?jiān)L問公司網(wǎng)站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版權(quán)所有。在全球范圍保留所有權(quán)利。Cadence、Cadence 徽標(biāo)和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標(biāo)志均為 Cadence Design Systems, Inc. 的商標(biāo)或注冊商標(biāo)。所有其他標(biāo)識均為其各自所有者的資產(chǎn)。

往期推薦

喜訊!Cadence Verisium 平臺榮獲 2023 ASPENCORE 全球電子成就獎!

AI 注入 EDA,點(diǎn)燃汽車革命烽火

芯片邁向系統(tǒng)化時代:EDA 軟件的創(chuàng)新之路

-

Cadence

+關(guān)注

關(guān)注

65文章

921瀏覽量

142077

原文標(biāo)題:IIC Shenzhen 2023 | Cadence 應(yīng)對 AI 機(jī)遇與挑戰(zhàn),智能重塑芯片設(shè)計(jì)流程

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AI智能體是什么_AI智能體如何重塑企業(yè)業(yè)務(wù)流程

Cadence如何應(yīng)對AI芯片設(shè)計(jì)挑戰(zhàn)

英諾達(dá)受邀參加IIC Shenzhen 2024

巨霖科技IIC Shenzhen 2024大會回顧

愛芯元智亮相IIC Shenzhen 2024

晶華微攜多款芯片產(chǎn)品及解決方案亮相IIC Shenzhen 2024

仇肖莘探討2024 AI芯片新趨勢與邊緣智能機(jī)遇

芯和半導(dǎo)體邀您相約IIC Shenzhen 2024峰會

愛芯元智邀您相約IIC Shenzhen 2024峰會

智能駕駛的挑戰(zhàn)與機(jī)遇

《AI for Science:人工智能驅(qū)動科學(xué)創(chuàng)新》第6章人AI與能源科學(xué)讀后感

AI for Science:人工智能驅(qū)動科學(xué)創(chuàng)新》第4章-AI與生命科學(xué)讀后感

在機(jī)遇與挑戰(zhàn)并存的AI時代,三星如何在DRAM領(lǐng)域開拓創(chuàng)新?

EMI電磁干擾:挑戰(zhàn)與機(jī)遇并存,如何應(yīng)對是關(guān)鍵

IIC Shenzhen 2023 | Cadence 應(yīng)對 AI 機(jī)遇與挑戰(zhàn),智能重塑芯片設(shè)計(jì)流程

IIC Shenzhen 2023 | Cadence 應(yīng)對 AI 機(jī)遇與挑戰(zhàn),智能重塑芯片設(shè)計(jì)流程

評論