今天給大家分享的是:高速 PCB 設計

主要是關于4 個高速 PCB 設計常見術語和保證信號完整性的3 種常見技術介紹。

一、高速 PCB 設計常見術語

1、轉換率

這里要明白一個點,不存在從關到開的瞬時轉變,電壓必須是從低電平轉換到高電平,雖然速度很快,但也會通過這中間的所有電壓。

在轉換器期間的某個時間點,它是1.8V,而在另一個時間點是2.5V。電壓從低狀態轉變到高狀態的速度稱為轉換速率。

2、速度

電信號也有速度限制-光速,光速非常快。考慮到1GHz 信號的周期為 1ns(1 納秒),光的傳播速度約為 0.3 m/ns,即 30 cm/ns,意味著在 30 cm 長的導體上,當下一個時鐘脈沖在其開始處生成時,1GHz 信號的第一個時鐘脈沖剛剛到達導體的另一端。

假設為 3GHz,當第一個脈沖到達導體的另一端時,時鐘信號源已經生成第三個脈沖,如果是 3GHz,30cm 導體,意味著單個 30cm 導體在其長度內包含3 個脈沖、3 個高狀態和低狀態。

信號傳輸不是瞬時

3、可靠性

每當電流通過導體時,就會在導體周圍產生磁場,。相反,當磁場穿過導體時,會在該導體內產生電壓。因此電路中的所有導體(通常是 PCB上的走線)都能產生和接受電磁干擾,可能會導致走線傳輸的信號失真。

PCB上的每個軌道也可以被視為一個小型無線電天線,能夠生成和接受無線電信號,可能會使軌道承載的信號失真。

4、阻抗

在上面已經講到過,電信號不是瞬時,實際上在導體中以波的形式傳播。在 3GHz / 30cm 跡線示例中,任何給定時間導體內都有 3 個波(波峰和波谷)。

波會受到各種現象的影響,其中對我們來說最重要的是“反射”。

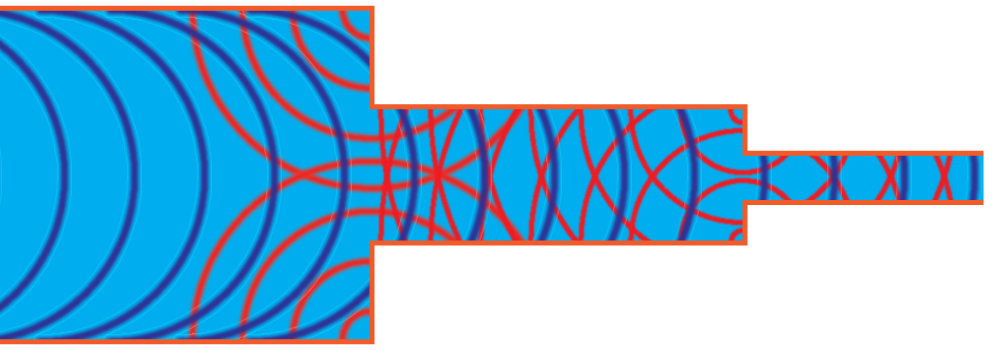

這里想象一下,我們的導體就像充滿水的運河/通道。波在通道的一端產生,并沿著通道(以接近光速)傳播到另一端。通道本來有100cm寬,但在某個時刻突然變窄到只有1cm寬,當我們的波到達突然變窄的部分(本質上是一堵有小縫隙的墻壁),大部分波會被反彈回來狹窄的部分(墻壁)并向后朝向發射器。

由于寬度變化而產生的波反射

如果運河/通道內有多個狹窄部分,就會有多次反射反彈,干擾信號,信號的大部分能量也不會到達接收器(至少不會在正確的時間)因此,重要的是通道的寬度/高度沿其長度盡可能保持恒定,避免反射。

寬度的多次變化會降低信號質量

也就是阻抗,是導體的電阻、電容和電感的函數。對于高速設計,我們希望走線的阻抗沿其長度盡可能保持一致,另外一件需要考慮的事情,特別是在總線拓撲中,我們希望在接收器處停止波,而不是讓它再次反彈。

這通常是通過終端電阻來實現的,終端電阻會吸收末端波的能量總線(例如RS485)

二、信號完整性

在設計電路時需要考慮回轉、速度、磁干擾和阻抗。

在 PCB 設計過程中考慮阻信號完整性意味著要考慮所有的這些因素,并且在PCB上采取適當的對策。

下面是 PCB 設計中使用的幾種常見技術。

1、長度匹配軌道

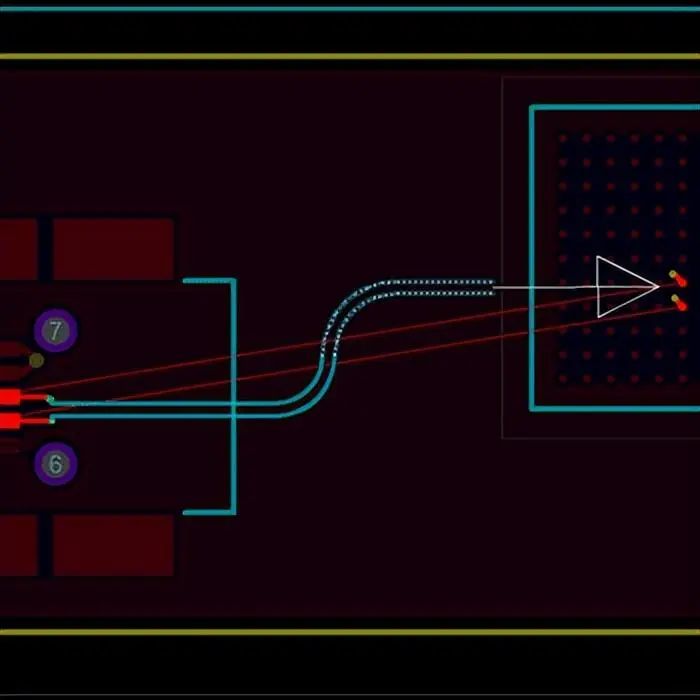

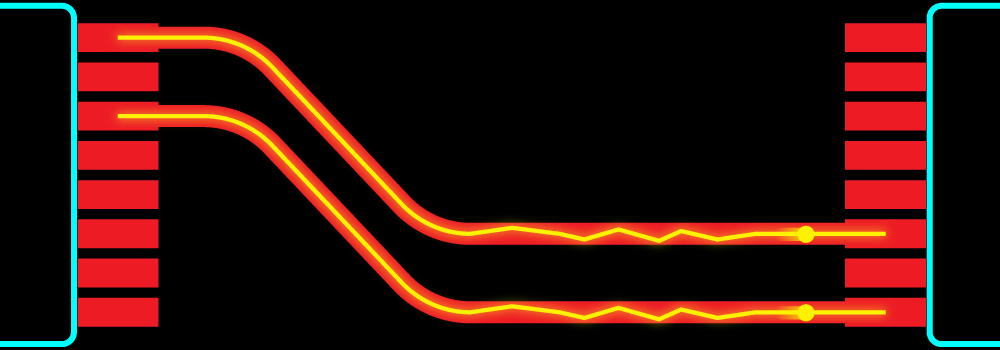

當我們的通信信號使用多條線路時,例如”時鐘“和”數據,可能具有8條/更多數據線的并行總線,那就必須確保信號全部到達接收器同時。

現在已經知道電信號不會瞬時傳播,那我們就可以理解,如果多個信號在不同長度的軌道上傳播,那么將在不同時間到達接收器。(即使它們是在完全相同的時間傳輸的)

不均勻的軌道長度可能會導致接收器發出不正確的信號

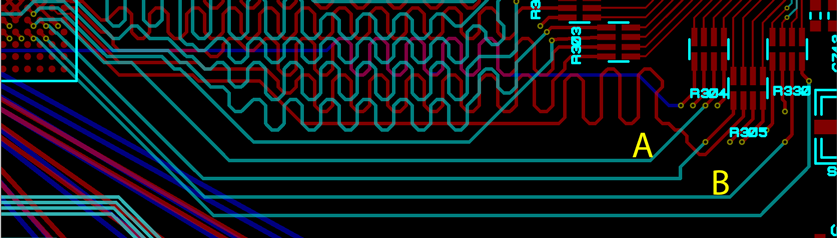

考慮具有條時鐘線(C)和2條數據線(A和B)的通信方案。如果數據線B的長度比數據線A的長度長的多,則B線上時鐘脈沖#1的信號可能與B線上時鐘脈沖#2的信號同時到達接收器,一條線路到達接收器,一條線路到達那里,完全扭曲和破壞了通訊。

軌道 A 和 B 的長度不同

另一種可視化的方法是想象很多人在兩條不同的跑道上跑步,每個人只能攜帶一半的信息,并且信息會在終點線重新組裝。如果人以相同的速度行進,并且軌道的長度相同,那么將同時到達目的地,并且接收者可以正確地重新組裝文件。

但是,如果軌道長度不同,那么人不會同時到達,文件沒有辦法很容易就重新組裝。

因此多線通信信號中的軌道長度相同非常重要,也就是軌道長度匹配或者網絡調諧。

這里特意增加了軌道A的長度,以便從源到接收器的距離與軌道B相同

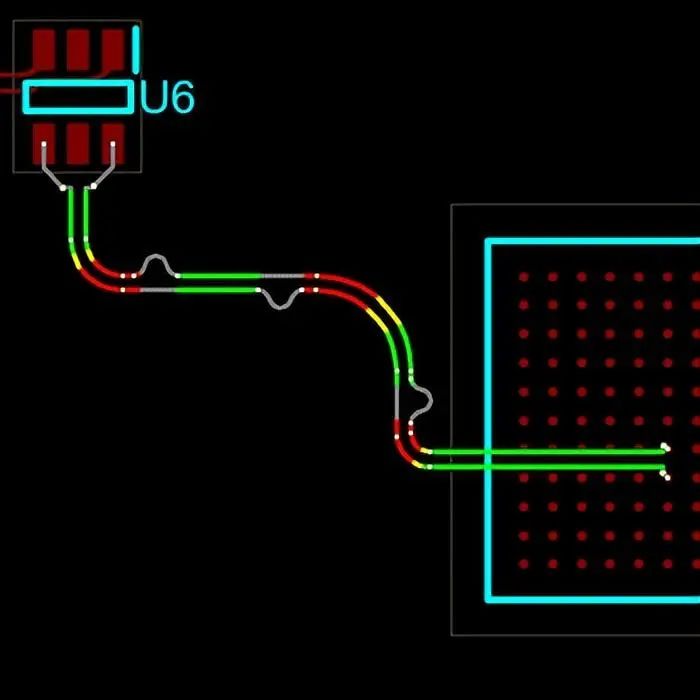

2、差分對

差分對是一種高度不受電磁干擾的通信技術。最常見且最容易識別的是實現USB,另一種實現差分對的技術是RS485。

差分對在兩個平行導體上使用推拉技術-一個推,另一個拉,如果一條線為高,那么另一條線一定為低,反之亦然。

差分對中的信號通過任一導體上的電壓之間的差來測量。差分對的布線嚴格彼此平行且同相。

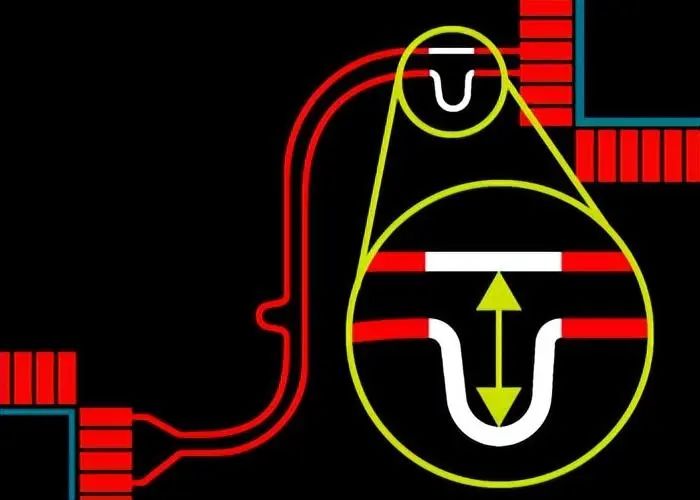

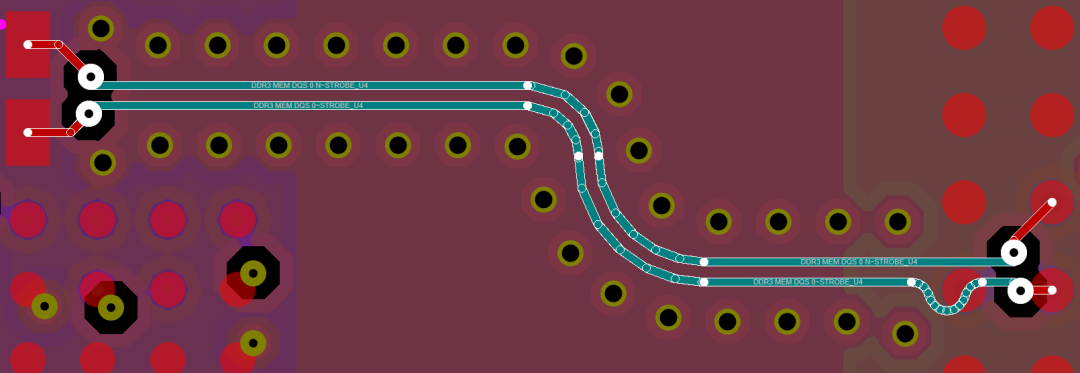

除了軌道長度匹配之外,同相要求意味著如果差分對繞過一個彎曲(導致外軌道比內軌道采用更長的路徑),那么內軌道必須人為低添加一點額外的長度,盡快回到其軌道,以便盡快使平行對的起點/終點的總距離再次均衡。

彎曲差分對的布線

添加軌道以保持配對同相

添加軌道以保持配對同相

差分對可能遇到的干擾都應該同等地影響兩條軌道,這樣,它們之前的差異才能保持恒定且可靠。

保持軌道相同非常重要,如果軌道總的某一特定點受到電磁干擾,就會以相同的方式影響并行信號。如果信號異相,則信號一側的峰值可能受到影響,而信號另一側的波谷可能受到影響。

只要兩條信號線同相,干擾就會同等影響它們

3、過孔縫合和屏蔽

通孔屏蔽是一種“屏蔽”軌道免受產生和接收電磁干擾的技術。“電源層”(也稱為“接地層”或“覆銅層”)被放置在多個 PCB 層上圍繞一個或多個軌道,然后使用過孔將這些電源層層縫合在一起,從而產生以下效果。

通過屏蔽差分對軌道

較高的轉換速率(信號從“高”到“低”或反之亦然)轉換的速度比較低的轉換速率產生更多的電磁噪聲。壓擺率本身通常在芯片數據表中指定(有時是可配置的,例如某些微控制器),因此不是由 PCB 設計階段決定的,但在屏蔽方面可以對已知高壓擺率的信號進行屏蔽。

過孔縫合用于將兩個電源層“縫合”在一起。這樣做的原因之一是為信號提供短的“返回路徑”,這對于阻抗匹配等很重要。

原文鏈接:https://www.labcenter.com/blog/pcb-highspeed-intro/

免責聲明:本文轉自網絡,版權歸原作者所有,如涉及作品版權問題,請及時與我們聯系,謝謝!

加入粉絲交流群

張飛實戰電子為公眾號的各位粉絲,開通了專屬學習交流群,想要加群學習討論/領取文檔資料的同學都可以掃描圖中運營二維碼一鍵加入哦~

(廣告、同行勿入)

原文標題:高速 PCB 設計如何保證信號完整性?看這一文,7個技巧總結,秒懂

文章出處:【微信公眾號:張飛實戰電子】歡迎添加關注!文章轉載請注明出處。

-

模擬技術

+關注

關注

17文章

469瀏覽量

40025 -

張飛電子

+關注

關注

55文章

175瀏覽量

12830

原文標題:高速 PCB 設計如何保證信號完整性?看這一文,7個技巧總結,秒懂

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

聽懂什么是信號完整性

評論