最近接觸到了一些產線的Test的東西,然后發現這里面有一些DFX的相關東西。

之前在梳理整個安全領域全景圖的時候,也提到了調試安全。

林林種種原因讓我打算來學習一下DFX相關的內容,那自然就繞不開Coresight。

今天就一起來看看Coresight吧,最近喜歡上了畫圖來整理自己的思路。

縮略詞

CoreSight Soc-400一個完整的調試和跟蹤解決方案,包括如下組件:

?控制和接入組件:

?DAP(Debug Access Port):用來連接外部硬件調試工具的物理接口,允許外部調試工具訪問芯片上CPU、CoreSight、DDR等。

?ECT(Embedded Cross Trigger)

?跟蹤數據源:跟蹤源是CoreSight中用于產生跟蹤信息的組件。每個跟蹤源組件都會產生一種格式的信息,最終可以組合在一起并且通過跟蹤鏈接到輸出端口。

? PTM(Program Trace Macrocell):監控處理器運行狀況,將處理器執行過的指令信息進行壓縮傳輸。

? STM(System Trace Macrocell):捕捉系統的事件信息并以獲取數據跟蹤形式傳輸到跟蹤漏斗或跟蹤輸出組件。

?ETM(Embedded Trace Macrocell):監控處理器運行狀況,將處理器執行過的指令信息進行壓縮傳輸。跟蹤指令執行、數據搬運、PE(Processing Element)事件。

?連接:

? Synchronous 1:1 ATB bridge:

? Replicator:可以把單個輸入復用到兩個分支輸出,可以使得CoreSight系統跟蹤信息同時傳輸到兩個或多個輸出。

? Trace Funnel:把CoreSight系統中多個跟蹤源產生的信息組合在一起并以單個流輸出到高級跟蹤總線ATB。Funnel之間可以級聯,一個Funnel最多可以支持6個跟蹤源信息輸入。

?跟蹤輸出節點:

? ETR(Embedded Trace Router):把跟蹤數據存儲到調試目標平臺的系統內存上,存儲系統內存空間是可配置的。

?ETF(Embedded Trace FIFO):主要是緩沖數據的輸出,尤其當當量數據在瞬間產生式,通過ETF可以平滑數據的輸出速率。緩存可以被配置為FIFO或Circular Buffer;FIFO滿了之后就會反壓,源頭停止輸出跟蹤數據;Circular Buffer滿了后則會覆蓋。

? TPIU(Trace Port Interface Unit):把捕捉到的數據導出到外部調試適配器,如DSTREAM。

? ETB(Embedded Trace Buffer):是芯片內一塊RAM,用來存儲捕捉到的跟蹤信息。可以通過DAP訪問存儲在ETB中的數據。

? TMC(Trace Memory Controller):在芯片設計時可配置,配置成ETB時跟上面介紹的ETB功能一致。還可以配置成ETR和ETF。

時間戳組件:產生CoreSight或處理器所需的時間戳。通過Narrow timestamp replicator分發到多個目的設備。路徑:時間戳發生器->時間戳編碼器->Narrow timestamp replicator->時間戳解碼器->CPU/CTI等。

?時間戳發生器

?時間戳編碼器

?時間戳解碼器

?AMBA AHB跟蹤宏單元(HTM)

?調試訪問接口(DAP),

?嵌入式交叉觸發器(ECT),

?AMBA跟蹤總線(ATB),

?橋和復制器(replicator),

?跟蹤聚合器(funnel),

?跟蹤端口接口單元(TPIU),

?嵌入式跟蹤緩沖器(ETB),

?測量跟蹤宏單元(ITM/STM)

更詳細的可以閱讀【ARM:CoreSight、ETM、PTM、ITM、HTM、ETB等常用術語解析】

一、coresight

coresight是ARM公司提出的,用于對復雜的SOC,實現debug和trace的架構。該架構,包含了多個coresight組件。眾多的coresight組件,構成了一個coresight系統。

我們也可以根據coresight架構,實現自己的coresight組件。

每個coresight的組件(component),都要遵循coresight架構的要求。

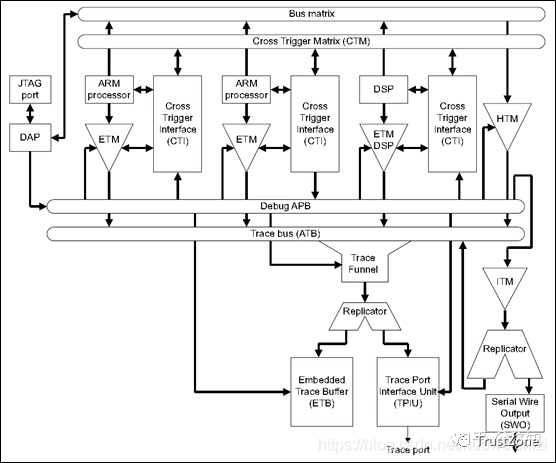

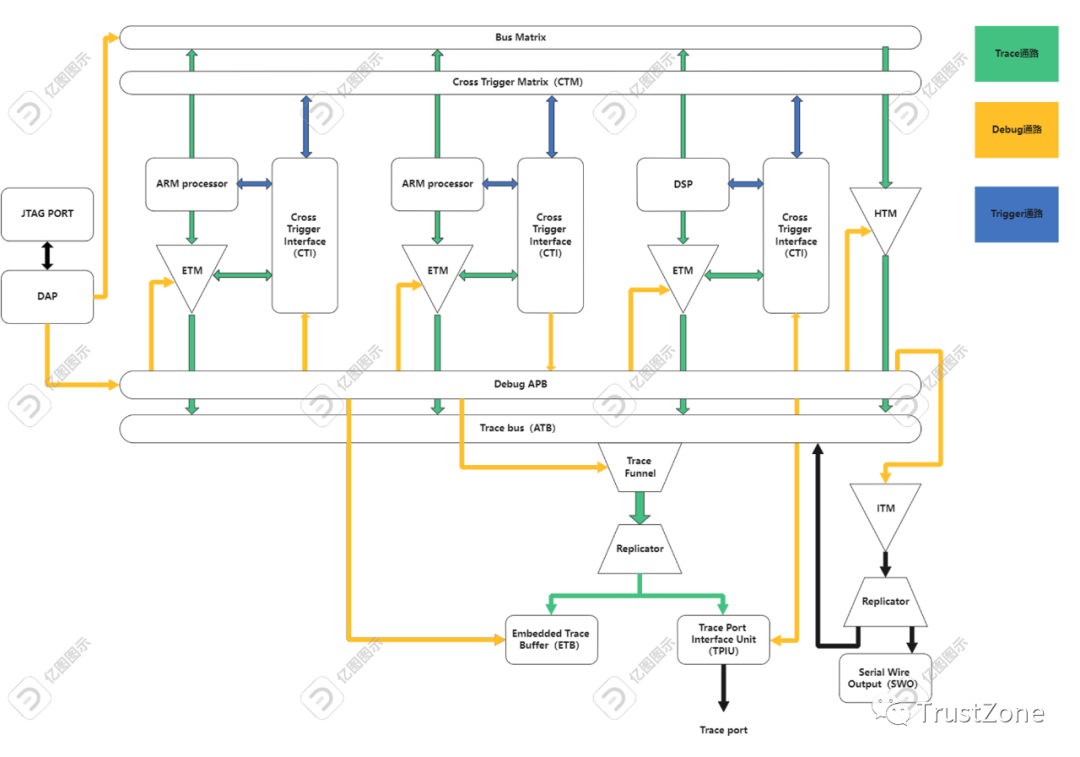

1、 典型的一個coresight的環境

以下是一個典型的coresight環境,包含了兩個ARM core,一個DSP,和眾多的coresight組件。

這個coresight組件,實現對core,DSP的debug和trace功能。

環境中,總共包括3個通路

? trace通路:將core和DSP內部信息輸出到外部

? debug通路:對core和DSP實現debug

? trigger通路:用于core和core之間,core和DSP之間,傳輸trigger信號

1.1、trace通路

trace通路,實現對master組件的數據追蹤功能,使用ETM來追蹤。

?ETM負責追蹤處理器和DSP的信息,將信息打包,通過ATB總線發送到trace bus上。

? trace bus上有trace funnel,funnel接收多個ATB總線數據,然后合并成一個ATB總線數據,發送給replicator。

? replicator接收到ATB數據,根據配置,將ATB數據發送給ETB和TPIU。

1.2、debug的通路

debug通路,用于外部的debugger,對ARM core和DSP進行調試功能。

上圖中,只考慮了JTAG的port。其實還有SW的port。

DAP接收外部端口的JTAG數據,然后轉化成對DAP內部的AP的訪問,然后AP再轉化為memory-mapped的總線訪問,去訪問soc內部的資源。

上圖中,DAP輸出兩個memory-mapped總線,

?一個是debug apb總線,連接到debug APB互聯上,用于訪問debug組件的寄存器,

?一個是system bus,連接到bus matrix,用于訪問soc的內部的資源。

debug APB互聯,連接了有CTI,ETM,HTM,ITM,ETB,TPIU等coresight組件,因此外部的debugger可以通過JTAG port,對這些coresight組件進行訪問。

bus matrix一般是連接soc的一些外設,如memory,串口等,因此外部的debugger可以通過JTAG port對這些外設設備進行訪問。

1.3、trigger通路

trigger通路,用于給指定的組件發送trigger信號,或者接收指定的組件的trigger信號。

這個功能由CTI和CTM來實現。

CoreSight交叉觸發接口(CTI)是一種硬件設備,它將被稱為觸發器的單個輸入和輸出硬件信號帶到設備和從設備輸出,并通過交叉觸發矩陣(CTM)將它們通過編號信道互連到其他設備,以便在設備之間傳播事件。

每個core和DSP都有一個CTI組件相連,CTI可以給處理器(DSP)發送trigger信號,也可以接收處理器(DSP)的trigger信號。

所有的CTI和CTM相連,因此可以實現多個CTI之間的trigger信號的相互發送與接收。

2、coresight組件的種類

2.1、control component

trigger的coresight組件

?ECT(embedded cross trigger)

? CTI(cross trigger interface):接收和發送trigger信號

? CTM(cross trigger matrix):CTI之間的trigger信號傳遞

2.2、trace sources

trace的coresight組件:

? ETM(embedded trace macrocells):追蹤指定設備(處理器,DSP)的trace信息,每個設備(處理器,DSP)均有自己的ETM。

? AMBA trace macrocells:追蹤AMBA總線的trace信息。

? PTM(program flow trace macrocells):

? STM(system trace macrocells):追蹤總線互聯上的trace信息

2.3、trace links

trace信息傳遞過程中所需要的中間coresight組件:

?trace funnel : 將接收的多個ATB總線數據合并成一個ATB總線數據

?replicator: 將一個ATB總線數據,分發成多個ATB總線數據發送

?ATB bridge: ATB 橋,用于兩個不同的ATB域之間數據傳輸

2.4、trace sinks

最終接收trace信息的coresight組件

? TPIU(trace port interface units):將ATB數據通過trace port發送給外界

? ETB(embedded trace buffers):存儲ATB數據的buffer

? TMC(trace memory controller):

每個trace sink可以有一個trace formatter。

2.5、debug access port

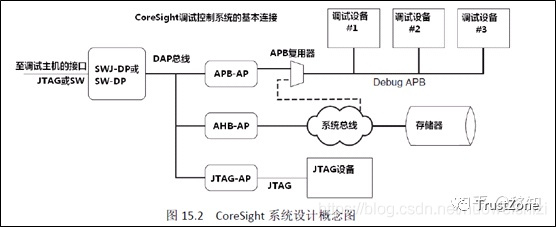

DAP不屬于coresight的組件,但是我們會通過DAP來對coresight的組件進行訪問。DAP包括以下:

?APB access port(APB-AP)

?AHB access port(AHB-AP)

?AXI access port(AXI-AP)

?JTAG access port(JTAG-AP)

?serial wire JTAG debug port(SWJ-DP)

?JTAG debug port(JTAG-DP)

?ROM table

DAP主要是由DP和AP組件。DP負責接收外部的JTAG或SW數據,然后轉化為對AP的訪問,而對AP的訪問,是可以發起memory-mapped的訪問。因此就可以對內部的資源進行訪問。

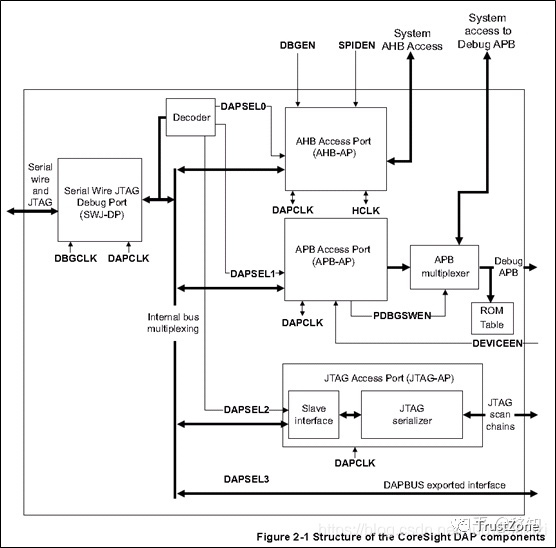

如上圖:DAP包括了三個AP

? APB-AP:對掛接到debug APB總線上的內部調試設備的訪問

? AHB-AP:對掛載在AHB系統總線上的設備的訪問

? JTAG-AP:對JTAG設備的訪問。這個是兼容以前較早的ARM處理器,如ARM9。這些較早的處理器內部是用JTAG來調試的。但是現在的ARM處理器,已經不用這種方式,統一用memory-mapped方式進行調試。

目前的ARM soc中,一般至少會包括一個DAP。而一個DAP可以包括1-256個AP(access port),AP受DP的控制。

只有對AP的訪問,才可以轉化成memory-mapped總線,對soc的內部資源進行訪問。

memory-mapped bus通常指的是將設備的寄存器映射到內存地址空間中,使得CPU可以通過讀取和寫入這些內存地址來訪問和操作這些設備。這種方式使得CPU可以像訪問內存一樣訪問這些設備,簡化了設備的訪問和控制方式。

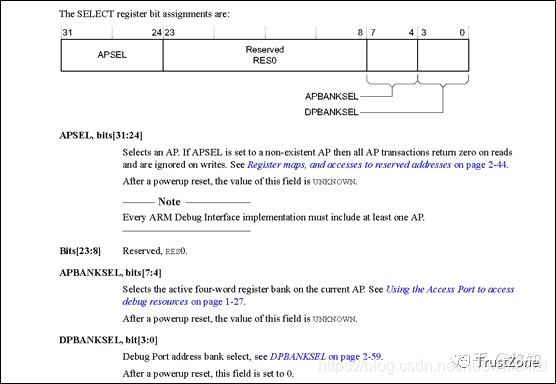

DP中有一個SELECT寄存器,該寄存器用來選擇,DP對AP的訪問,是針對于哪一個AP進行訪問。

DAP中,是可以有多個AP的,而每次,只能對一個AP進行訪問。因為需要對AP進行編號,編號的值就在APSEL位域中。因為這個位域有8位,因此DAP中可以最多有256個AP。

DAP的內部結構如下圖:

包括了一個DP,和3個AP,依次是AHB-AP,APB-AP,JTAG-AP。

DP通過JTAG或者SW管腳,連接外部的debugger,和外部debugger進行通信。

DP接收到外部debugger發送的JTAG或SW數據,轉化為對內部AP的訪問。經過decoder模塊,判斷是對哪一個AP進行訪問,然后將訪問信息發送給對應的AP。

AP接收到DP的訪問后,轉化為對應的總線訪問,去訪問內部資源。

然后將訪問的信息,才回送給DP,DP再通過JTAG或SW,將訪問信息返回給外部的debugger。

以上就是本文全部內容,希望看完能對coresight有一個宏觀了解。

文章來源:TrustZone

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19261瀏覽量

229659 -

芯片

+關注

關注

455文章

50725瀏覽量

423174 -

編碼器

+關注

關注

45文章

3639瀏覽量

134430 -

cpu

+關注

關注

68文章

10855瀏覽量

211595

原文標題:2、coresight組件的種類

文章出處:【微信號:談思實驗室,微信公眾號:談思實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ARM調試CoreSight、ETM、PTM、ITM、HTM、ETB等常用術語解析

CoreSight是什么?其功能有哪些?

CoreSight性能監控單元架構

ACPI for CoreSight?性能監控單元架構1.0平臺設計文檔

Arm CoreSight ETM-M33技術參考手冊

Arm CoreSight SoC-600技術參考手冊

簡述DFX理念與產品研發(一)

簡要分析DFX實施流程

2021華為開發者大會亮點 HarmonyOS架構演進與關鍵技術-HarmonyOS對DFX能力的要求是什么

來講講與工具密切配合的CoreSight

芯片DFX:Coresight架構

芯片DFX:Coresight架構

評論