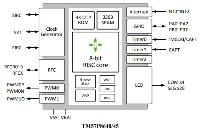

當今復雜的FPGA含有眾多用于實現各種電路與系統的功能塊,諸如邏輯陣列、存儲器、DSP模塊、處理器、用于時序生成的鎖相環(PLL)和延遲鎖定環DLL)、標準I/0、高速數字收發器以及并行接口(PCI、DDR 等)。這些不同的功能塊通常多個時鐘驅動,FPGA一般會綜合采用外部振蕩器以及內部PLL與DLL來生成時鐘。設計人員需要綜合使用外部與內部資源來實現最佳的時鐘樹設計。

而可編程時鐘振蕩器用作FPGA系統的時序參考,可提供一系列優勢;其中首要優勢是為了實現時鐘樹優化而進行高分辨率頻率選擇時所帶來的設計靈活性。另一個優勢是可以減少電磁干擾的擴頻調制功能。

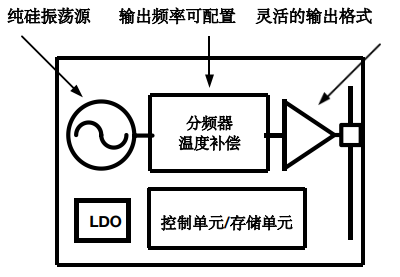

本文主要介紹一種可兼容替換石英晶振或MEMS振蕩器的純硅可編程振蕩器,該振蕩器是基于純CMOS工藝,利用自主創新的先進電路和補償算法來實現高性能的相位穩定性和頻率穩定性,相比基于石英晶振的同類產品可提供更高的可靠性。

國產純硅可編程振蕩器可以實現在超寬工業溫度范圍內頻率穩定度優于±50ppm,能產生10kHz至350MHz之間任意頻率,且相位抖動性能達到350fs rms的時鐘信號。是一種適用于服務器、AI處理器、網絡接口、邊緣計算、汽車電子以及廣泛工業應用的理想時鐘源。此外,純硅振蕩器只需要普通的塑封工藝,大大提高了供應鏈的靈活性和安全性。

可編程純硅振蕩器產品亮點:

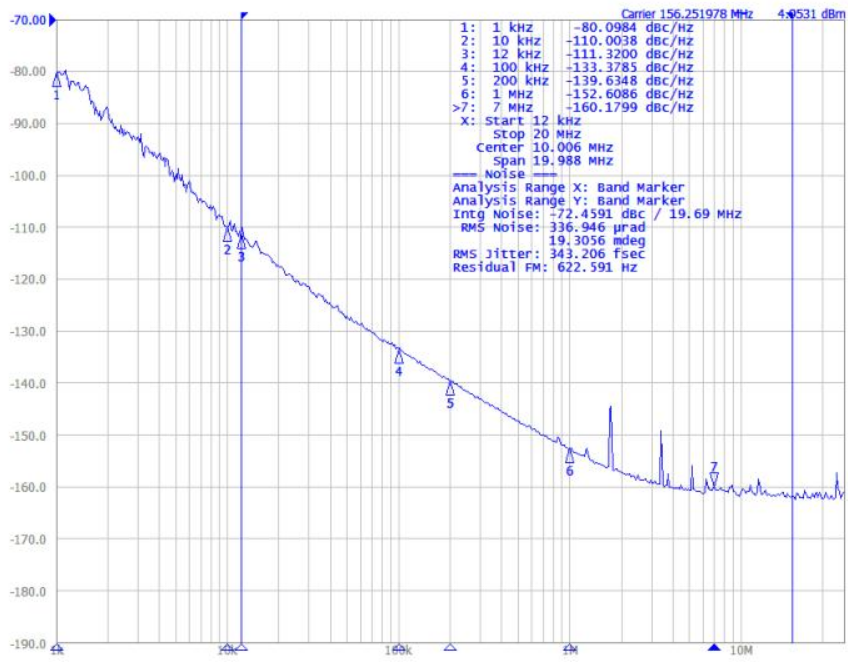

?總穩定度:+/-50ppm(包含10年老化)

?12kHz~20MHz帶寬范圍內相位抖動低于350fs

?工業級器件支持-40℃~+85℃工作溫度范圍

?擴展工業級器件支持-40℃~+105℃工作溫度范圍

?可支持輸出時鐘展頻SSC、VCXO和DCXO模式

?集成電路級的質量保證和可靠性

?支持單路LVCMOS,雙路LVCMOS,LVPECL,LVDS,HCSL及CML等輸出格式

?支持多至九種頻率配置以及12C可編程頻點輸出,可替換多個振蕩器和多路復用器,從而提高產品的可靠性和性能并降低用戶的BOM成本。

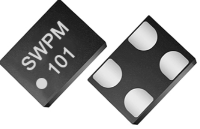

?提供與3.2x2.5mm和5.0x3.2mm振蕩器行業標準封裝兼容的6引腳封裝

注:如涉及作品版權問題,請聯系刪除。

-

FPGA

+關注

關注

1629文章

21754瀏覽量

604234 -

振蕩器

+關注

關注

28文章

3839瀏覽量

139167 -

驅動

+關注

關注

12文章

1844瀏覽量

85355 -

國芯思辰

+關注

關注

0文章

1064瀏覽量

1389

發布評論請先 登錄

相關推薦

解析全硅可編程 CMOS 振蕩器 SWPM101 系列(0.01 至 212.5 MHz)的卓越特性

利用國產純硅可編程振蕩器可增強FPGA的應用優勢

利用國產純硅可編程振蕩器可增強FPGA的應用優勢

評論