Perface

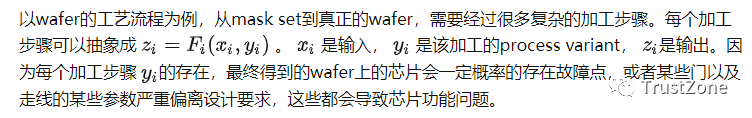

半導體芯片從想法到最終可以交付客戶的產品,簡單的說經歷芯片設計,芯片生產,芯片封裝和芯片測試。

半導體測試對于大多數人,甚至很多半導體從業人員而言,也是陌生的;很多人將半導體測試與設計階段的設計驗證,以及流片后的芯片功能驗證相互混淆。

半導體測試作為半導體產業鏈中不可或缺的一環,隨著工藝的持續下探,SoC的規模復雜度的持續增加,在項目中的重要性也越來越高,某種程度上決定了產品能否按時量產并交付客戶。

半導體測試是什么?

傳統意義的半導體測試指基于ATE機臺的產品測試,分為wafer level的CP測試(chip probing)或FE測試(FrontEnd test)和封裝之后的FT測試(final test)或BE測試(backend test)。當然隨著WLCSP (wafer level chip scale package)封裝的推廣,越來越多產品只需要CP測試后就可以切割分片供貨了。

在FrontEnd test中,主要測試晶圓的電性參數,如CMOS的電容、電阻、Contact、Metal Line等,通過這些參數來監控各步工藝是否正常和穩定。這個測試環節通常采用CP測試(Chip Probing)或FE測試(FrontEnd test)。

CP測試和FE測試是在芯片制造過程中的wafer level進行的,即芯片還沒有進行封裝之前。而FT測試和BE測試是在芯片封裝完成之后進行的。

+ CP測試(Chip Probing):這是在晶圓(wafer)級別進行的測試,主要用于測試一些基本的器件參數,如閾值電壓、導通電阻、源漏擊穿電壓、柵源漏電流和漏源漏電流等。此外,對于內存器件,CP測試還可以通過MRA計算出chip level的Repair address,通過Laser Repair將CP測試中的Repairable die修補回來,這有助于提高良率和可靠性。CP測試在芯片制造完成后、封裝前進行,能挑出壞的芯片,減少封裝和測試的成本,并直接了解晶圓的良率。

+ FE測試(FrontEnd test):這是在封裝之前進行的測試,主要針對的是邏輯設計。使用verilog/VHDL等語言進行行為級的描述,并使用仿真軟件進行RTL編程和仿真。

+ FT測試(Final test):這是在封裝之后的最終測試,主要檢查芯片的功能和性能。

+ BE測試(Backend test):也是封裝之后的測試,主要針對的是后端設計。

傳統的半導體測試是高度依賴DFT設計,完備的DFT設計可以提供高故障覆蓋率的測試激勵,保證半導體測試可以用最小的時間成本篩選出有故障的芯片。

但是隨著芯片軟硬件復雜度的提高,許多問題無法或很難抽象出相應的故障模型,因此SLT(system level test)也被多數公司采用,放在FT測試之后整個FT測試的故障覆蓋率,保證DPM(defects per million )滿足客戶需求。

DPM(defects per million)是指每百萬缺陷率,是一種衡量產品或系統中缺陷數量的指標。它通常用于評估產品質量、過程能力和可靠性等方面。

為什么半導體測試是必須的?

芯片在設計階段有完備的驗證流程,仿真驗證、UVM、形式驗證以及基于FPGA的SLE(system level emulation)等等驗證手段可以保證100%設計功能正確性。一般來說芯片可以流片,芯片的netlist是通過驗證的所有測試用例,完美實現設計需求的。

因此很多人會奇怪為什么每一個芯片都需要費時費力的經過嚴格的半導體測試,才能提供給客戶呢?

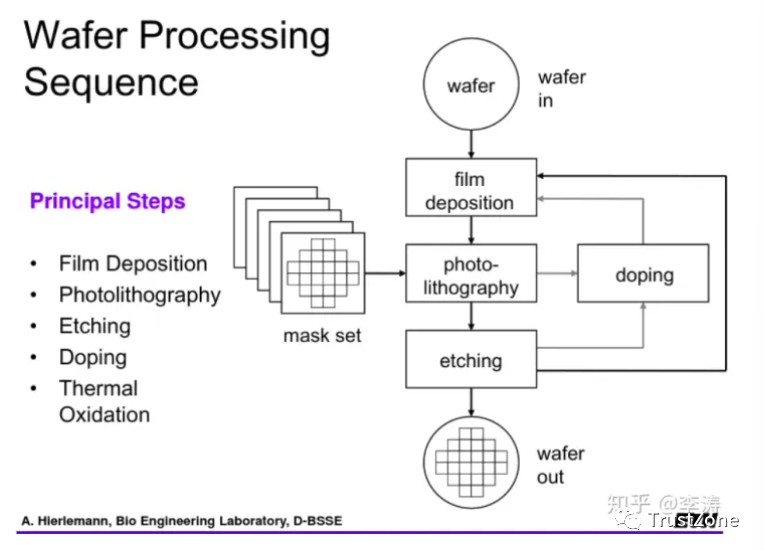

以成熟的28nm工藝為例,總體yield在93%左右(wafer的yield一般在93%左右而封裝后的yield一般在99%)。一個復雜電子產品比如手機需要集成很多芯片在一個基板上,整個系統的DPM是每個芯片的DPM乘積,因此每個芯片的DPM 需要控制在500以下以保證集成商可以低成本的生產出合格可靠的電子產品。

為了達到DPM的目標,半導體測試是保證芯片出廠品質所不能缺少的一步。而隨著半導體工藝的不斷下探1nm,量產工藝的總體yield也下降到80%左右,更多的產品生產故障率進一步要求更完備的半導體測試,否則低故障覆蓋率的測試會導致大量customer return,影響產品的量產上市時間。

半導體測試的數據結果也用于工藝監控和優化以及產品設計優化中。比如scan/mbist測試一般會將故障的具體信息存儲在數據庫,大量產品測試的這些故障信息會反標到wafer具體die上,甚至反標到layout的X/Y坐標上,如果有明顯的defect signature出現,工藝和設計就需要檢查是否有什么原因造成這種通用問題, 是否有可以改進的地方。

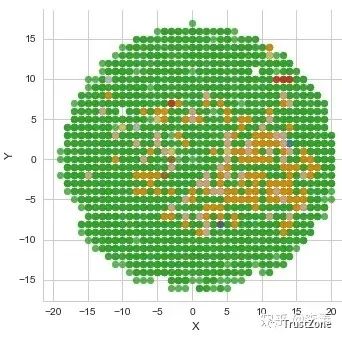

半導體測試也用stress加速老化測試,減少或者避免burn-in。burn-in一般需要125C/24h,目的是根據澡盆曲線,將早期失效的DUT通過stress篩選出來。

因為burn-in的時間一般很長,多數產品在ATE測試中加入超高電壓短時stress測試可以加速老化,用最短的stress時間快速篩選出早期失效的DUT。

DUT(Device Under Test)是指被測試的設備或部件。在這個上下文中,它指的是在燒機過程中被測試的設備或部件。

燒機(burn-in)是一種可靠性測試技術,目的是通過模擬產品在正常工作條件下的應力和環境因素,如溫度、濕度、電壓等,來檢測和識別出早期失效的產品。

芯片根據應用領域不同,Jedec會有不同的qualification的要求,一般qualification包括ESD/latchup,HTOL,TC,ELFR,HTS,THB等等。

無論哪種qualification,在stress之前要使用完備的ATE測試程序篩選出完好的芯片,在stress之后需要使用相同的程序做readout,判斷芯片是否經過stress后損壞。因此對于qualification而言ATE測試也是不可或缺的,需要在項目中和測試工程師合作制定可行的計劃。

是的,Jedec(固態技術協會)制定了許多關于半導體器件的測試和認證標準。在半導體行業中,qualification通常指的是產品或工藝的驗證過程,以確保它們符合特定的規格和要求。

在Jedec的標準中,不同的qualification可能有不同的要求,涵蓋了各種不同的測試和評估。以下是一些常見的Jedec qualification標準和它們的目的:

?ESD(Electrostatic Discharge):這是測試半導體器件對靜電放電的抵抗能力。ESD測試通常模擬實際操作環境中可能出現的靜電放電情況,以確定器件是否能夠承受這些潛在的應力。?Latchup:這是一種測試,用于評估半導體器件在遇到瞬態電壓時內部電路的保護能力。Latchup測試通常模擬潛在的電壓瞬變情況,以確定器件是否會遭受損壞或功能失效。?HTOL(High Temperature Operating Life):這是一種測試,用于評估半導體器件在高溫工作條件下的壽命和穩定性。HTOL測試通常暴露器件于高溫條件下,并監測其性能隨時間的推移而變化的情況。?TC(Thermal Cycling):這是一種測試,用于評估半導體器件在不同溫度循環下的可靠性和穩定性。TC測試通常暴露器件于一系列的溫度循環中,以模擬實際使用中可能出現的溫度變化。?ELFR(Early Life Failure Rate):這是一種測試,用于評估半導體器件在早期使用階段的故障率。ELFR測試通常通過加速壽命試驗來預測器件的早期故障率。?HTS(High Temperature Storage):這是一種測試,用于評估半導體器件在高溫存儲條件下的穩定性和可靠性。HTS測試通常將器件暴露于高溫條件下并監測其性能的變化情況。?THB(Thermal/Hybrid Bump):這是一種測試,用于評估半導體封裝中的焊球在經受溫度循環時的可靠性和穩定性。THB測試通常通過施加溫度循環來模擬實際使用中可能出現的溫度變化對焊球的影響。這些只是一些常見的Jedec qualification標準和它們的示例目的。實際上,根據不同的應用和產品要求,可能還有其他特定的qualification要求需要進行評估。通過執行這些測試和認證程序,可以確保半導體器件符合特定的性能和質量標準,并能夠滿足應用的需求。

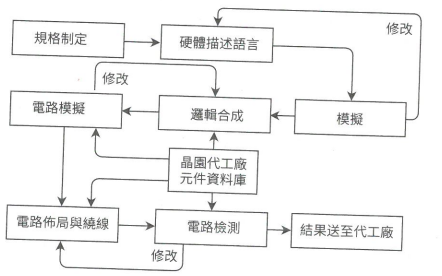

半導體測試流程

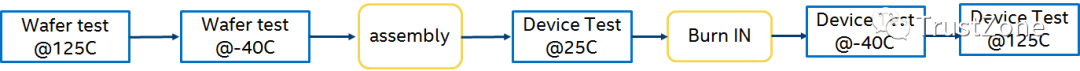

芯片根據應用領域,溫度和可靠性要求的不同,需要定義不同的test insertion。比如汽車電子的產品測試流程如下共有5個test insertion,如此多的test insertion是因為汽車電子的DPM要求zero defect,必須在不同溫度下多次測試最大限度地篩選新品。

而一般用于消費類比如手機通訊的芯片,因為不涉及生命和公共安全,DPM要求一般在500附近,因此測試的流程也盡可能的簡化去降低測試成本。如下圖所示,根據工藝在不同溫度對logic/sram的影響,決定wafer和device的測試溫度。

因為增加一個test insertion,測試成本就會顯著增加,產品利潤就會降低。因此半導體測試的一個重要工作是研究如何用盡量少的test insertion達到同樣的DPM目標。

以上圖為例,在項目的早期定下目標是“量產程序需要去除device test@cold,burn-in以及SLT”,在早期測試程序開發過程中,就需要研究嘗試如何在保留的test insertion中增加更多的測試(比如scan/mbist/IO stress測試,更嚴格的pass/fail limit等等),以達到篩選出同樣有問題的芯片。

如何定義不同test insertion的測試內容呢?概括而言是需要測試工程師根據故障概率,測試時間和測試條件的綜合評估而定。

wafer test使用探針卡+probe實現芯片與ATE機臺的電氣連接,一般而言探針卡的接觸電阻以及感性阻值較大,盡量避免測試頻率高的測試(限制在50M~100M以內),而將重點放在scan/mbist等故障率比較高的測試上,保證90%以上的defect可以在wafer level篩出而不浪費assembly和FT測試的cost。

FT測試一般在早期需要實現所有的測試以保證測試覆蓋率。除了篩選defect之外,一般FT測試還需trim一些analog模塊比如bandgap,reference current,reference resistance等等,以及其他一些需要將結果寫到fuse內的測試。

除了篩選缺陷之外,FT測試還需要進行一些模擬模塊的測試,例如bandgap、reference current和reference resistance等。這些測試用于模擬和測量芯片的內部電路和元件的性能,以確保它們符合設計規格和性能指標。

此外,FT測試還需要進行一些需要將結果寫到fuse內的測試。這些測試通常用于對芯片進行個性化配置或編碼,以確保每個芯片都具有正確的標識符、序列號或其他特定信息。這些信息可以通過編程寫入到芯片的fuse(熔絲)中,用于后續的識別、追蹤和管理。

SLT一般使用類似系統應用板搭建的mini-system執行系統應用軟件,篩選出無法用DFT的故障模型表征的defect,或者是ATE機臺受限的一些和性能相關的功能測試。但是因為SLT測試不容易提供工藝和設計改進需要的具體數據,一般需要在量產過程中提高ATE測試的故障覆蓋率以及有效性,最大限度地減少進入SLT測試的defect device的數量,最終目標是去除SLT測試。

ATE測試抽象模型

業界用于SoC產品測試的ATE測試機臺主要由兩家提供:

?Teradyne:J750 (low cost) and UltraFlex (high performance)?Advantest: V93000 and T2000

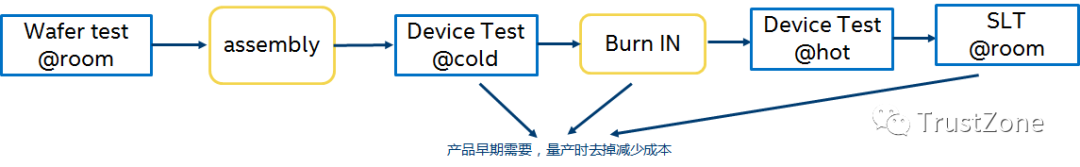

盡管各個機臺各有特點,但主要的功能是一致的,可以用下圖抽象。

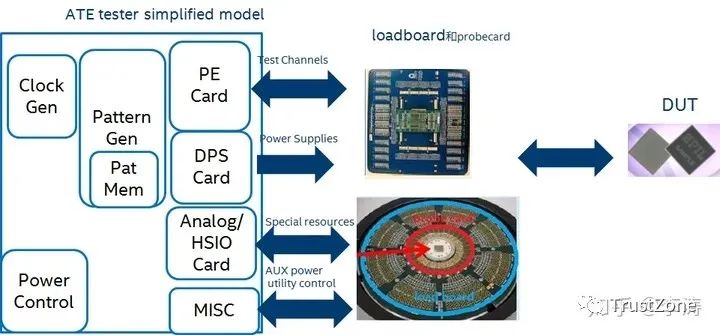

ATE測試機臺提供測試需要的硬件資源,測試板(wafer使用探針板probecard,device使用loadboard)實現待測芯片和ATE測試機臺的物理電氣連接。

基于這個硬件系統,測試工程師開發ATE的測試軟件程序,實現各種測試。

下面簡要介紹一些通用SoC測試機臺的基本模塊及功能:

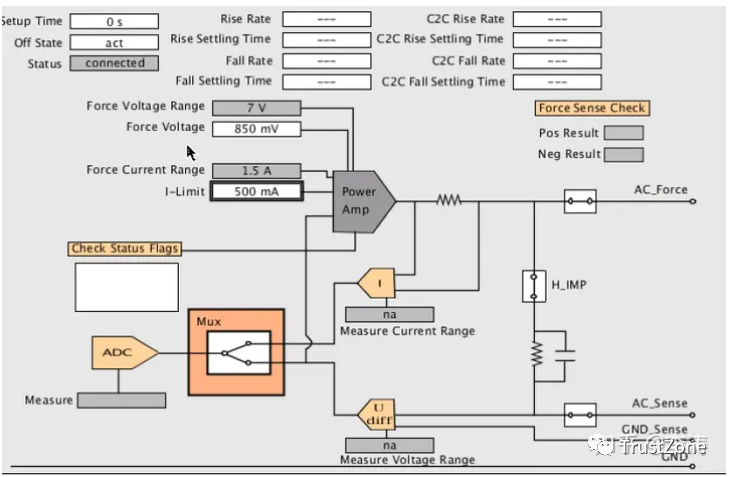

?clock Generation模塊提供各個板卡需要的時鐘信號,保證所有時鐘同源同相。在定義測試程序的timing的時候,需要綜合考慮機臺的這個最大基頻和最小period resolution,保證機臺可以盡可能高精度的提供芯片測試需要的各種時序信號;?Pattern Gen模塊控制測試程序的測試激勵(Pattern)按照定義的timing時序執行,它是tester的核心模塊;?PE Card模塊提供通用Tester channel,一般連接SoC的IO。通用tester channel可以提供輸入激勵,采樣DUT輸出;集成PPMU進行電流電壓的測試;強大的tester支持protocol編程支持業界通用的串行總線協議;

?DPS 模塊給待測DUT提供電源supply,一般支持動態電流測試,高級的支持紋波擾動測試以及IFVM模式(current force voltage measure);

?不同的SoC tester會提供不同的模擬信號或數字高速板卡,支持不同的測試需求。一般AWG(analog waveform generation)和Digitizer是多數SoC芯片測試需要的板卡;如果SoC芯片的HSIO IP支持內建自測試,高速數字板卡就不是必須的;?測試機臺還需要提供一些Auxillary Power比如15V/12V/5V, 繼電器控制需要的utility bits等等;甚至有些tester會提供usb/pcie的接口;

半導體測試的基本內容

半導體芯片有各種類型,不同類型的芯片測試內容不同。以通訊類基帶SoC芯片為例,半導體測試程序需要包括以下測試,具體測試原理可以參照。

?參照:[1]

Pad相關測試

涵蓋IO contact,Pad leakage,Pad pullup&pulldown,輸入輸出VIX/VOX/IOX測試以及輸出阻抗測試。測試原理很簡單,是基于歐姆定理進行電流電壓的測量。但該類測試可以有效篩選出pad/bump/ball相關的故障,該類故障多發生在wafer切割,assembly/package等工序,以及qualification的一些stress測試。

ESD/Latchup的測試程序需要實現完備的Pad測試,保證stress損壞的defect可以篩選出來。

Power電流相關測試

涵蓋SICC(static/leakage current),DICC(dynamic work current)以及休眠電流。測試可以評估DUT的功耗指標,根據用戶對功耗的要求將產品分為不同類別。采用PAT(Part Average Testing)技術,可以使用adaptive test limit的方式將功耗異常的芯片篩選出來。

Performance相關測試

一般core/cpu/dps需要測試最大工作頻率,最低工作電壓等性能相關的參數,這些測試結果用于產品分類以及系統軟件運行時DVFS(Dynamic voltage and frequency scaling)的具體設置。

Scan測試

數字logic的故障覆蓋率主要是DFT的scan保證的,大部分產品的scan覆蓋率在95%以上。Scan測試激勵是基于故障模型(stuck-at fault,transition fault,bridge fault...等等)由EDA工具生成。相比較于傳統功能激勵測試,優勢是可以用最少的測試時間獲得最大的故障覆蓋率,同時一般不需要高速的測試機臺,也避免了DUT和測試機之間的異步通訊要求,而且DUT測試失敗可以反標回具體的設計電路,便于后期的分析。

Scan測試主要取決于DFT/DFM的設計,需要在設計階段就覆蓋率,故障模型,vector大小,shift時的脈沖電流等等進行充分溝通。

Mbist測試

Sram在SoC中占據很大的面積,和數字邏輯類似,Sram有很成熟的內建自測試方案mbist保證100%的故障覆蓋率。Sram也有多種故障模型(stuck-at,transition fault,address fault,Coupling fault, Neighborhood sensitivity,Stability Fault,Retention Fault等),需要根據工藝的穩定度以及DMP要求,選擇多種mbist的算法保證測試強度。

mbist測試需要支持redundancy的修補,repair的測試流程需要不斷優化,保證可以將多數weak cell用完好的redundancy cell替換掉。

為了支持工藝優化,量產程序還需要能夠將sram defect的信息輸出到后臺數據庫中,經過大數據分析,一些工藝或設計的缺陷可以暴露加以改正。

高速數字接口測試

SoC一般集成很多數字高速接口,常見的比如USB,MIPI,PCIE,SATA..等等。這些接口的data rate在2GHz以上,多數ATE測試機的普通PE Card是無法支持如此高的頻率,而選取高速板卡意味著測試成本的大幅提高,而且不容易在OAST尋找到合適的測試機臺。

一般DFT可以在這些phy中實現TX/RX的loop back,使用類似bist的方式發送PRBS數據并采回,通過修改內部比較電壓和采樣時間自動測試眼圖。

DC參數的測試一般需要參照datasheet,在設計階段需要和DFT溝通保證重要的DC參數可以測試;

Analog模塊測試

涵蓋了PLL,LDO,bandgap, OSC.... 等等。測試需求來自這些IP的設計者,需要在設計階段討論定義,并尋求DFT的支持避免對ATE測試機的過高要求。

-

測試

+關注

關注

8文章

5269瀏覽量

126599 -

半導體

+關注

關注

334文章

27290瀏覽量

218099 -

封裝

+關注

關注

126文章

7873瀏覽量

142896

原文標題:參考資料

文章出處:【微信號:IC學習,微信公眾號:IC學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體制程

半導體測試解決方案

半導體與芯片器件研究測試方案匯總【泰克篇】

半導體電阻率測試方案解析

我國半導體封裝市場概述

半導體制造教程之工藝晶體的生長資料概述

半導體測試概述

半導體測試概述

評論