咬尾中斷

Cortex-M3 內核發生中斷時,硬件會自動將 XPSR、PC、LR、R12、R3、R2、R1 和 R0 這 8 個寄存器壓入棧,其余的 R4~R11、LR、XPSR 寄存器的備份則需要由 C 編譯器去做。

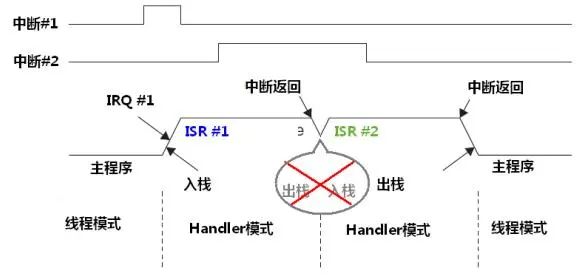

我們知道每次中斷操作有三部曲:入棧+ISR+出棧。**Cortex-M3 內核支持中斷嵌套。所謂中斷嵌套就是高優先級的中斷可以打斷低優先級的中斷轉而去執行高優先級的中斷服務程序,當高優先級中斷服務程序執行完畢再去接著執行低優先級的中斷服務程序。

若在高優先級中斷服務程序執行過程中產生了低優先級中斷,那么低優先級中斷需要等高優先級中斷服務程序執行完畢才能去執行。

對于后者兩個中斷是串行執行的,如果按照每個中斷備份、恢復寄存器的過程,那么高優先級中斷先將上述 8 個寄存器壓入棧中,等執行完畢再從棧中彈出這 8 個寄存器,緊接著低優先級中斷再將這 8 個寄存器壓入棧中,等執行完畢再從棧中彈出,這么做對這 8 個寄存器重復入棧出棧 2 次,浪費了時間,Cortex-M3 內核采用咬尾中斷機制避免這種問題發生,來看下圖:

Cortex-M3不會再出棧這些寄存器,而是繼續使用上一個異常已經壓棧好的結果,消除出棧和入棧操作的耗時。這樣一來我們執行兩次中斷只需要:入棧+ISR1+ISR2+出棧。

咬尾中斷看上去好像后一個異常把前一個的尾巴咬掉了,前前后后只執行了一次PUSH/POP操作。這兩個異常之間的“時間溝”就變窄了很多,大大提高了效率!

與常規中斷處理(ARM7)的比較:

晚到中斷

Cortex-M3的中斷處理還有另一個機制,它強調了優先級的作用,這就是 “晚到的異常處理” 。

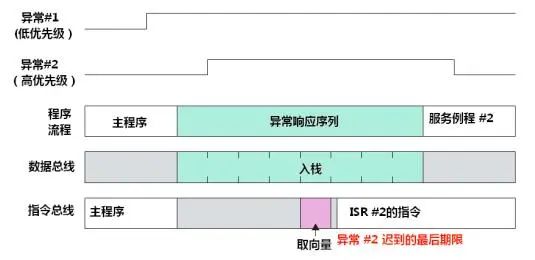

這里有一種情況,低優先級中斷先發生,而在低優先級中斷壓棧的過程中又發生了高優先級的中斷,這時高優先級中斷就會搶占低優先級中斷,如果高優先級中斷再壓棧然后執行,再出棧,低優先級中斷執行再出棧,這樣對這 8 個寄存器又是重復入棧出棧 2 次,做了無用功,Cortex-M3 內核采用晚到中斷機制避免這種問題發生,來看下圖:

比如,若在響應某低優先級異常#1的早起,檢測到了高優先級異常#2,則只要#2沒有太晚,就能以“晚到中斷”的方式處理,在入棧完畢后執行ISR#2。如圖所示:

如果異常#2來得太晚,以至于已經執行了ISR#1的指令,則按普通的搶占處理,這會需要更多的處理器時間和額外32字節的堆棧空間。在ISR#2執行完畢后,則以“咬尾中斷”的方式來啟動ISR#1的執行。

-

處理器

+關注

關注

68文章

19833瀏覽量

233965 -

寄存器

+關注

關注

31文章

5427瀏覽量

123743 -

Cortex-M3

+關注

關注

9文章

276瀏覽量

60174 -

中斷優先級

+關注

關注

0文章

22瀏覽量

9545 -

中斷嵌套

+關注

關注

0文章

7瀏覽量

6989

發布評論請先 登錄

Cortex-M3處理器中斷與FreeRTOS中斷優先級配置

STM32的Cortex-M3中斷異常處理

Cortex-M3 NVIC與中斷控制資料下載

Cortex-M3的異常和中斷資料下載

Cortex-M3和Cortex-M4 Fault異常應用之基礎知識資料下載

Cortex-M3工作模式、異常與中斷介紹資料下載

STM32的NVIC與中斷簡介&&Cortex-M內核的識別

STM32 的核心Cortex-M3 處理器

Cortex-M4和Cortex-M3內核的systick不進中斷的軟件延時

評論