學(xué)術(shù)界和工業(yè)界已經(jīng)提出將二維(2D)過渡金屬二摻雜化合物(TMD)半導(dǎo)體作為未來取代物理柵極長度小于10納米的硅晶體管的一種選擇。在這篇評論中,我們分享了基于堆疊二維TMD納米帶制造互補(bǔ)金屬氧化物半導(dǎo)體 (CMOS) 器件的最新進(jìn)展,并特別強(qiáng)調(diào)了二維界在五個關(guān)鍵研究領(lǐng)域仍需解決的問題:接觸、溝道生長、柵極氧化物、可變性和摻雜。雖然二維TMD晶體管具有巨大的潛力,但還需要更多的研究來了解二維材料在原子尺度上的物理相互作用。

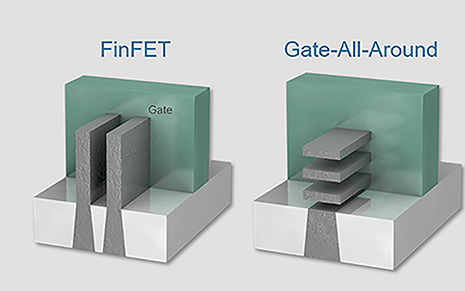

學(xué)術(shù)界和工業(yè)界已經(jīng)提出了二維TMD半導(dǎo)體(如MoS2、WSe2等)作為硅(Si)晶體管的潛在替代品,其物理柵極長度為10納米以下,采用全柵極(GAA)堆疊納米帶(NR)1,2,3,4。GAA NR的靜電特性決定了當(dāng)物理柵極長度縮小到10納米以下時,半導(dǎo)體溝道的厚度必須大大降低到5納米以下,才能保持低于70 mV/dec 的亞閾值擺幅 (SS),從而有效地關(guān)閉晶體管。如果沒有較低的SS,晶體管要么會在關(guān)斷狀態(tài)泄漏過多電流,要么需要更高的電壓才能工作。

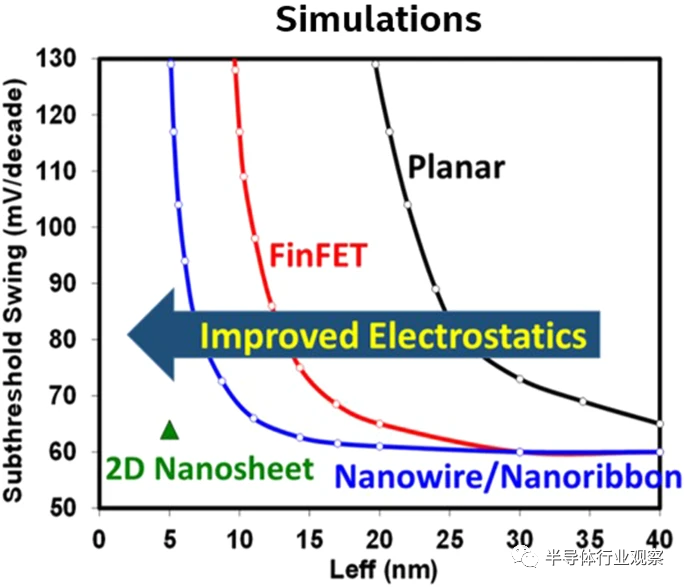

我們在圖 1 中使用密度泛函理論 (DFT) 原子模擬對各種器件幾何形狀的二維納米片計算出的 SS 進(jìn)行了比較,從而說明了這一點(diǎn)。在柵極長度小于 10 nm 的情況下,源極和漏極之間的直接隧穿預(yù)計會導(dǎo)致硅晶體管和其他傳統(tǒng)體晶體管的高離態(tài)漏電。TMD 的大帶隙及其高有效質(zhì)量抑制了源極和漏極之間的直接隧穿,從而使關(guān)態(tài)電流保持在較低水平。此外,硅的遷移率會隨著溝道厚度的減小而降低,而二維 TMD 的遷移率卻能保持不變5。這為二維 TMD 晶體管在 10 納米以下物理柵極長度或 1 納米以下節(jié)點(diǎn)取代硅提供了機(jī)會。

然而,向新半導(dǎo)體材料過渡的實(shí)際可行性和時間安排仍是一個懸而未決的問題。在取代硅之前,二維界需要解決許多難題。在這篇評論中,我們將闡述二維 TMD 的一些有前途的特性,并強(qiáng)調(diào)目前阻礙半導(dǎo)體行業(yè)采用這些材料的問題。

圖 1:各種晶體管幾何形狀的閾下擺幅 (SS) 與溝道長度的比較,說明二維納米片的優(yōu)勢。

半導(dǎo)體幾何形狀(平面、FinFET、納米帶和二維納米片)的SS與Leff(柵極長度)的模擬顯示,在物理柵極長度小于10 nm時,二維過渡金屬二鈣化物的靜電與硅相比具有競爭性。二維納米片SS是通過原子密度泛函理論計算得出的,而其他幾何形狀則是通過靜電求解得出的。

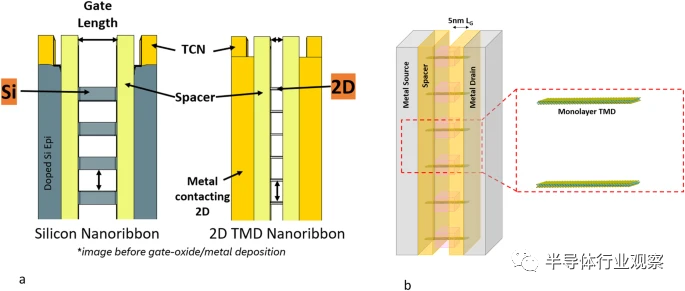

半導(dǎo)體器件的未來將以堆疊GAA NR結(jié)構(gòu)為中心,與硅GAA NR相比,二維TMD具有獨(dú)特的擴(kuò)展優(yōu)勢。圖2顯示了堆疊硅 GAA NR 和堆疊二維TMD GAA NR晶體管在同等高度上的橫截面,以考慮到常見的工藝集成因素,包括蝕刻晶體管堆疊所面臨的挑戰(zhàn)。二維TMD GAA NR結(jié)構(gòu)的優(yōu)勢顯而易見,因為在相同的體積內(nèi)可以放置更多的二維TMD NR。具體來說,相同的柵極高度可以容納6個2D TMD NR,而Si NR只有4個。這樣,即使單個TMD納米片的性能低于單個硅納米片,相同尺寸的 2D TMD GAA NR 晶體管也能達(dá)到比硅更高的性能。

圖 2:具有相同物理高度的堆疊納米帶晶體管示意圖。

物理高度相同的疊層全柵極 (GAA) 硅晶體管與疊層 GAA 二維 TMD 納米帶 (NR) 晶體管的截面圖對比。假設(shè)柵極氧化物和柵極金屬沉積體積相同,則四個堆疊硅 NR 的高度與六個堆疊二維 TMD NR 的高度相同。因此,二維 TMD 驅(qū)動電流只需達(dá)到硅驅(qū)動電流的 2/3,就具有競爭力。b.面板顯示的是相同的圖紙,但以二維 TMD 薄膜的單個原子為比例。金屬觸點(diǎn)用灰色表示,間隔電介質(zhì)用黃色表示,柵極氧化物用粉紅色表示。柵極金屬未顯示。“Advancing 2D monolayer CMOS through contact, channel and interface engineering,” 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2021, pp. 7.1.1–7.1.4, https://doi.org/10.1109/IEDM19574.2021.9720651.

制造二維 TMD 晶體管面臨的挑戰(zhàn)

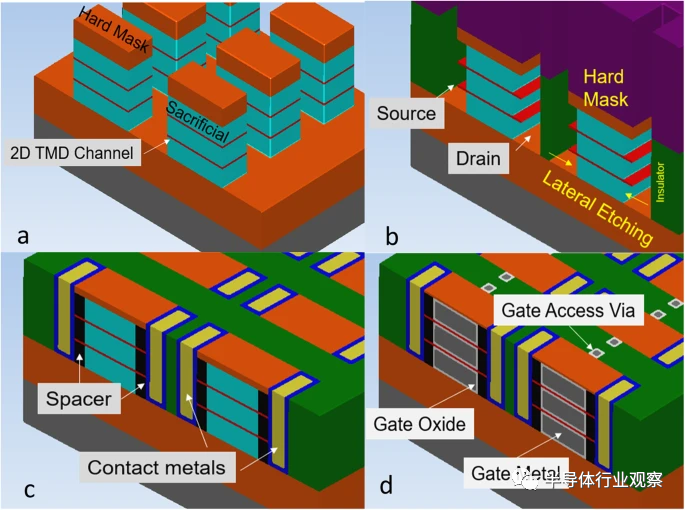

制造二維 TMD NR 晶體管必須包括以下關(guān)鍵工藝步驟:(1) 二維 TMD 的沉積,(2) 疊層 NR 溝道的形成,(3) 間隔區(qū)的摻雜,以及 (4) 源極/漏極接觸區(qū)和柵極氧化物/金屬區(qū)的沉積。在圖3中,我們分享了一個簡化的二維TMD疊層NR集成方案,以提請讀者注意目前文獻(xiàn)中報道較少的挑戰(zhàn)。在圖 3a 中,我們展示了一個切割后的二維疊層 NR 結(jié)構(gòu)圖像,二維片之間有一個犧牲氧化層隔開,這揭示了制造過程中眾多挑戰(zhàn)中的第一個,即蝕刻對二維溝道性能的影響。在最終產(chǎn)品中,由于 NR 的寬度可以小到 5-10 nm,因此 NR 邊緣的缺陷和邊緣終止可能會影響器件的性能。在圖 3b 中,我們展示了使用定向和各向同性蝕刻形成間隔區(qū)的過程。現(xiàn)代硅技術(shù)中使用的許多蝕刻溶液并不能轉(zhuǎn)化為二維 TMD 疊層 NR 結(jié)構(gòu),而且人們對干法、濕法和氣相蝕刻化學(xué)法與二維 TMD 的相互作用仍然知之甚少。因此,我們需要能在不損害 TMD 單層的情況下去除周圍材料的選擇性化學(xué)方法。

圖 3:將二維TMD沉積或轉(zhuǎn)移到犧牲氧化物上的簡化二維TMD疊層NR集成方案。

為便于說明,我們將圖片限定為兩個堆疊的 NR。紅色代表 TMD,淺藍(lán)色代表犧牲膜(可以是氧化物或其他材料)。a對堆疊的二維 TMD NR 進(jìn)行蝕刻。b 側(cè)面蝕刻,打開源極和漏極接觸區(qū),形成內(nèi)部間隔。c通過大馬士革工藝(damascene process)形成金屬觸點(diǎn)(藍(lán)色和黃色層)。d通過原子層沉積 (ALD) 工藝蝕刻通路以填充柵極氧化物(淺灰色)和金屬(深灰色),從而形成柵極。請讀者注意,由于二維TMD范德華(van der Waals)材料的性質(zhì),柵極氧化物沉積具有獨(dú)特的挑戰(zhàn)性。典型的原子層沉積工藝依賴于懸掛鍵進(jìn)行材料成核,但無缺陷的二維 TMD不存在懸掛鍵。

在圖3c和d中,我們展示了源極/漏極接觸和柵極氧化物/金屬沉積的形成過程。要形成源極/漏極接觸區(qū),必須考慮兩個關(guān)鍵因素:暴露的二維薄膜面積和暴露材料的質(zhì)量,后者可能會因蝕刻工藝而改變。雖然特定的制造方案可以在接觸區(qū)暴露出更大面積的二維薄膜,但也可能使二維 TMD 表面質(zhì)量下降,從而增加接觸電阻或?qū)е?a target="_blank">機(jī)械不穩(wěn)定性。其他沒有明確解決方案的挑戰(zhàn)是如何摻雜間隔物下的二維薄膜,以及最佳方案是依靠置換摻雜還是遠(yuǎn)程電荷摻雜。

由于TMD在制造過程的多個階段僅在2或3個面上得到支撐,因此單層薄膜的機(jī)械堅固性非常令人擔(dān)憂。例如,在圖3b中,TMD 層只有兩面受到綠色絕緣層的支撐,一面受到藍(lán)色犧牲氧化層的支撐,剩下的一面在內(nèi)層間隔物沉積之前對空氣開放。幸運(yùn)的是,TMD的特點(diǎn)是單層 MoS26 的楊氏模量(robust Young’s)高達(dá)約 270 兆帕,而 Si7為 130-188 兆帕。在制造過程中,內(nèi)應(yīng)力和周圍薄膜熱膨脹的影響可能是一個問題,如果使用濕蝕刻工藝,毛細(xì)管塌陷也是一個問題。考慮到這些因素,我們需要更多的非侵入式解決方案來蝕刻 TMD周圍的薄膜,同時又不破壞其特性。一種緩解策略是在制造 TMD 納米帶時加入犧牲背層,以提供機(jī)械支撐。

接觸區(qū)和間隔層下的摻雜也將是未來 TMD 器件面臨的一項挑戰(zhàn)。目前,摻雜 TMD 材料有兩種通用方法,一種是置換摻雜,另一種是遠(yuǎn)程電荷摻雜。過去,通過將摻雜原子高能植入硅晶格來實(shí)現(xiàn)硅的置換摻雜。然而,由于 TMD 的單層性質(zhì),這種方法無法應(yīng)用于疊層 TMD 納米帶。替代性摻雜需要重新生長 TMD 薄膜或極其復(fù)雜的制造技術(shù)。TMD 的另一種獨(dú)特可能性是在通道附近放置偶極子電荷,以有效摻雜相關(guān)區(qū)域。然而,這種策略可能會引入來自相同偶極子的潛在庫侖散射(coulomb scattering ),因此需要進(jìn)一步調(diào)整。

與硅一樣,納米帶堆疊結(jié)構(gòu)的選擇也會對多個領(lǐng)域和設(shè)計決策產(chǎn)生深遠(yuǎn)影響8。在圖 3 中,我們分享了一種制造堆疊納米帶結(jié)構(gòu)的方法,該方法基于單一類型的 TMD 作為 NMOS 和 PMOS 器件的半導(dǎo)體通道。對于堆疊在PMOS路線上的NMOS,有可能為 NMOS 和 PMOS 晶體管分別使用不同的材料。由于要權(quán)衡驅(qū)動電流和電池電容,這些結(jié)構(gòu)的最佳設(shè)計仍是一個未決問題。

在二維TMD上沉積柵極氧化物

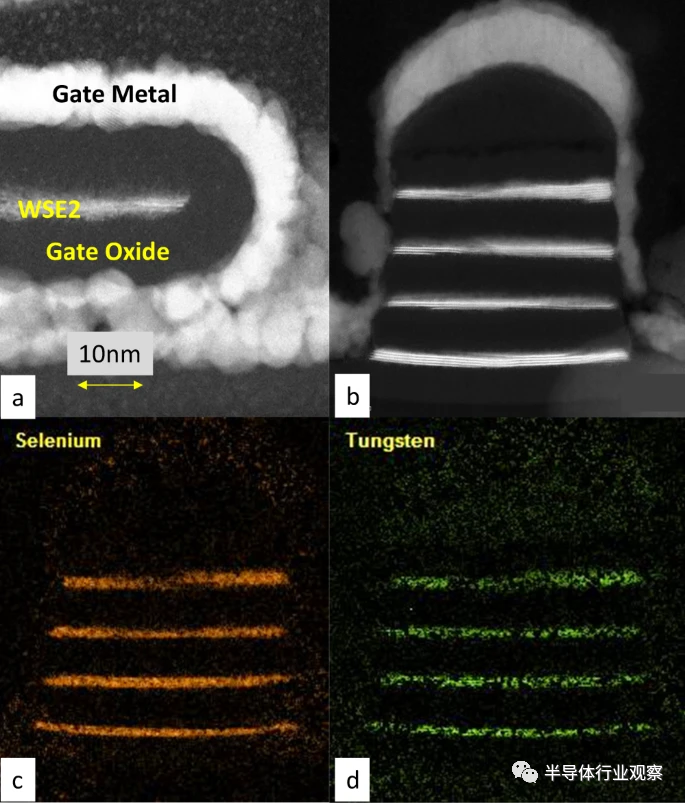

沉積符合嚴(yán)格的可靠性和等效氧化物厚度 (EOT) 要求的柵極氧化物仍然是一個持續(xù)的研究課題9,10。例如,柵極氧化物厚度需要擴(kuò)展到約1nm的電氣EOT,同時滿足氧化物擊穿要求,以及基于體積限制的<3 nm的物理厚度。圖3d顯示了柵極氧化物/金屬沉積的示例。二維TMD是沒有懸鍵的范德華材料(van der Waals materials )。由于原子層沉積 (ALD) 依賴于懸鍵來啟動生長并可控地合成有限的介電厚度,因此在具有最小缺陷的二維 TMD 表面進(jìn)行柵極氧化物的 ALD 生長是一項重大挑戰(zhàn)。我們以前曾報道過物理吸附可以增強(qiáng)柵極沉積10,而破壞較厚的TMD作為替代柵極的策略可能會產(chǎn)生不必要的滯后,在柵極長度低于10 nm時無法達(dá)到低SS。在圖 4a 中,我們展示了GAA沉積,但要獲得理想的最終產(chǎn)品,仍需解決器件集成的難題。此外,器件可能無法通過可靠性測試。柵極堆疊技術(shù)的另一個相對尚未探索的方面是使用不同的工作函數(shù)金屬或偶極層來設(shè)置多個NMOS和 PMOS 門限電壓。如果要在前端晶體管技術(shù)中使用二維材料,這是一項關(guān)鍵要求。

圖4:二維TMD納米帶的透射電子顯微鏡 (TEM) 截面圖像。

a.帶有GAA氧化物和金屬的二維 TMD NR,尺寸欄為 10 納米。b-d.帶有Se和W TEM HAADF信號的四個疊層二維 WSe2 NR。

現(xiàn)實(shí)的二維TMD生長要求

盡管過去10年中在二維TMD生長質(zhì)量方面取得了重大進(jìn)展,但這一領(lǐng)域的研究仍需繼續(xù)。50多年來,硅一直是晶體管的首選材料,其原因之一就是存在缺陷密度極低的晶體外延生長工藝。二維TMD生長目前還沒有達(dá)到單晶水平:已經(jīng)證實(shí)晶粒尺寸大于10微米,但很少能獲得晶圓級無缺陷單晶薄膜11。二維TMD沉積通常是一個隨機(jī)過程,在晶圓上的隨機(jī)位置開始生長,晶體橫向生長,最終合并成多晶材料。由于大多數(shù)生長技術(shù)都具有隨機(jī)性,晶界的隨機(jī)分布會導(dǎo)致不同器件的溝道質(zhì)量存在差異。如果傳輸特性存在顯著差異,器件性能的變異性就會過大,無法滿足現(xiàn)代電路設(shè)計的要求2。為了規(guī)避這一問題,我們之前已經(jīng)引入了在確定位置選擇性生長 TMD 晶體的方法,但這種方法也面臨著自身的集成挑戰(zhàn)12。進(jìn)一步發(fā)展二維 TMD 沉積技術(shù),生產(chǎn)出具有大晶粒尺寸和低缺陷密度的凝聚單層薄膜,將有助于縮小高質(zhì)量硅外延和二維 TMD 生長之間的差距。值得注意的是,這個問題也可能是一個干擾因素,因為晶體管的驅(qū)動電流通常由10納米以下柵極長度的接觸電阻所主導(dǎo)。因此,溝道遷移率的變化可能與驅(qū)動電流的變化關(guān)系不大。

接觸電阻

TMD的接觸電阻可以說是需要解決的最關(guān)鍵問題,在過去幾年中,相關(guān)領(lǐng)域已經(jīng)取得了重大進(jìn)展。盡管如此,如果要使TMD達(dá)到商用半導(dǎo)體產(chǎn)品的水平,還需要繼續(xù)研究二維TMD 的 NMOS 和 PMOS接觸電阻。隨著銻(Sb)和鉍(Bi)等半金屬的引入,NMOS接觸電阻在過去幾年中取得了快速進(jìn)展。Bi的熔點(diǎn)較低,僅為 271°C,而Sb則能在 BEOL 溫度下進(jìn)行加工,因此更受青睞1,13。然而,這些半金屬能否在10-20 納米的物理接觸尺寸要求下達(dá)到嚴(yán)格的接觸電阻率目標(biāo),目前仍是未知數(shù)。PMOS接觸電阻仍然是一個難以捉摸的問題。我們發(fā)現(xiàn),如果WSe2的質(zhì)量足夠好,Ru等金屬是PMOS WSe2系統(tǒng)的良好候選材料1。二維材料的接觸電阻仍然是二維TMD性能的致命弱點(diǎn),我們強(qiáng)烈鼓勵在這一領(lǐng)域開展更深入的研究。

由于前端硅晶體管正在轉(zhuǎn)向GAA NR架構(gòu),因此二維TMD也將采用類似的幾何結(jié)構(gòu),以提高競爭力。這就帶來了一個潛在的問題,因為大多數(shù)已發(fā)表的試圖解決接觸電阻問題的作品都是基于蒸發(fā)頂部觸點(diǎn),而最簡單的NR晶體管制造卻默許使用邊緣觸點(diǎn),如圖 3c 所示。通過改變圖3c中的蝕刻順序,使內(nèi)隔板向柵極蝕刻的程度大于圖中所示的程度,就有可能用ALD金屬制作出部分環(huán)繞觸點(diǎn)。但是,這可能會影響晶體管密度。另一種方法是在接觸區(qū)重新生長TMD。在這種情況下,我們鼓勵科學(xué)界向GAA架構(gòu)發(fā)展,因為未來的器件學(xué)習(xí)將提供寶貴的反饋,并加速實(shí)現(xiàn)潛在的集成。

未來方向

總之,我們強(qiáng)調(diào)了二維 TMD 晶體管有機(jī)會取代硅晶體管的原因,特別是在10納米以下的柵極長度。此外,我們還強(qiáng)調(diào)了需要進(jìn)行更多學(xué)術(shù)和工業(yè)研究的領(lǐng)域,以及實(shí)現(xiàn)這一轉(zhuǎn)變的基本認(rèn)識。這些重要領(lǐng)域中的每一個,即 (1) 二維 TMD 的沉積,(2) 堆疊 NR 溝道的形成,(3) 間隔區(qū)的摻雜,以及 (4) 源極/漏極區(qū)和柵極氧化物/金屬區(qū)的沉積,都需要可行的可制造解決方案。此外,我們還注意到,雖然未來的硅器件架構(gòu)是以NR為基礎(chǔ)的,但目前的TMD文獻(xiàn)主要集中在背柵器件上。我們急需開展更多研究,以了解NR幾何形狀對二維 TMD晶體管性能的影響。我們必須認(rèn)識到,這有可能成為類似硅微電子革命的戰(zhàn)略拐點(diǎn)。現(xiàn)在是該領(lǐng)域令人興奮的時刻,我們鼓勵開展更多研究,以了解原子尺度的二維TMD NR 架構(gòu)的物理學(xué)和工程學(xué)。學(xué)術(shù)界和產(chǎn)業(yè)界都需要加快對這些結(jié)構(gòu)的研究和學(xué)習(xí),因為我們正在離開納米技術(shù)世界,進(jìn)入埃米時代。我們需要專注于制造、控制和理解極其復(fù)雜的系統(tǒng),在這些系統(tǒng)中,每個原子都至關(guān)重要。

來源:半導(dǎo)體行業(yè)觀察

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28165瀏覽量

227680 -

晶體管

+關(guān)注

關(guān)注

77文章

9881瀏覽量

139854 -

二維

+關(guān)注

關(guān)注

0文章

41瀏覽量

12073 -

TMD

+關(guān)注

關(guān)注

0文章

16瀏覽量

9670

原文標(biāo)題:2D晶體管的未來展望

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

應(yīng)用材料公司以技術(shù)助力極紫外光和三維環(huán)繞柵極晶體管實(shí)現(xiàn)二維微縮

什么是3d晶體管

應(yīng)對功耗挑戰(zhàn):晶體管技術(shù)方案面臨瓶頸

什么是GaN透明晶體管?

晶體管電路設(shè)計超詳細(xì)版(上部)

晶體管電路設(shè)計超詳細(xì)版(下部)

RESURF原理應(yīng)用于SOI LDMOS晶體管

一種由石墨烯和二維超導(dǎo)體制成的新型晶體管問世

剖析二維電子器件的高k介電薄膜——氟化鈣

評論