#共建FPGA開發(fā)者技術(shù)社區(qū),為FPGA生態(tài)點(diǎn)贊#

1.算法涉及理論知識(shí)概要

現(xiàn)代電子技術(shù)的不斷發(fā)展,很多應(yīng)用領(lǐng)域?qū)?a target="_blank">信號(hào)的頻率的準(zhǔn)確度和穩(wěn)定性要求越來越高,不僅需要單一的固定頻率,還需要多點(diǎn)頻率,如短波通信接收機(jī)要求在2~30MHz的范圍內(nèi)提供以100Hz為間隔的280000個(gè)通信頻道。一般的振蕩器已不能滿足要求,于是出現(xiàn)了高穩(wěn)定和高準(zhǔn)確的晶體振蕩器。但晶體振蕩器產(chǎn)生的只是單一頻率的信號(hào)或只能在很小范圍內(nèi)微調(diào)。然而,在通信、雷達(dá)、儀表、宇航等領(lǐng)域往往需要在一定頻率范圍內(nèi)提供一系列穩(wěn)定和準(zhǔn)確的頻率,為了解決既要頻率穩(wěn)定準(zhǔn)確,又要頻率能在很大范圍內(nèi)變化的問題,于是產(chǎn)生了頻率合成技術(shù)。

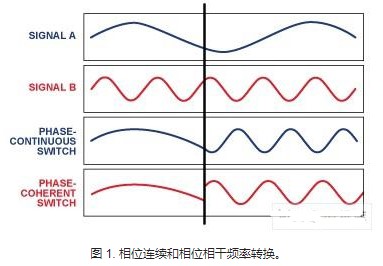

直接數(shù)字頻率合成技術(shù) (Direct Digital Synthesis)完全不同于我們己經(jīng)熟悉的直接頻率合成技術(shù)和鎖相環(huán)頻率合成技術(shù)。直接數(shù)字頻率合成技術(shù)(簡(jiǎn)稱DDS)的理論早在七十年代就被提出。它的基本原理就是利用采樣定理,通過查表法產(chǎn)生波形,由于硬件技術(shù)的限制,DDS技術(shù)當(dāng)時(shí)沒能得到廣泛應(yīng)用。隨著大規(guī)模集成電路技術(shù)的飛速發(fā)展,DDS技術(shù)的優(yōu)越性己逐步顯現(xiàn)出來。不少學(xué)者認(rèn)為,DDS是產(chǎn)生信號(hào)和頻率的一種理想方法,發(fā)展前景十分廣闊。與其他頻率合成方法相比較,直接數(shù)字頻率合成技術(shù)的主要優(yōu)點(diǎn)是易于程控,相位連續(xù),輸出頻率穩(wěn)定度高,分辨率高。其頻率分辨率可以達(dá)到10-3。而且頻率轉(zhuǎn)換速度快,可小于100ns,特別適宜用在跳頻無線通信系統(tǒng)。其相位噪聲主要決定于參考時(shí)鐘振蕩器。

DDS(Direct Digital frequency Synthesis)即直接數(shù)字頻率合成器,是一種新型的頻率合成技術(shù),具有較高的頻率分辨率,快速的頻率切換,穩(wěn)定性好,可靈活產(chǎn)生多種信號(hào)的優(yōu)點(diǎn)。因此,在現(xiàn)代電子系統(tǒng)及設(shè)備的頻率源設(shè)計(jì)中,尤其在通信領(lǐng)域,直接數(shù)字頻率合成器的應(yīng)用越來越廣泛。在數(shù)字化的調(diào)制解調(diào)模塊中。DDS取代了VCO(模擬的壓控振蕩器),被大量應(yīng)用。這種合成技術(shù)是一種利用數(shù)字技術(shù)來控制信號(hào)的相位增量的技術(shù),它采用插值取樣的方式,將要合成的正弦波波形用若干個(gè)采樣點(diǎn)的取值來代替,然后依次等時(shí)間間隔輸出這些取值,每個(gè)采樣點(diǎn)的值由預(yù)先存儲(chǔ)的數(shù)字值經(jīng)D/A轉(zhuǎn)換后得到。

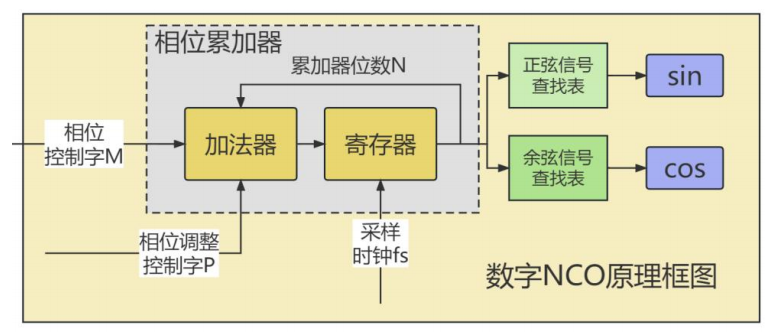

DDS工作原理框圖如圖1所示。其基本結(jié)構(gòu)包括:相位累加器PA、波形查詢表ROM、數(shù)模轉(zhuǎn)換器DAC及低通濾波器。

DDS的工作過程為:在參考時(shí)鐘fc的作用下,相位累加器對(duì)頻率控制字FCW(Frequency Control Word)進(jìn)行線性累加,將其高W位作為地址碼通過波形查值表ROM變換,產(chǎn)生D位對(duì)應(yīng)信號(hào)波形的數(shù)字序列,再由數(shù)模轉(zhuǎn)換器DAC將其轉(zhuǎn)化為階梯模擬電壓波形后由具有內(nèi)插作用的低通濾波器LPF將其平滑為連續(xù)的正弦波形作為輸出。

一個(gè)N位的相位累加器對(duì)應(yīng)相位圓2N上個(gè)相位點(diǎn),其最低相位分辨率為θmin=Δθ=2π/2N。在圖2中N為4,則有16個(gè)相位值和16個(gè)幅度碼相對(duì)應(yīng)。該幅度存儲(chǔ)于波形存儲(chǔ)器中,在頻率控制字FCW的作用下,相位累加器給出不同的相位碼,對(duì)波形存儲(chǔ)器尋址,完成相位--幅度變換,經(jīng)DAC變成階梯正弦波信號(hào),再通過低通濾波器平滑,便得到模擬正弦波輸出。

自第一部正弦波發(fā)生器問世以來,函數(shù)發(fā)生器的設(shè)計(jì)已經(jīng)發(fā)生了多次演進(jìn),在當(dāng)前數(shù)字領(lǐng)域中,大多數(shù)新型函數(shù)發(fā)生器都在采用直接數(shù)字頻率合成技術(shù)。DDS在大部分操作中使用數(shù)字電路,從而提供了數(shù)字操作擁有的許多優(yōu)勢(shì)。

第一,輸出信號(hào)的頻率精度可以達(dá)到作為發(fā)生器參考信號(hào)使用的晶體控制振蕩器的水平。如果想實(shí)現(xiàn)更高的精度,也可以采用函數(shù)發(fā)生器本身的溫度補(bǔ)償晶體振蕩器產(chǎn)生。

第二,DDS信號(hào)發(fā)生器的數(shù)字電路可以實(shí)現(xiàn)與數(shù)字電路相同的頻率精度。

第三,如果擁有RAM波形存儲(chǔ)器,那么DDS函數(shù)發(fā)生器可以重現(xiàn)幾乎任何波形。因此,函數(shù)發(fā)生器現(xiàn)在的功能要遠(yuǎn)遠(yuǎn)超過傳統(tǒng)函數(shù)發(fā)生器。對(duì)稱性可變的波形現(xiàn)在已經(jīng)是標(biāo)配功能,另外還可以內(nèi)置各種不常見的波形,如指數(shù)上升和下降型波形或正弦脈沖型波形等。但由于DDS的全數(shù)字結(jié)構(gòu),使得直接數(shù)字頻率合成器不可避免的擁有以下兩個(gè)缺點(diǎn)。

第一,其雜散分量豐富。這些雜散分量主要由相位舍位、幅度量化和DAC的非理想特性所引起。

第二,輸出頻帶受限。由于DDS內(nèi)部DAC和ROM的工作速度限制,使得DDS輸出的最高頻率受到極大的限制。

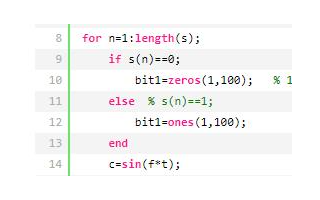

function a_ASK() i=10; j=5000; t=linspace(0,5,j); fc=10; fm=i/5; B=2*fc; %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%產(chǎn)生基帶信號(hào) a=round(rand(1,i));%隨機(jī)序列 st=t; for n=1:10 if a(n)

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603016 -

調(diào)制

+關(guān)注

關(guān)注

0文章

157瀏覽量

29664 -

DDS

+關(guān)注

關(guān)注

21文章

633瀏覽量

152631

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字調(diào)制(ASK、FSK、PSK)例程分享

PSK調(diào)制電路

DDS模塊

基于labview的4ASK 4FSK 4PSK 調(diào)制與解調(diào)程序 求好人發(fā)個(gè)

AD9954調(diào)制基帶板和DDS不同源頻譜很差

數(shù)字通信系統(tǒng)中的ASK調(diào)制技術(shù)

如何利用DSP Builder設(shè)計(jì)一種適合于軟件無線電使用的可控?cái)?shù)字調(diào)制器

基于FPGA的DDS調(diào)頻信號(hào)的研究與實(shí)現(xiàn)

基于FPGA的DDS信號(hào)源設(shè)計(jì)與實(shí)現(xiàn)

基于DDS與FPGA的FSK調(diào)制方式

DDS實(shí)現(xiàn)MSK信號(hào)調(diào)制

高效FSK/PSK調(diào)制器利用多通道DDS實(shí)現(xiàn)零交越切換

高效FSK_PSK調(diào)制器利用多通道DDS實(shí)現(xiàn)零交越切換介紹

利用AD9958/AD9959多通道DDS實(shí)現(xiàn)相位相干FSK調(diào)制器的設(shè)計(jì)

基于FPGA的DDS設(shè)計(jì),并通過DDS實(shí)現(xiàn)ASK,FSK,PSK三種調(diào)制(一)

基于FPGA的DDS設(shè)計(jì),并通過DDS實(shí)現(xiàn)ASK,FSK,PSK三種調(diào)制(一)

評(píng)論