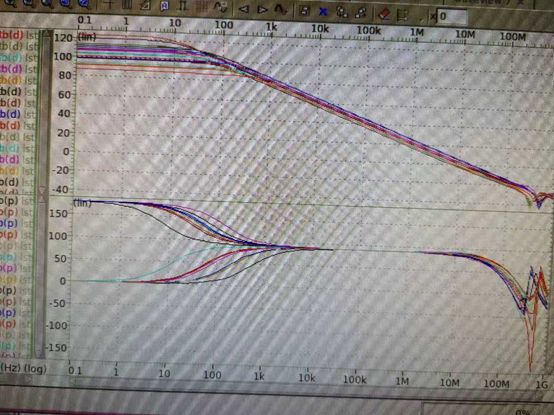

一個運放,使用電阻接成負反饋的形式,閉環放大倍數為-1。進行環路stb仿真,有些corner下相位曲線從0開始,但其他corner正常。這種是什么原因?該怎么解決?

注0:本文來源于某天微信群的討論。感謝提問者和解答****的大神們。

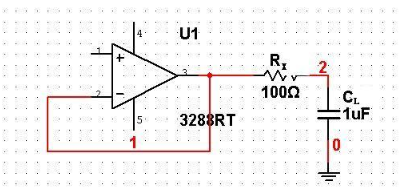

注1:本文涉及到的運放經確認是一個折疊式輸入,class AB輸出,使用電阻配置為閉環增益負一的運放。

注2:stb仿真指的是stability,主要仿的是電路的環路穩定性。

注3:由于某些“你懂的”原因,圖片只能拍照,無法截取高清圖。特補上另一個圖片,這個圖片來自于文末Designer guide網站。

電路上來說,確實是負反饋。如果相位從零開始,那么低頻時,豈不是正反饋?對于仿真器,如何計算的,大家是怎么理解的呢?

大神1給出了一個解答,原文如下:

這個問題來源應該是內部補償的minor loop還在導致的,如果沒有minor loop,stb仿真就不會出現這種問題。。。。stb用的Middlebrook那個double injection方法會常常出現這個問題,大家好像都忽略這個問題,沒看見誰去深究過這個主要是Middlebrrok的文章太難懂了...

這時,大神2補充道:

第一,spectre的STB仿真時基于“Middlebrook方法”,仿真時將輸入與輸出斷開,引入交流源,得到Tv=Vy/Vx 。第二,在反饋環路引入電流源ix、iy,Ti=iy/ix

仿真時假定Tv=T=LG。對于CMOS工藝,低頻gate阻抗無窮大,ix≈0,Ti∞,所以T≈Tv。高頻時,由于有漏電流,Ti不斷減小,T≠Tv。所以在低頻是得到的LG是一致的,高頻時會有一定區別在Ti大、Tv比較小情況下,由于spice是單獨計算Ti和Tv。若Tv非常小,spice計算出來的TV與實際值會有δTv的差值,經過很大的Ti放大后,最終得到的環路增益會有很大的誤差值。

大神1此時又做了更為詳盡的補充:

反正我估計這篇論文,包括我在內的大多數人看了也只能是知其然,但不知道其所以然。還是解釋不了為何某些corner會從0度開始,反正從我直覺上猜測是因為里面還有個小環路導致的。。。對于multi-loop的loop gain我也一直有些confuse,因為很明顯stb在不同地方加probe仿出來的phase margin是不一樣的,因為斷的位置不一樣確實也是不同的loop,如果按照middlebrook這個理論怎么更好的去解釋呢?

所有3-stage及以上的opamp論文都不看loop gain,穩定性就只看close-loop gain的極點是不是在左半平面,可以判斷是否穩定,但是close-loop gain是告訴不了你margin還有多少的,因此文章通常都是看階躍響應的ripple來估算。從mason定理來講,不管你in/out是哪個點,close-loop gain的分母永遠是一樣的,也就是說閉環極點是唯一的,所以穩定性也是確定的。所以感覺上stb仿真不管在哪里加probe,即使仿出來的phase margin有的大有的小也沒關系,反正都會是穩定的。隨便舉個例子,可能在某個地方斷環穩定性的PM隨pvt corner變化5070度之間,在另一個地方斷環PM在3540度之間,其實都是正確的,不要因為phasemargin不夠大而非要強行把后一個值也要做到60度,可能他值不大但是variation也比較小。

尤其是在做哪種leapfrog的filter的時候,可能某些結構在某些地方斷環的話,即使理想opamp也可能phasemagrin只有40度而已,這不代表opamp有問題,而是因為這些極點可能是filter的intrinsic pole @瓜在stb斷環時通常大家習慣在高阻地方斷環,也是為了Ti≈0,更簡單。但照理講Ti即使不等于0也是可以的。或者不說是斷環吧,就是指stb probe放的位置。

-

仿真器

+關注

關注

14文章

1017瀏覽量

83722 -

STB

+關注

關注

0文章

23瀏覽量

16580 -

CMOS工藝

+關注

關注

1文章

58瀏覽量

15672 -

漏電流

+關注

關注

0文章

262瀏覽量

17011

發布評論請先 登錄

相關推薦

運放的穩定性仿真分析

運放穩定性,你真的懂了嗎?

運放穩定性,你真的懂了嗎?

評論