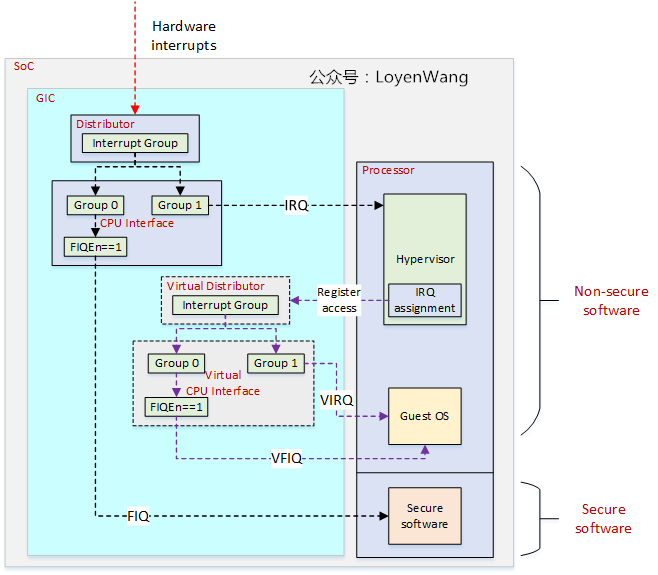

ARM cortex-A系列處理器,提供了4個管腳給soc,實現外界中斷的傳遞

? ?nIRQ:物理普通中斷

? ?nFIQ: 物理快速中斷

? ?nVIRQ: 虛擬普通中斷

? ?nVFIQ: 虛擬快速中斷

(2)gicv3和ARM Core的連接

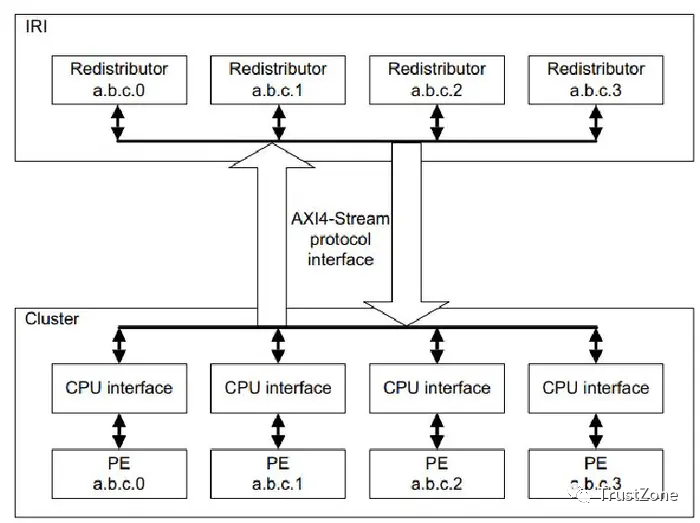

gicv3 AXI-stream協議

? ?gic stream協議,是基于AXI-stream協議。用于gic的IRI組件,和cpu interface之間,傳輸信息。

? ?distributor,redistributor和ITS,統稱為IRI組件(interrupt routing

infrastructure)。

? ?gic stream協議,包含以下2個接口:

? (1)下行AXI-stream接口:用于IRI向cpu interface傳遞信息,連接

? (2)上行AXI-stream接口:用于cpu interface向IRI傳遞信息

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ARM

+關注

關注

134文章

9087瀏覽量

367394 -

中斷

+關注

關注

5文章

898瀏覽量

41471 -

gic

+關注

關注

0文章

14瀏覽量

6270

發布評論請先 登錄

相關推薦

ARM GIC(一)之ARM soc中斷的處理介紹

的橋接器件,就是arm公司推出大名鼎鼎的gic,general interrupt controller。gic其實是一個架構,版本歷經了gicv1(已棄用),gicv2,gicv3,gicv4。對于

發表于 04-06 10:12

ARM GIC(二)之中斷術語的定義

ARM在GIC中,對于中斷,定義了如下的一些術語。一、中斷狀態對于每一個中斷而言,有以下4個狀態:?inactive:中斷處于無效狀態?pending:中斷處于有效狀態,但是cpu沒有響應該中斷

發表于 04-06 10:15

ARM GIC(三)之GICv2架構的組成及其功能簡析

ARM的cpu,特別是cortex-A系列的CPU,目前都是多core的cpu,因此對于多core的cpu的中斷管理,就不能像單core那樣簡單去管理,由此

發表于 04-06 10:26

ARM GIC(四) 之GICv3架構基礎知識介紹

的使用MPIDR_EL1寄存器,來標識core是一樣的。每個core,連接一個cpu interface,而cpu interface會連接gic

發表于 04-06 10:33

ARM GIC(八)GICv3架構的變化

GIC,是arm為了實現復雜的中斷控制,而定義的一套架構。版本也歷經了多個變化,從最初的GICv1到現在最新的GICv4。每一個新的版本,都增加了一些新的功能。目前最新的GIC-600 IP,支持

發表于 04-07 10:59

ARM GIC(十二) GICv3支持中斷bypass功能

在GICv2架構中,GIC與core之間,是直接通過irq,fiq管腳,傳遞中斷信號。但是在GICv3架構中,GIC通過gic stream接口向cpu interface傳遞中斷信息

發表于 04-08 10:10

ARM GIC電源管理使用手冊指南

背景介紹GIC電源管理,ARM官方手冊,只有一頁描述:1、在符合GICv3體系結構的實現中,CPU接口和PE必須位于同一個位置power domain,但它不必與關聯的Redistributor所在

發表于 05-27 16:41

ARM GIC對soc中外設中斷源的管理介紹

1、ARM GIC簡介與Linux中斷處理分析先簡單說明一下GICGIC即general interrupt controller。它是一個架構,版本歷經了GICv1(已棄用),GICv2

發表于 05-27 16:53

一文解析ARM GIC中斷線映射與GICD寄存器配置

1、ARM GIC中斷線映射與關鍵寄存器配置中斷生命周期generate:外設發起一個中斷distribute:distributor對收到的中斷源進行仲裁,然后發送給對應的cpu

發表于 05-27 17:24

淺談OpenHarmony LiteOS-A內核之基礎硬件——中斷控制器GIC400

公司功能更強大的Cortex-A/R系列的芯片,GIC是ARM公司給Cortex-A/R系列芯片提供的一個中斷控制器,在移植OpenHarmony LiteOS-A內核到特定板子的實踐中,我們遇到了很多

發表于 10-27 12:20

GIC是什么意思 GIC硬件原理

GIC硬件原理 ARM公司提供了一個通用的中斷控制器 GIC(Generic Interrupt Controller) , GIC 的版本包括 V1 ~ V4 ,由于本人使用的SoC

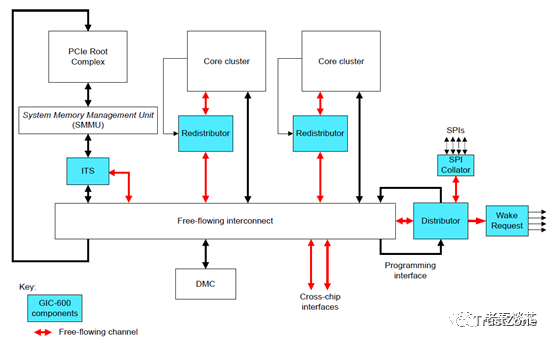

GIC-600的組件是如何連接的

為了適應大規模的SoC設計,GIC-600被設計成分布式IP。 所謂分布式,GIC-600由幾種組件構成,每個組件可以跟其它相關模塊在物理設計上擺放在一起,并與其擁有共同的電源域;組件之間通過片上網

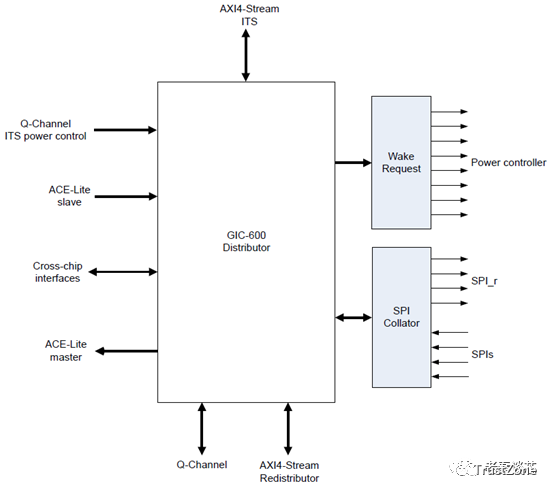

GIC-600的內部結構組件

所有的中斷,并轉發給相應的目標core。 圖3 GIC-600 distributor和SPI collator 對于core來說,可以通過上圖中的ACE-Lite slave接口訪問GIC

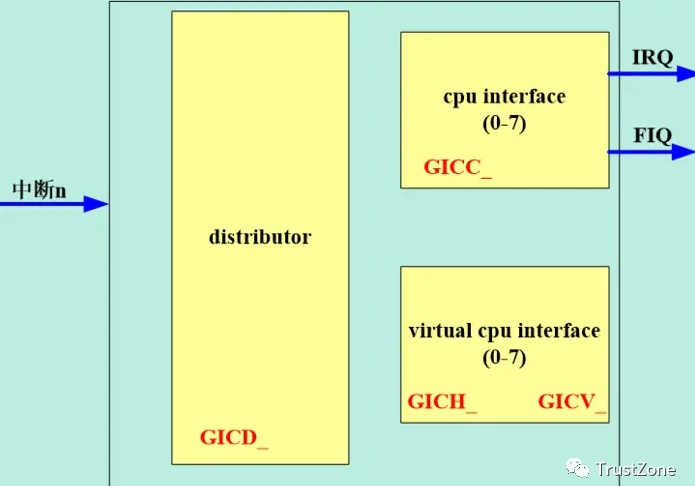

gic的組件介紹

的,根據配置決定中斷發往的core。最后選擇最高優先級中斷發送給cpu interface。寄存器使用 GICD_ 作為前綴。一個gic中,只有一個GICD。 ? cpu interface:將

gic和ARM Core的連接

gic和ARM Core的連接

評論