引言:對于中壓或高壓的電源系統(tǒng),對MOS組的要求特別高,DrMOS已經(jīng)不能滿足設(shè)計參數(shù)要求,此時將DrMOS再次分拆開來,將驅(qū)動部分獨立成為柵極驅(qū)動器。柵極驅(qū)動器的強度和抗擾度極佳,非常適用于電機驅(qū)動、家用電器、SMPS、電池供電應(yīng)用和大功率照明。

1.結(jié)構(gòu)組成

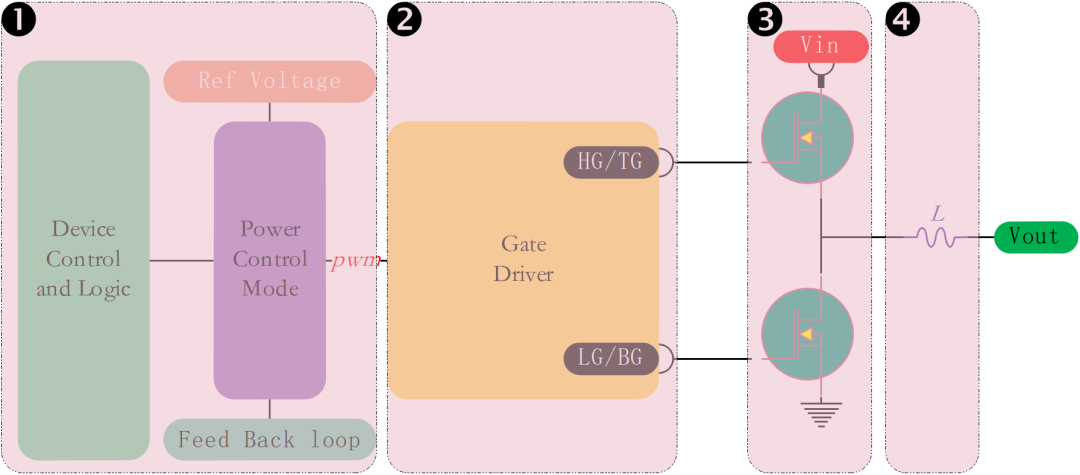

在SMPS中,如圖8-1所示,(Low Voltage Gate Drivers)低壓柵極驅(qū)動器 (半橋柵極驅(qū)動器)即是2部分。而在電機驅(qū)動中,兩個半橋柵極驅(qū)動器就可以組成一個H橋驅(qū)動器,控制電機的轉(zhuǎn)速和方向,在AC-DC/DC-AC中,還充當(dāng)整流器和逆變器,例如無線充電鏈路。每一個功率器件都需要一個驅(qū)動器(驅(qū)動芯片)

圖8-1:DC-DC結(jié)構(gòu)層級

圖8-1中是以PWM三態(tài)模式驅(qū)動,還有另外一種兩態(tài)模式驅(qū)動,本節(jié)先介紹PWM模式,下節(jié)介紹HL兩態(tài)模式。

2.PWM三態(tài)模式驅(qū)動

驅(qū)動結(jié)構(gòu)

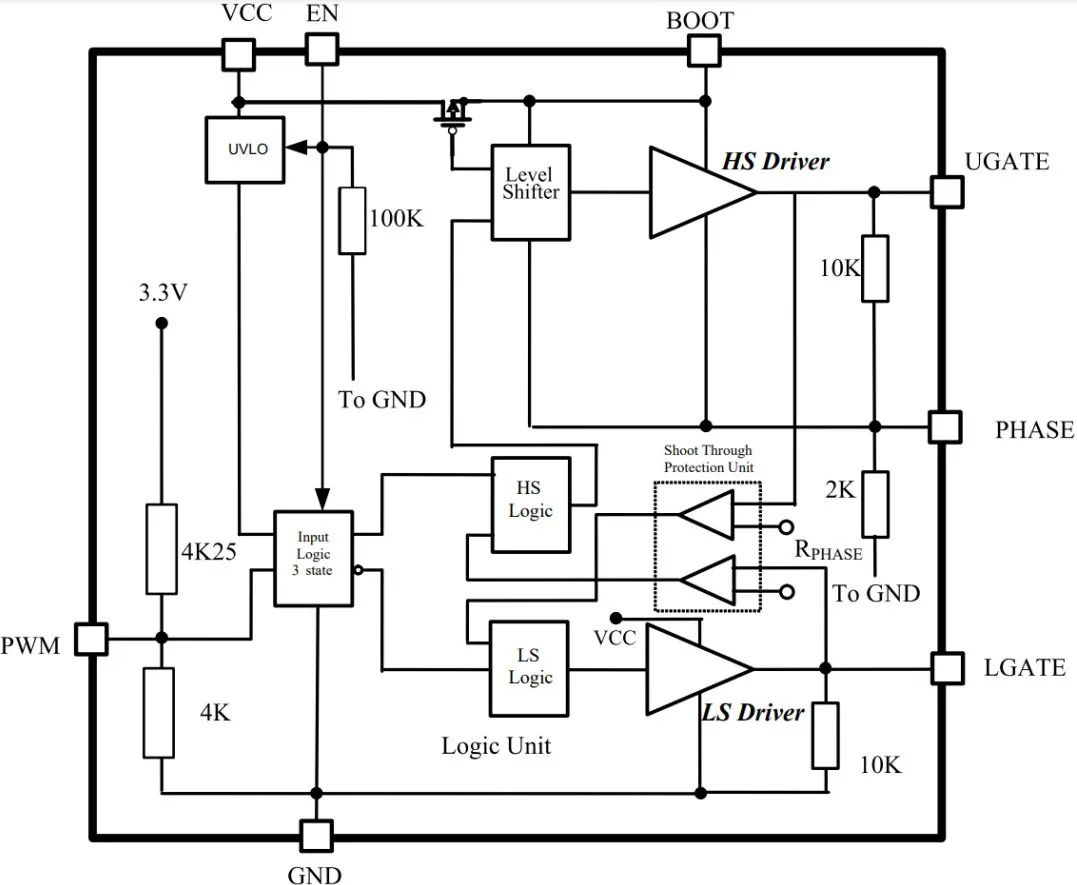

圖8-2是一個和數(shù)字電源控制器搭配使用的半橋柵極驅(qū)動器IC內(nèi)部結(jié)構(gòu)圖,其中VCC是獨立供電引腳,BOOT和PHASE用于自舉設(shè)置(BST),PWM來自于數(shù)字電源控制器的PWM輸入,輸入信號PWM參考SGND引腳,TG/BG(UG/LG)狀態(tài)由該引腳處的電壓決定。驅(qū)動器內(nèi)部實現(xiàn)了一個嵌入式電阻器網(wǎng)絡(luò),如果該引腳是浮動的,內(nèi)部電阻分壓器會觸發(fā)高Z模式,在該模式下BG和TG都關(guān)閉,Layout時該引腳上的寄生電容應(yīng)最小化。

圖8-2:典型的半橋驅(qū)動IC內(nèi)部結(jié)構(gòu)

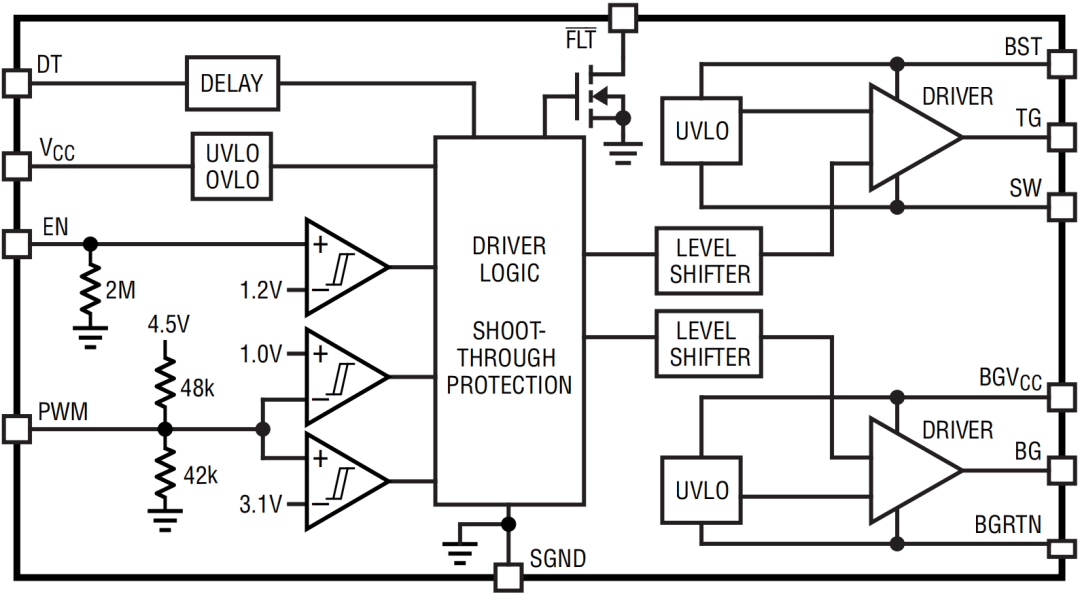

圖8-3:典型的半橋驅(qū)動IC內(nèi)部結(jié)構(gòu)-2

柵極驅(qū)動器接收以地為基準(zhǔn)的低電壓數(shù)字PWM信號,以驅(qū)動半橋配置中的兩個N溝道功率MOSFET。低側(cè)MOSFET的柵極被驅(qū)動為高或低,在BGVCC和BGRTN之間擺動,這取決于PWM引腳的狀態(tài)。類似地,高側(cè)MOSFET的柵極與低側(cè)MOSFET互補地被驅(qū)動,在BST和SW之間擺動。低側(cè)驅(qū)動器和高側(cè)驅(qū)動器都是浮柵驅(qū)動器,獨特的雙浮動結(jié)構(gòu)使柵極驅(qū)動器輸出穩(wěn)健,對地噪聲不太敏感,對稱設(shè)計允許半橋輸出是輸入邏輯的反相或非反相。

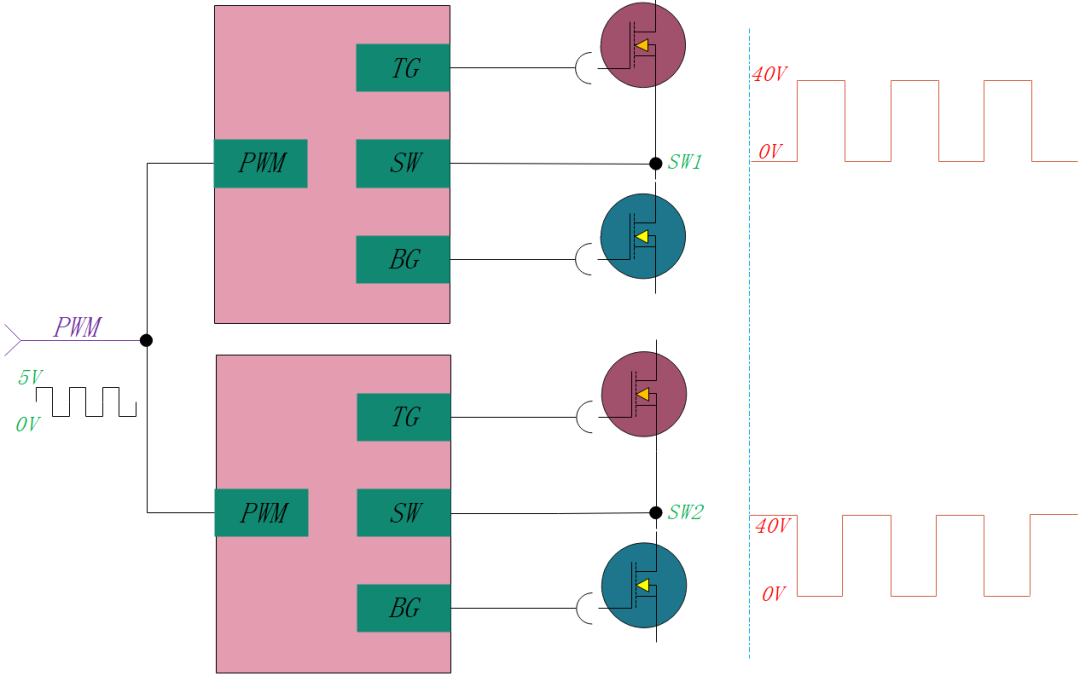

而同一個PWM波可以同時驅(qū)動多個驅(qū)動器,如圖8-4所示:

圖8-4:多驅(qū)動器模式

驅(qū)動邏輯

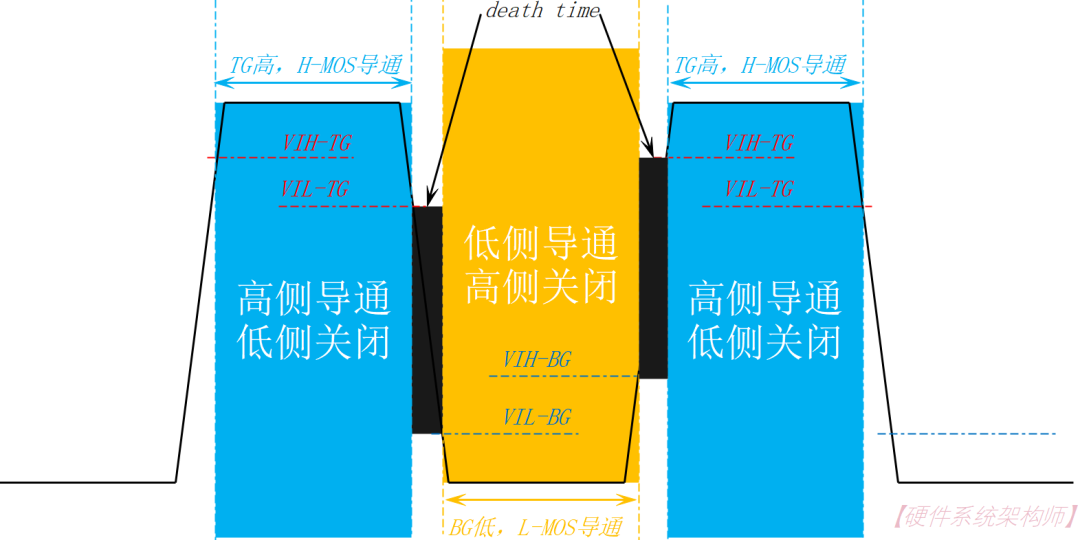

對于具有固定轉(zhuǎn)換閾值的三態(tài)PWM輸入,驅(qū)動器的轉(zhuǎn)換閾值和三種輸入狀態(tài)之間的關(guān)系如圖8-5所示。當(dāng)PWM上的電壓大于閾值VIH(TG)時,TG被上拉到BST,使高側(cè)MOSFET導(dǎo)通,該MOSFET將保持導(dǎo)通,直到PWM降至VIL(TG)以下。類似地,當(dāng)PWM小于VIH(BG)時,BG被上拉到BGVCC,使低側(cè)MOSFET導(dǎo)通,BG將保持高電平,直到PWM增加到閾值VIL(BG)以上。

圖8-5:三態(tài)及其轉(zhuǎn)換閾值

驅(qū)動器還能夠?qū)蓚€外部MOSFET驅(qū)動到斷開狀態(tài),當(dāng)PWM信號電平進(jìn)入關(guān)閉窗口或三態(tài)(通常在1.2V和2V之間)時,在關(guān)閉保持時間到期后,兩個MOSFET都會關(guān)閉。當(dāng)控制器想要減少活動相(多相架構(gòu))的數(shù)量以降低功耗時,此功能非常有用。原則上,三態(tài)也可以用于在重負(fù)載和輕負(fù)載轉(zhuǎn)換期間提高性能。

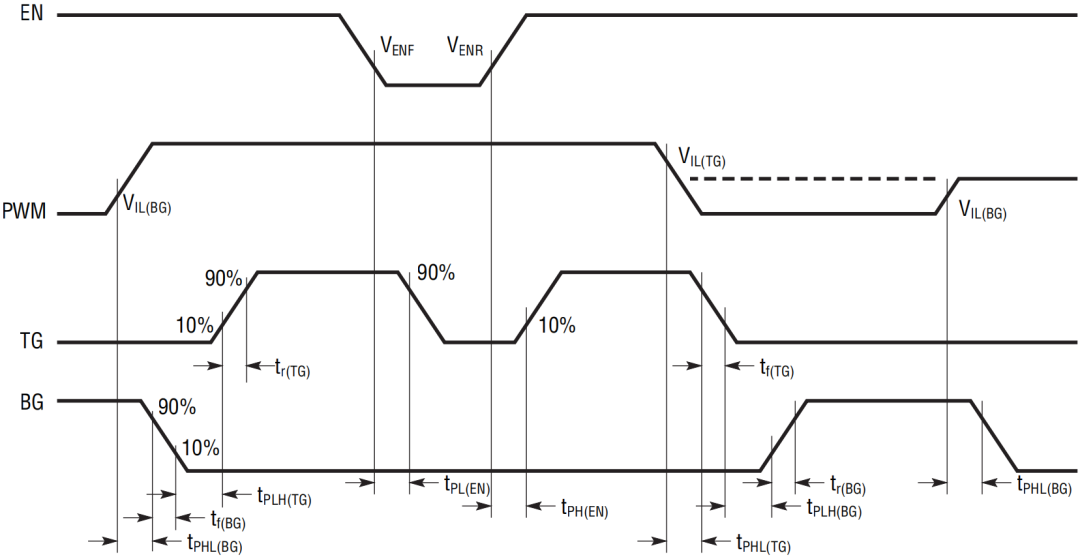

圖8-6是驅(qū)動器的時序圖,其中自適應(yīng)交叉導(dǎo)通保護(hù)基于MOSFET在關(guān)斷期間的柵極到源極電壓,當(dāng)PWM信號變低時,高側(cè)MOSFET將開始關(guān)斷,一旦高側(cè)MOSFET的VGS放電到1V以下,低側(cè)MOSFET就會開始導(dǎo)通。當(dāng)PWM信號變高時,低側(cè)MOSFET將開始關(guān)斷,一旦低側(cè)MOSFET的VGS在1V以下放電,高側(cè)MOSFET就會開始導(dǎo)通。為了避免高側(cè)MOSFET和低側(cè)MOSFET之間的交叉導(dǎo)通,驅(qū)動器內(nèi)部采用了自適應(yīng)反擊穿控制方案,這種自適應(yīng)方案允許將各種不同的功率MOSFET用于不同類型的功率轉(zhuǎn)換,但是為了最大限度地提高整體解決方案的效率,死區(qū)時間保持得盡可能短。

對應(yīng)的VIH和VIL電平之間的滯后消除了由于開關(guān)轉(zhuǎn)換期間的噪聲而引起的錯誤觸發(fā),但是應(yīng)注意防止噪聲耦合到PWM引腳,特別是在高頻、高電壓應(yīng)用中。

圖8-6:三態(tài)柵極驅(qū)動器時序圖

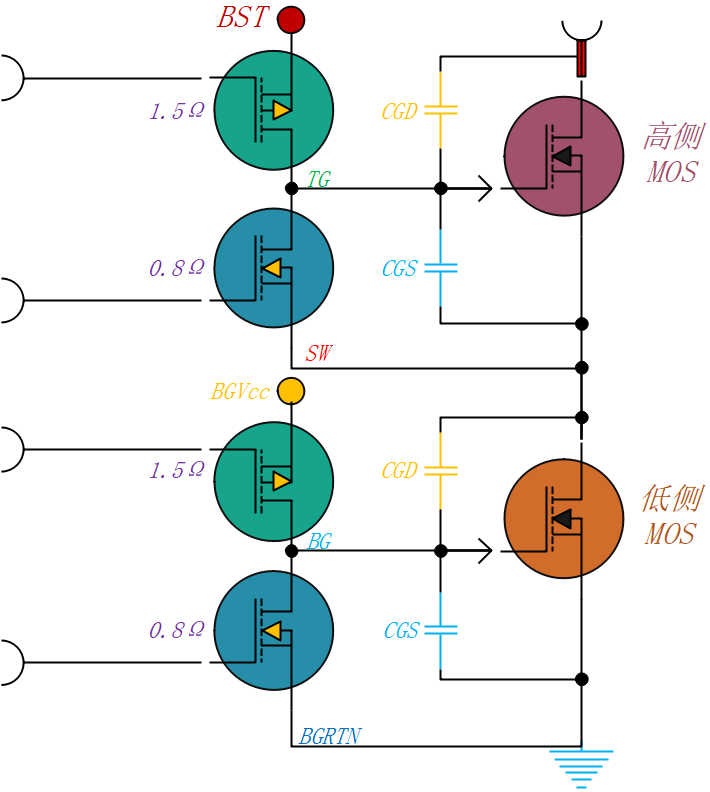

驅(qū)動能力

由于功率MOSFET通常占轉(zhuǎn)換器中功率損耗的大部分,因此具備快速導(dǎo)通和關(guān)斷特性的功率MOSFET非常重要,從而最大限度地減少轉(zhuǎn)換時間和功率損耗。如圖8-7所示,驅(qū)動器的典型1.5Ω上拉電阻和0.8Ω下拉電阻相當(dāng)于10V驅(qū)動器電源下的3A峰值上拉電流和6A峰值下拉電流。BG和TG都可以驅(qū)動MOSFET的快速導(dǎo)通轉(zhuǎn)變,具有以18ns上升時間驅(qū)動3.3nF負(fù)載的能力,所以一定要關(guān)注所選MOS的寄生電容和Layout電容。

圖8-7:半橋配置中的簡化輸出級

3.工作過程 *

當(dāng)VCC引腳電壓超過VCC上升電壓閾值(VUVLO_R)時,驅(qū)動器開始根據(jù)PWM狀態(tài)進(jìn)行操作。在VCC引腳電壓達(dá)到VCC上升閾值之前,兩個MOSFET都保持在斷開狀態(tài)。對于VCC,建議其上升沿的斜率高于上升UVLO閾值附近的5V/100ms。當(dāng)PWM信號執(zhí)行從低狀態(tài)到高狀態(tài)的轉(zhuǎn)換(PWM電壓高于2.5V典型值)時,在關(guān)斷傳播延遲時間之后,低側(cè)MOSFET關(guān)斷,接下來在導(dǎo)通傳播延遲時間之后,高側(cè)MOSFET導(dǎo)通。一旦接通時間到期,PWM信號從高狀態(tài)轉(zhuǎn)換到到低狀態(tài)(PWM電壓低于0.8V典型值),這將在關(guān)斷傳播延遲時間之后將高側(cè)MOSFET從導(dǎo)通狀態(tài)驅(qū)動到截止?fàn)顟B(tài)。

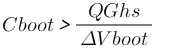

4.自舉電容

高側(cè)MOSFET通過自舉電路供電,有的內(nèi)部帶自舉電源,有的驅(qū)動器嵌入自舉二極管,因此要完成Boot網(wǎng)絡(luò),只需要在PHASE引腳和BOOT引腳之間添加電容。在許多情況下,驅(qū)動器經(jīng)過優(yōu)化已具備最佳的開關(guān)動作,因此不需要外部電阻(串聯(lián)柵極驅(qū)動電阻)。根據(jù)高側(cè)MOSFET柵極電荷來選擇自舉電容,以下公式給出了由于高側(cè)MOSFET的充電而引起的自舉電容兩端的電壓降的準(zhǔn)確估算:

ΔVBoot是自舉電壓的浮動值,這通常應(yīng)盡可能低,以避免高側(cè)MOSFET的Rdson下降,一般0.1V和0.01V之間的值是可以接受的。

低側(cè)MOSFET驅(qū)動器通過VCC引腳供電,自舉電容的相同考慮因素和公式可以應(yīng)用于對VCC引腳進(jìn)行濾波的電容。部分驅(qū)動器還支持將驅(qū)動電壓從4.5V調(diào)整到8V,這樣的靈活性使設(shè)計者能夠以任何所需的方式塑造效率曲線。

5.注意點

驅(qū)動器輸出上的強下拉防止了交叉?zhèn)鲗?dǎo)電流,例如在圖8-7所示的半橋配置中,當(dāng)BG關(guān)閉低側(cè)功率MOSFET,TG打開高側(cè)功率MOSFET時,SW引腳上的電壓可能會非常迅速地上升到VIN,該高頻正瞬態(tài)電壓將通過低側(cè)功率MOSFET的CGD電容耦合到BG引腳。如果BG引腳沒有被充分壓低,BG引腳上的電壓可能會上升到低側(cè)功率MOSFET的閾值電壓以上,從而瞬間使其重新導(dǎo)通,因此高側(cè)和低側(cè)MOSFET都將導(dǎo)通,這將導(dǎo)致大量的交叉導(dǎo)通電流通過MOSFET從VIN流到地,從而造成相當(dāng)大的功率損失并且可能損壞MOSFET,因此建議BG和TG引腳的PCB走線盡可能短粗,以最大限度地減少寄生電感。

-

PWM

+關(guān)注

關(guān)注

116文章

5511瀏覽量

219380 -

smps

+關(guān)注

關(guān)注

6文章

131瀏覽量

55185 -

驅(qū)動芯片

+關(guān)注

關(guān)注

13文章

1411瀏覽量

56411 -

DC-AC

+關(guān)注

關(guān)注

3文章

28瀏覽量

18221 -

柵極驅(qū)動器

+關(guān)注

關(guān)注

8文章

1085瀏覽量

39681

發(fā)布評論請先 登錄

為什么需要柵極驅(qū)動器?柵極驅(qū)動器及其應(yīng)用介紹

單片機應(yīng)用系統(tǒng)的結(jié)構(gòu)與工作過程

隔離式柵極驅(qū)動器的揭秘

柵極驅(qū)動器是什么

柵極驅(qū)動器是什么,為何需要柵極驅(qū)動器?

了解您的柵極驅(qū)動器

柵極驅(qū)動器電流多少正常啊,柵極驅(qū)動器電流怎么計算

柵極驅(qū)動器芯片的原理是什么

無刷電機驅(qū)動器的工作原理和結(jié)構(gòu)組成

什么是柵極驅(qū)動器?柵極驅(qū)動器的工作原理

采用智能柵極驅(qū)動器的低壓電機驅(qū)動操作

柵極驅(qū)動器的定義和結(jié)構(gòu)

LM5101系列 高壓高壓側(cè)和低壓側(cè)柵極驅(qū)動器數(shù)據(jù)手冊

評論