關于FPGA的功耗優化,筆者曾經在一個項目上做過深入的比對實踐。近期在Xilinx官網搜到這篇文章,有種醍醐灌頂、相見恨晚的感覺。這篇文章的原創應該是來自科通的FAE技術分享集,值得大家好好研讀一番。

AMD -Xilinx FPGA功耗優化設計簡介

重要的事情說三遍,文章里面說一遍,筆者接下來將會結合自身的設計經驗和體會再說一遍,讀后也請大家默默回味一遍。若能牢記在心,相信這些要點將來一定能夠成為指導大家設計的一些基本原則。

● 仔細檢查一下設計中的PLL,是不是可以把兩個PLL整合為一個;或者是否可以對時鐘頻率做一些“整合”,盡量減少時鐘頻率數量,從而省去一個PLL。如果可以,恭喜你,你將收獲的是幾十mW的功耗降低,這個數值很可能是整個功耗優化項目中的top1。

● 盡可能降低FPGA資源的使用,這句話只能在優化功耗的時候說,因為從整個設計角度看,“速度”和“資源”有時是蹺蹺板的兩端,必須在它們之間做出權衡。或者換句話說,在滿足“速度”性能要求的情況下,盡可能減少“資源”的消耗。一種看似行之有效的方法,就是在產品應用允許的情況下,讓FPGA器件的加載者在多個不同的比特流之間切換,這樣就能做到在單獨運行某個功能時,其它功能不會白白消耗任何的靜態功耗。這也可能會帶來一點麻煩,需要設計者為一個設計維護多個工程,并且最重要的是,產品應用以及存在一個合適的FPGA加載者支持這么干。

● 接著上面的點,如果要在片內存儲器和邏輯資源之間做選擇,盡量減少片內存儲器的使用,原因很簡單,片內存儲器相比邏輯資源更耗電。

● 使用門控時鐘或片選信號(存儲器的CE信號),在非運行時間關閉時鐘或邏輯(存儲器),從而降低不必要的動態功耗。

FPGA內部的功耗優化,其實就如同水龍頭,要么減少開啟時間,要么盡可能調小流量。很多時候很難像去掉一個PLL那樣有立竿見影的效果,大多數的優化嘗試可能收獲的都是杯水車薪,但是積少成多,一點一滴也可能省出一個可觀的百分比。有很多細節的優化,也并不是筆者可以一一娓娓道來的,只有工程師結合自身具體的工程應用,耐心細致的進行不斷嘗試和比對測試,才可以做到設計功耗的最優化。

-

amd

+關注

關注

25文章

5476瀏覽量

134289 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26552 -

存儲器

+關注

關注

38文章

7514瀏覽量

163994

原文標題:FPGA設計功耗優化

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

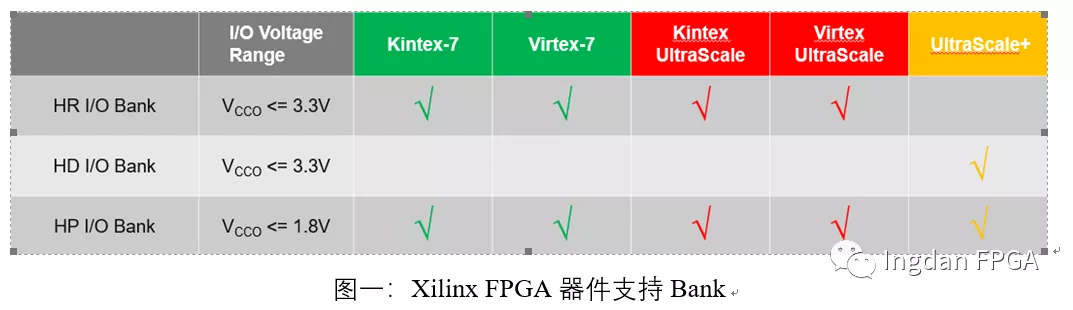

Xilinx系列FPGA SelectIO簡介

AMD Xilinx 7系列FPGA的Multiboot多bit配置

為什么要優化FPGA功耗?

使用ISE設計工具優化FPGA的功耗方案

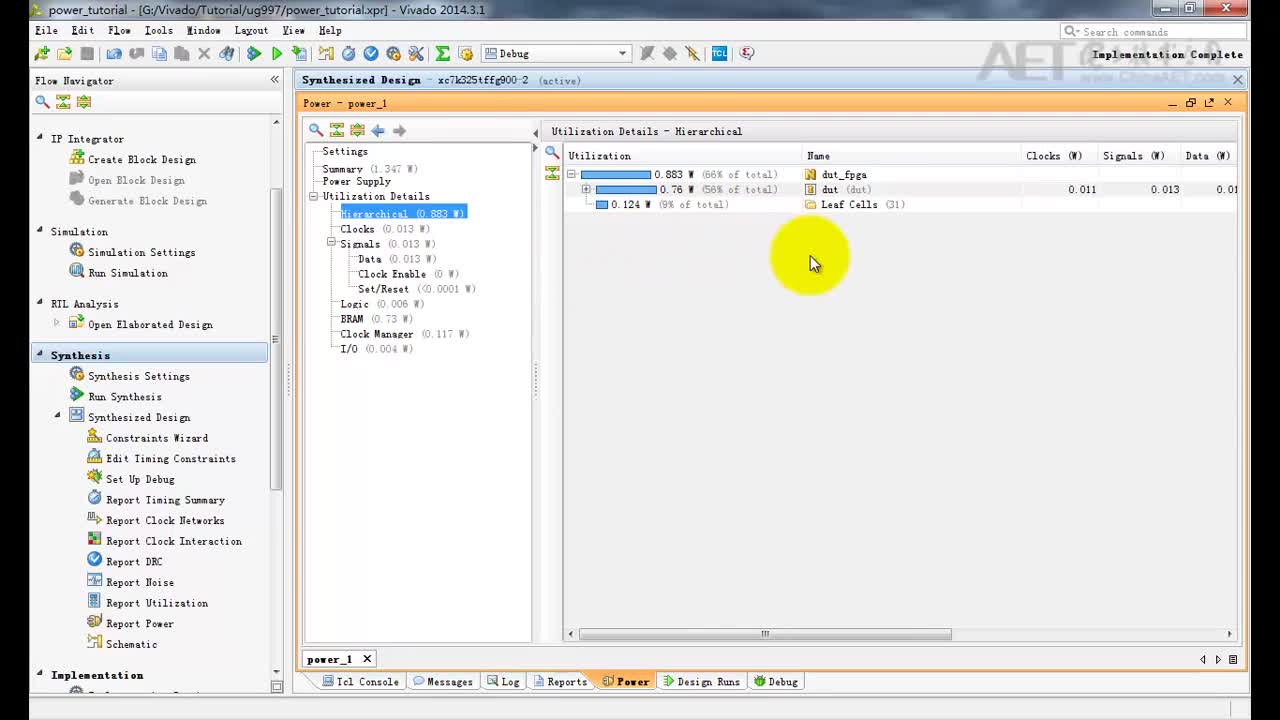

Xilinx升級Vivado 2014.3的FPGA功率優化

基于FPGA的Vivado功耗估計和優化

實現低功耗FPGA電子系統優化技巧與方法

AMD收購FPGA領域的市場領導者Xilinx

AMD-Xilinx FPGA功耗優化設計簡介

XILINX FPGA簡介-型號系列分類參考

AMD -Xilinx FPGA功耗優化設計簡介

AMD -Xilinx FPGA功耗優化設計簡介

評論