使用 MATLAB HDL Coder 和 FPGA 快速實現自動白平衡(AWB)

在此項目中,我們將使用 MATLAB Simulink 和 HDL 編碼器創建自定義 IP -- AWB。

MATLAB 設計

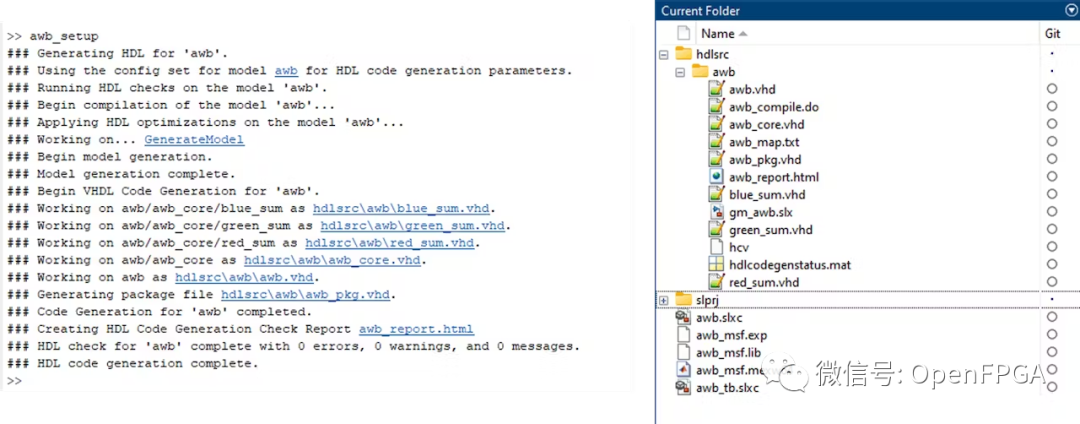

自動白平衡模塊的設計是使用 HDL Coder 在 MATLAB 和 Simulink 中創建的。HDL Coder能夠生成 HDL 文件,這些文件可以作為 IP 在我們的目標 FPGA 中運行。

AWB IP 設計旨在對每個時鐘 2 個像素求和,這些像素是從 Vivado 設計中的demosaic 輸出的 RGB 像素。

該算法非常簡單,對每個幀的 RGB 通道進行求和并提供給微處理器。在微處理器中,像素的總和被劃分創建校正白平衡所需的校正因子。

除法是在 MicroBlaze 中完成的,雖然必須快速收集每幀的統計數據,但除法不必那么快,因此為了節省邏輯資源,利用 Microblaze即可完成。

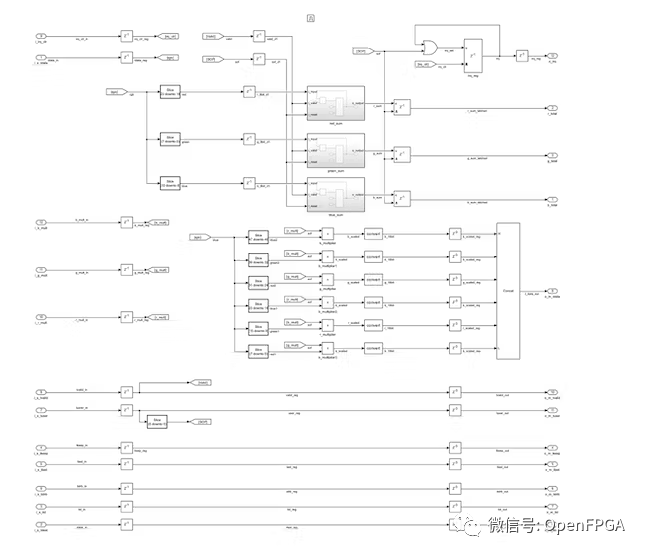

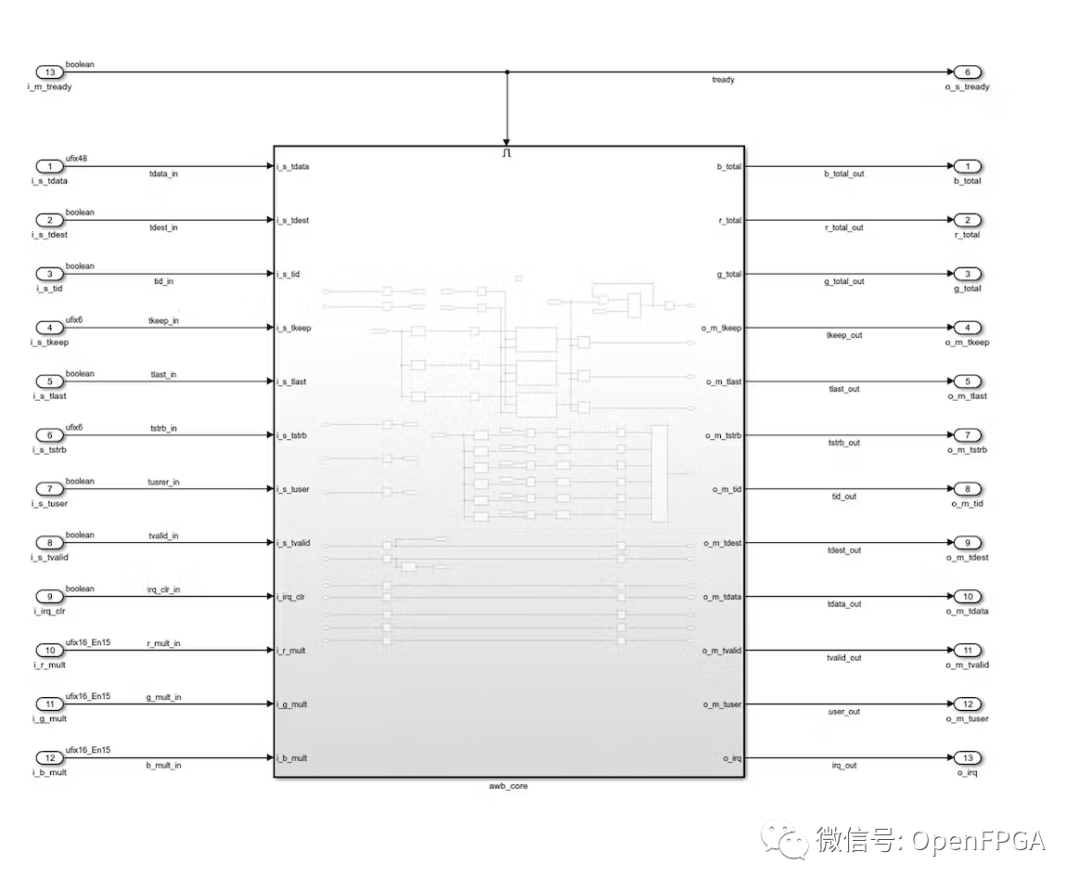

整體設計如下

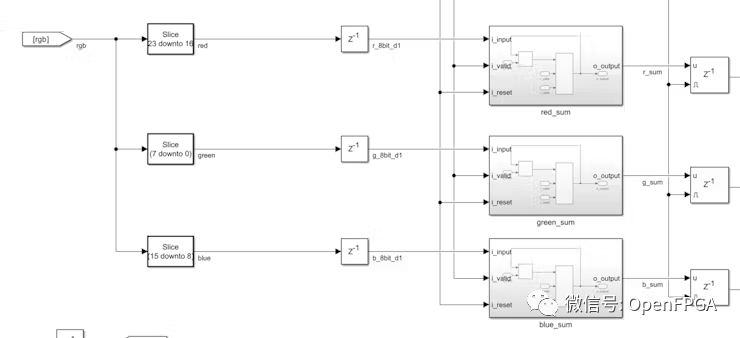

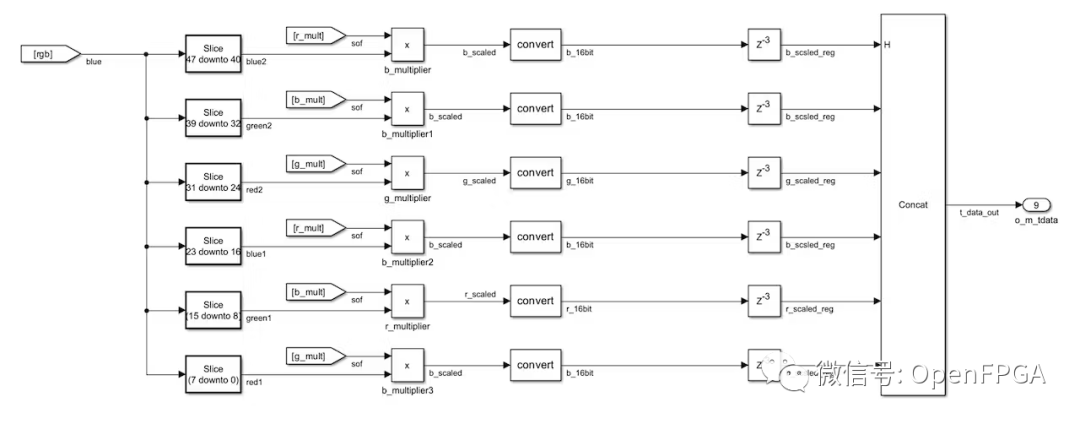

像素求和旨在捕獲將傳入的 AXI 流像素數據分割為三個元素 R、G、B,然后在求和之前對這些像素中的每一個進行緩沖。求和塊的輸出也被記錄。

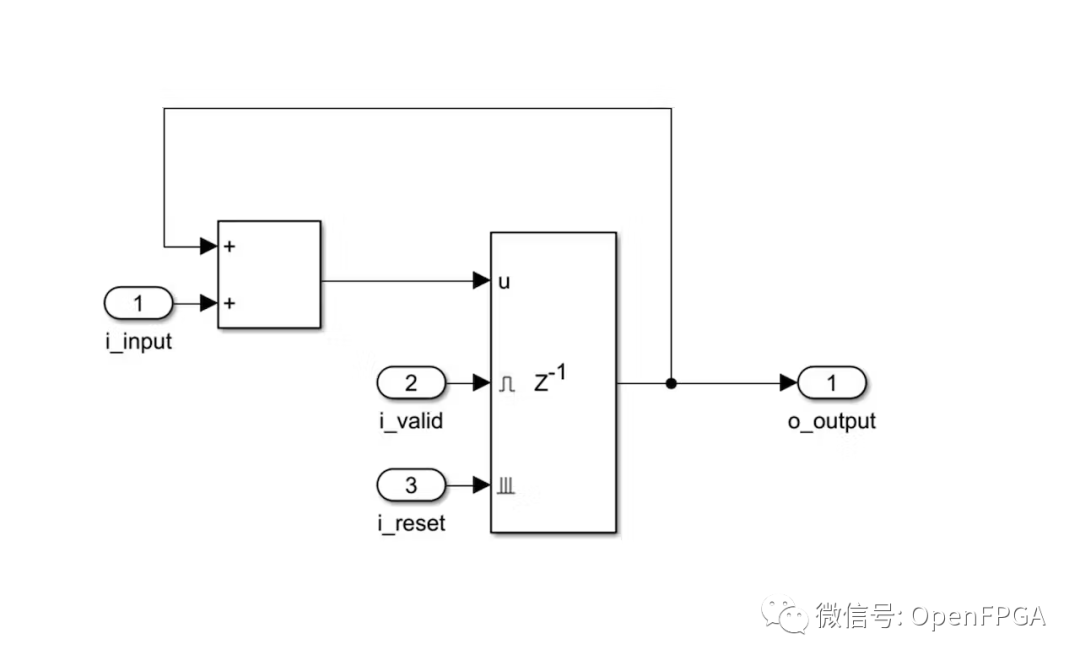

求和塊本身非常簡單。獲取輸入、有效和復位信號。復位信號連接到來自 AXI Stream 接口的 SOF 信號。而 AXI Valid 信號使能寄存器和累加。

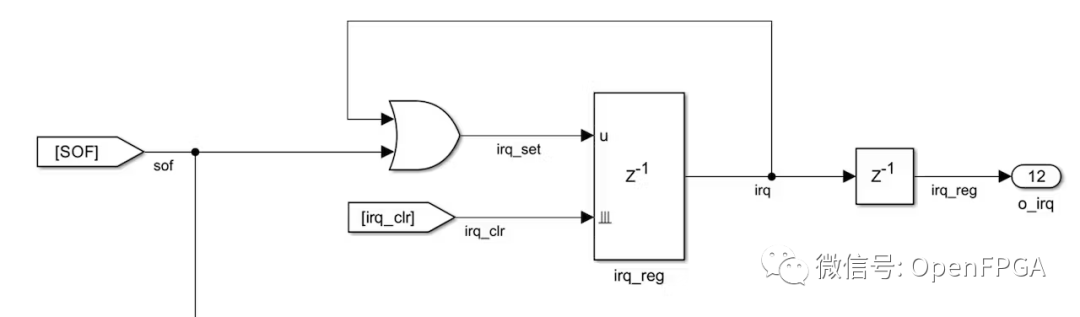

為了在每一幀結束時向微處理器生成 IRQ,我們使用了以下結構

一旦 MicroBlaze 定義了系數數據,需要將其應用于后面幀像素。

然后將它們連接起來,為 AXI-stream提供最終的像素數據。

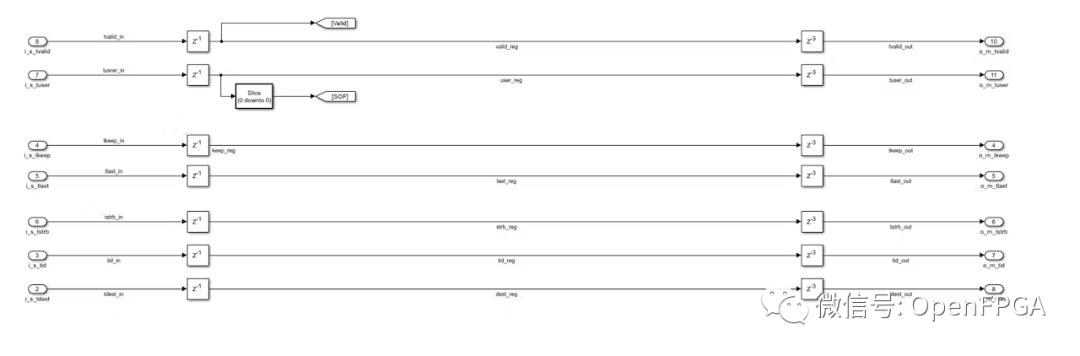

當然,也需要針對 AWB 算法中插入延遲進行平衡

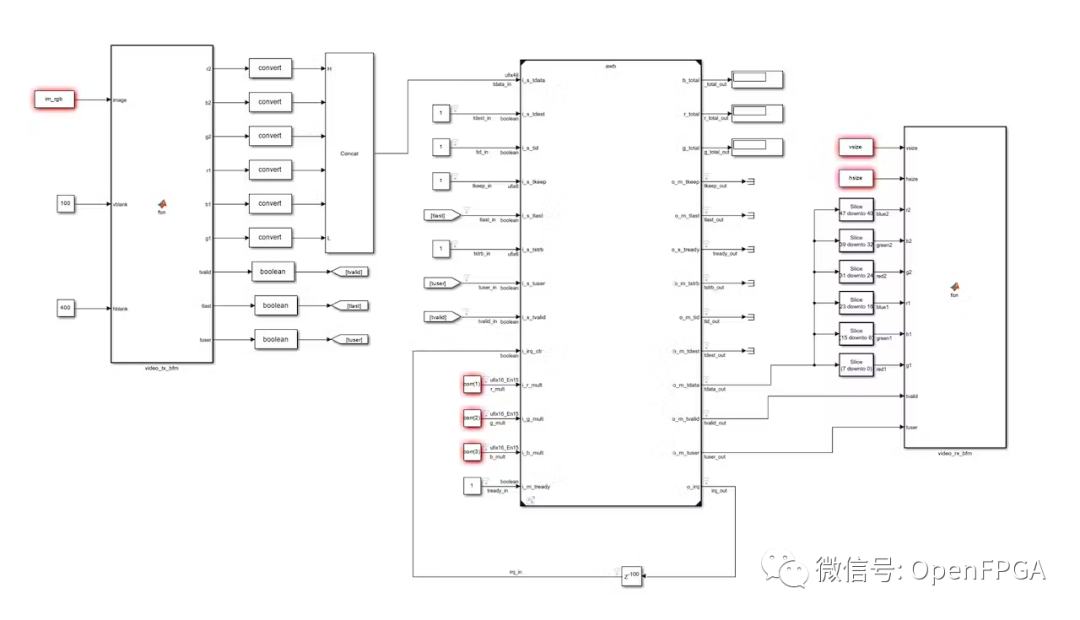

完整的模塊設計如下:

MATLAB 測試

為了測試這個設計,我們將在 MATLAB 中創建了一個測試平臺,它提取圖像文件來提供算法

自定義 MATLAB 模塊用于輸入和接收圖像,設置的 M 代碼如下所示:

closeall

[im,im_map]=imread("awb_test_img.jpg");

im_rgb=ind2rgb(im,im_map);

im_rgb=uint8(im_rgb*2^8);

imshow(im_rgb);

vsize=size(im_rgb,1);

hsize=size(im_rgb,2);

div_val=16;

fori=13

means(i)=mean(mean(im_rgb(:,:,i)/div_val));

end

max_mean=max(means);

im_corr=im_rgb;

fori=13

corr(i)=max_mean/means(i);

im_corr(:,:,i)=im_rgb(:,:,i)*corr(i);

end

figure()

imshow(im_corr)

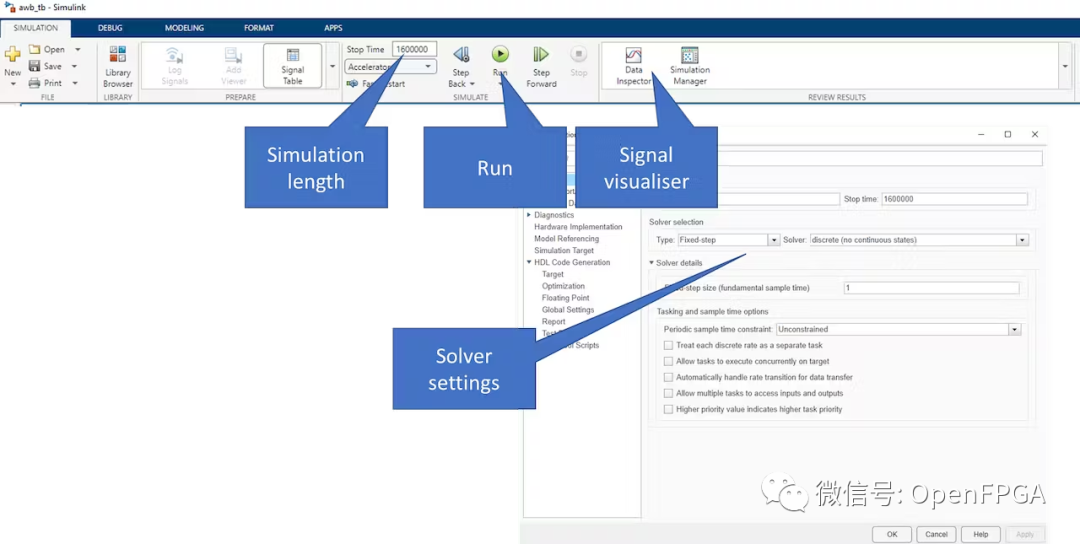

要運行模擬,我們首先需要做一些事情

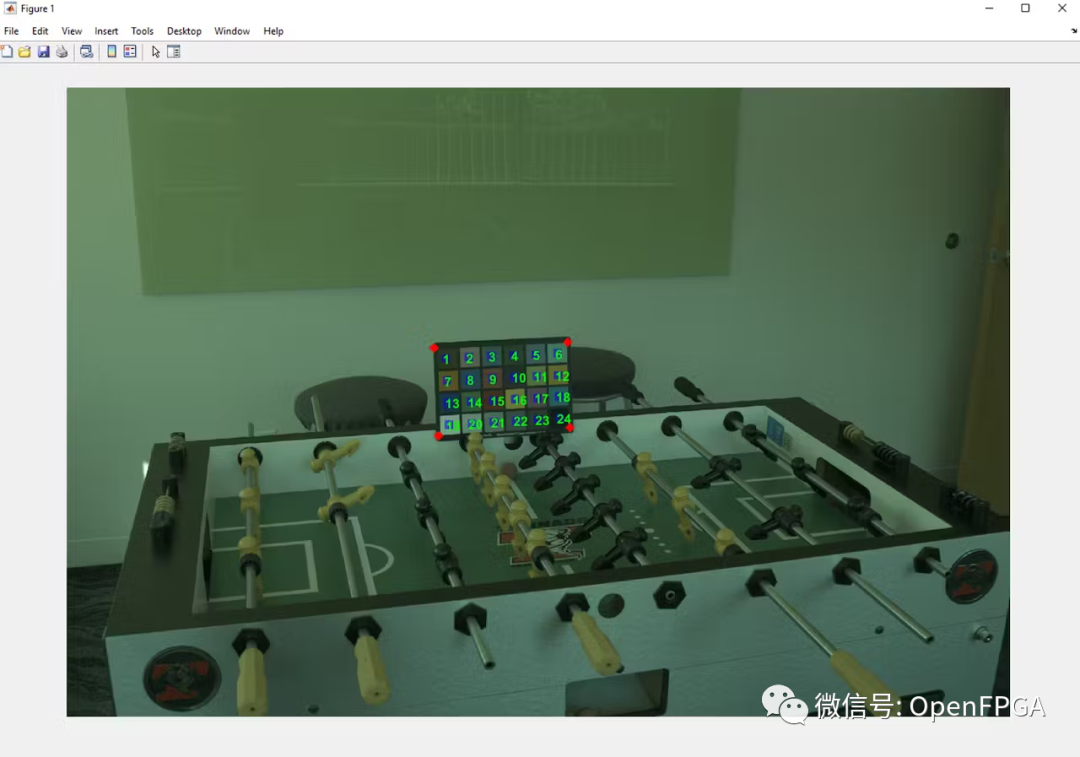

模擬輸入

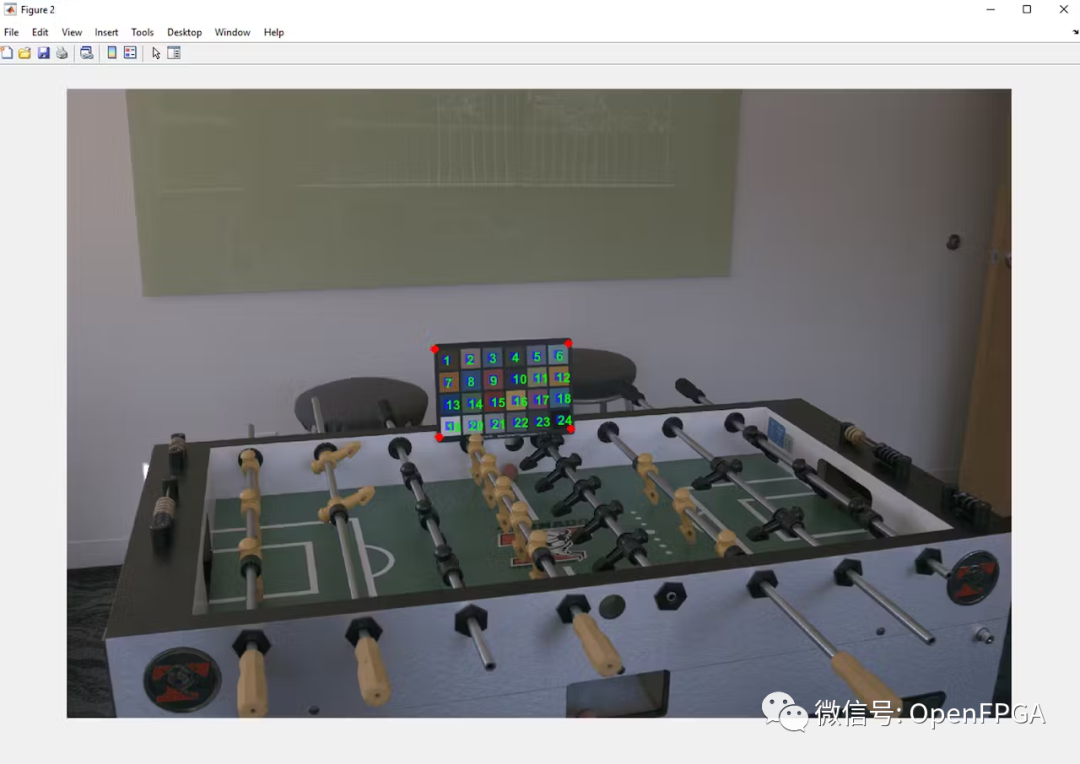

浮點結果

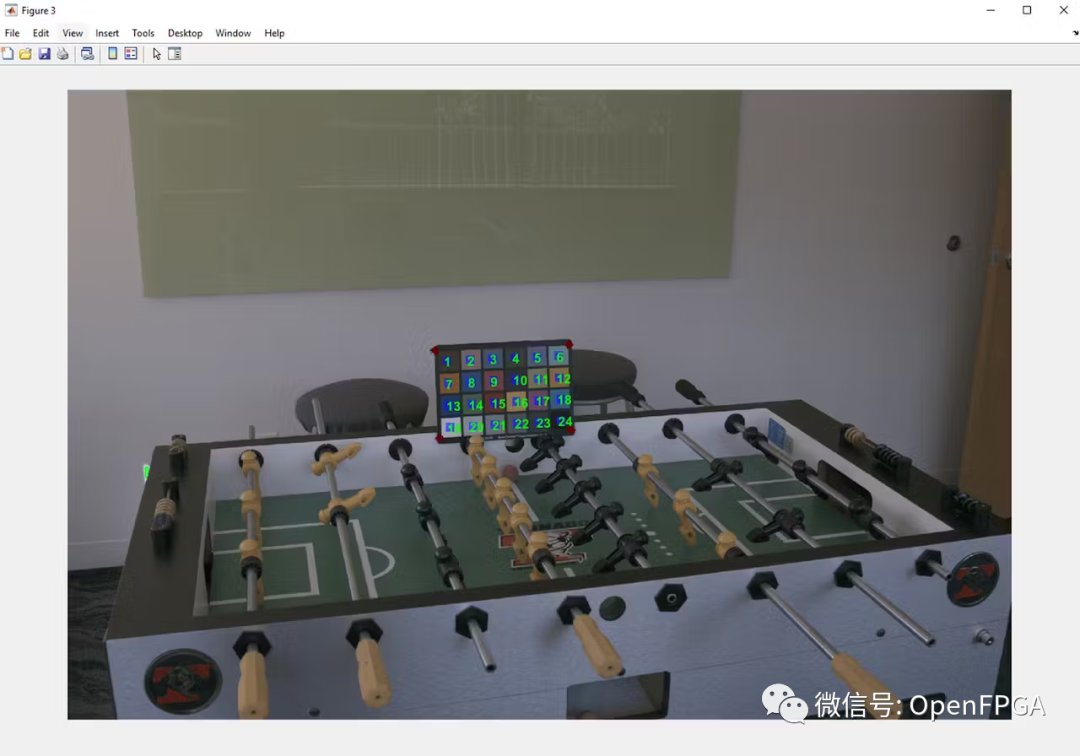

定點結果

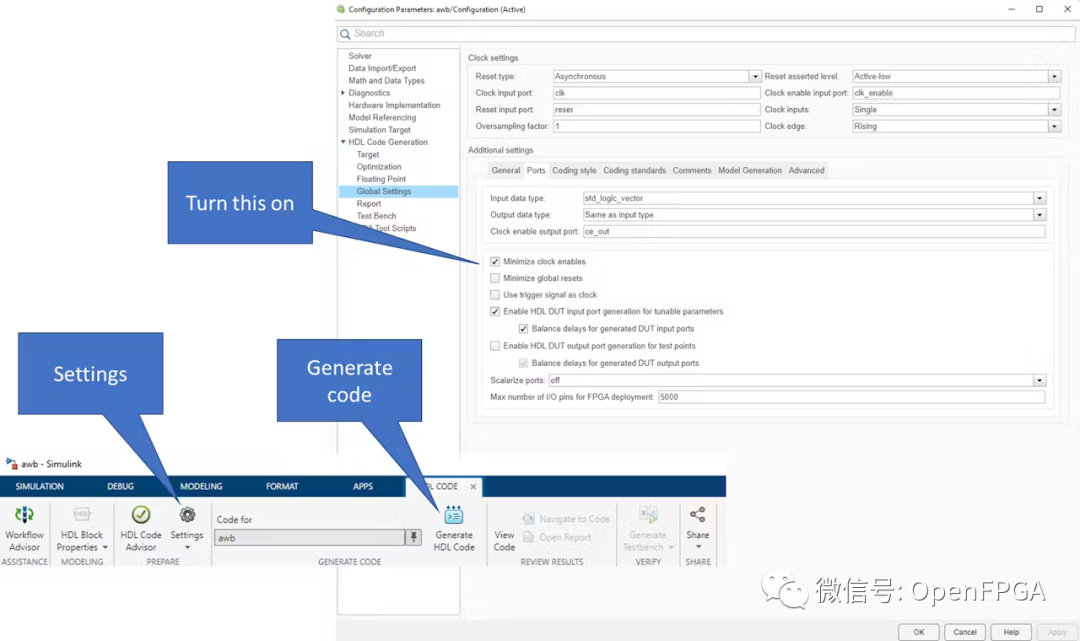

為了生成定點 HDL 解決方案,我們需要設置 HDL Coder生成器

Vivado 驗證

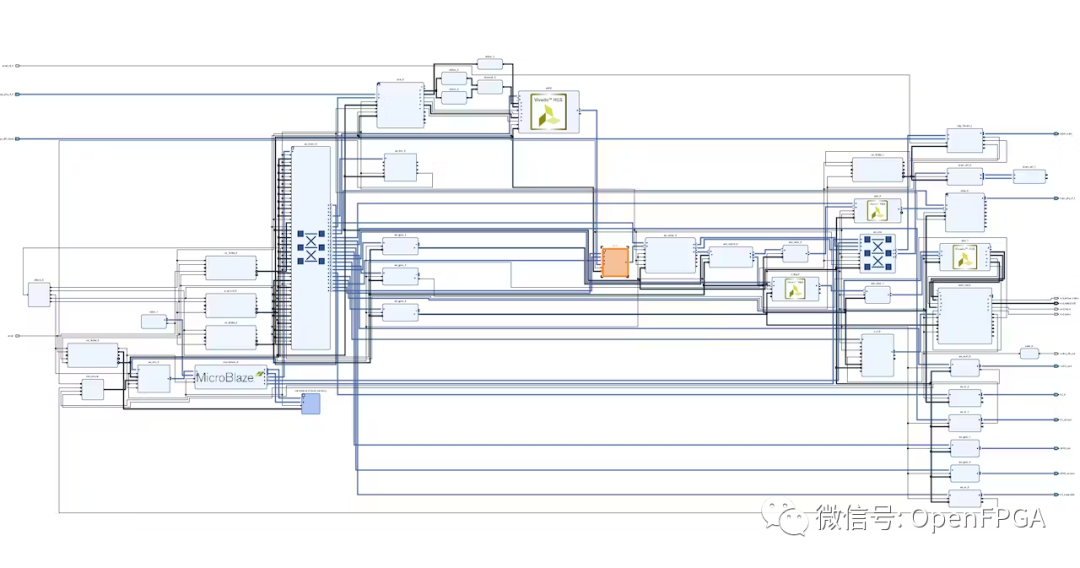

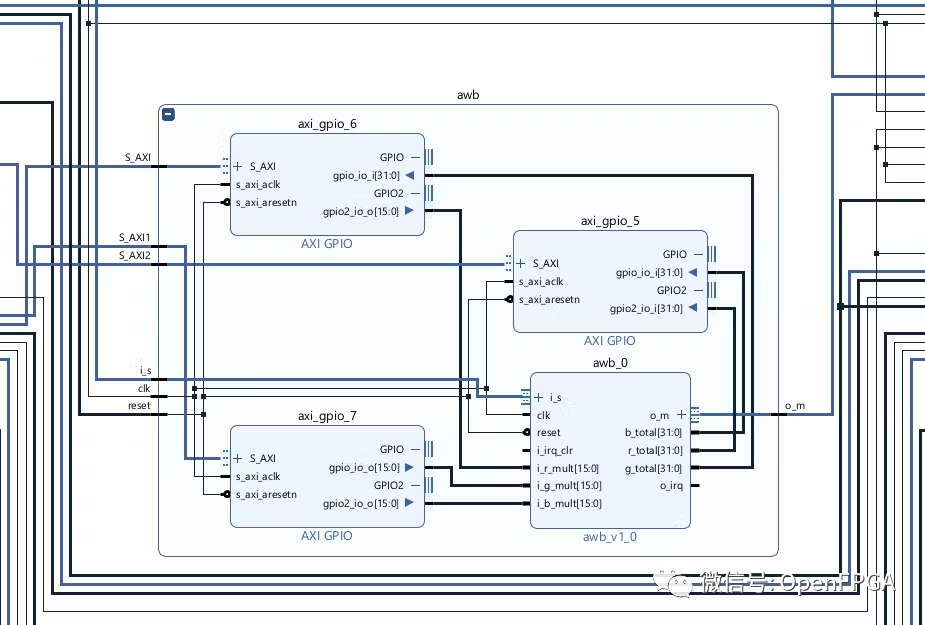

導出IP核后,我們可以將其導入Vivado IP庫并將其添加到演示項目中。

為了簡化寄存器接口,我們使用 AXI GPIO 提供所需的系數。

可以看到 AWB 提供 AXI Stream 輸入和輸出。

插入 AWB 后,接下來將在 Vitis 中的設計。

Vitis設計

算法非常簡單

Status=XGpio_Initialize(&Gpio5,XPAR_AWB_AXI_GPIO_5_DEVICE_ID);

Status=XGpio_Initialize(&Gpio6,XPAR_AWB_AXI_GPIO_6_DEVICE_ID);

Status=XGpio_Initialize(&Gpio7,XPAR_AWB_AXI_GPIO_7_DEVICE_ID);

exp_scale=0.8;

while(1){

r=XGpio_DiscreteRead(&Gpio5,1);

g=XGpio_DiscreteRead(&Gpio5,2);

b=XGpio_DiscreteRead(&Gpio6,1);

if(r>=g&&r>=b){

r_corr=1.0*32768*exp_scale;

g_corr=((float)r/(float)g)*32768*exp_scale;

b_corr=((float)r/(float)b)*32768*exp_scale;

}

elseif(g>=r&&g>=b){

r_corr=((float)g/(float)r)*32768*exp_scale;

g_corr=1.0*32768*exp_scale;

b_corr=((float)g/(float)b)*32768*exp_scale;

}

elseif(b>=r&&b>=g){

r_corr=((float)b/(float)r)*32768*exp_scale;

g_corr=((float)b/(float)g)*32768*exp_scale;

b_corr=1.0*32768*exp_scale;

}

XGpio_DiscreteWrite(&Gpio6,2,(int)r_corr);

XGpio_DiscreteWrite(&Gpio7,1,(int)g_corr);

XGpio_DiscreteWrite(&Gpio7,2,(int)b_corr);

總結

MATLAB HDL Coder 和 FPGA聯合開發,可以快速進行算法設計。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603008 -

matlab

+關注

關注

185文章

2974瀏覽量

230385 -

編碼器

+關注

關注

45文章

3638瀏覽量

134427 -

Simulink

+關注

關注

22文章

533瀏覽量

62380

原文標題:使用 MATLAB HDL Coder 和 FPGA 快速實現自動白平衡(AWB)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PYNQ設計案例:基于HDL語言+Vivado的自定義IP核創建

使用USRP E310和MATLAB和Simulink進行原型設計和測試軟件定義的無線電

SIMULINK線的處理/SIMULINK自定義功能模塊

利用SDSoC創建自定義硬件

Vivado Design Suite用戶指南:創建和打包自定義IP

如何在Matlab中自定義Message

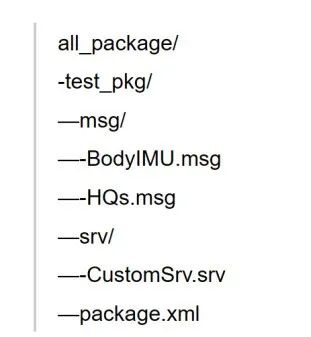

使用MATLAB Simulink和HDL編碼器創建自定義IP--AWB

使用MATLAB Simulink和HDL編碼器創建自定義IP--AWB

評論