一個電路板從設計到實現是經過什么步驟?

從頂層設計來講,首先是射頻方案的選擇。

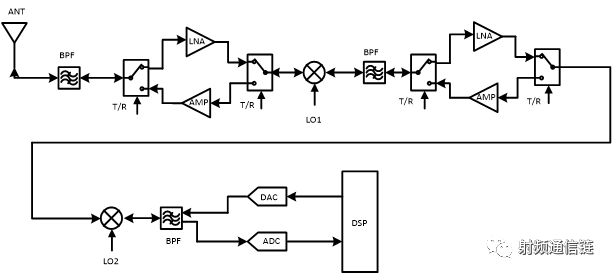

射頻框架

射頻方案設計來設計去,就那三種設計方案,超外差,零中頻,低中頻。

超外差

超外差方案實現了頻譜搬移,所以可以通過頻譜搬移、中頻濾波器把很多干擾頻率濾除,而且相對而言超外差方案如果不考慮對別人的發射影響,超外差方案只在接收的抗干擾上有優勢。

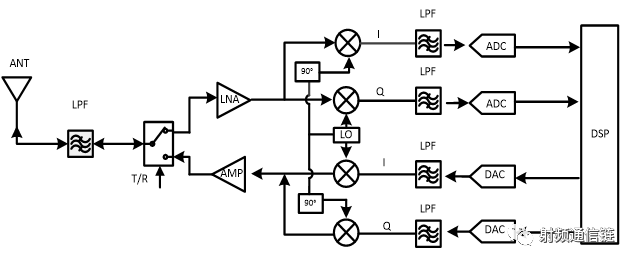

零中頻

零中頻架構,將射頻直接變成基帶信號。所以零中頻在尺寸、功耗上都很有優勢。這也是方案時選擇這個方案最重要的考慮。

因為零中頻是正交變換,所以硬件的不一致,會導致零中頻方案出現因為差分正交不平衡帶來的頻譜拓展。

低中頻方案,為了規避零中頻存在的問題,在ADC之前做了一次變頻處理。因為是在FPGA做處理,所以相對超外差方案比,尺寸和功耗有優勢。

方案選擇的原則就是側重什么就選擇相應的方案

側重射頻指標的一般用超外差,因為中頻濾波器的存在,可以比較容易的實現高指標。

側重尺寸和功耗的,一般選擇零中頻方案。

低中頻的方案主打的也是功耗和尺寸,對于一些實時更新的收發設計,零中頻設計在直流和偏差會存在差異,一般采用低中頻方案來規避。

落實到器件選擇

器件的選擇主要是鎖相環、放大器、混頻器和外圍電路。

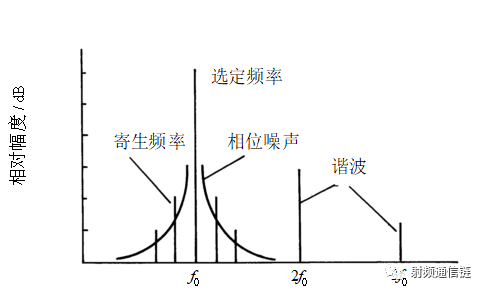

鎖相環

鎖相環的選型關系到發射和接收鏈路的關鍵指標,鎖相環也是雜散的關鍵來源之一。所以鎖相環的選擇至關重要。

在功耗設計允許的條件下,相位噪聲越高越好。

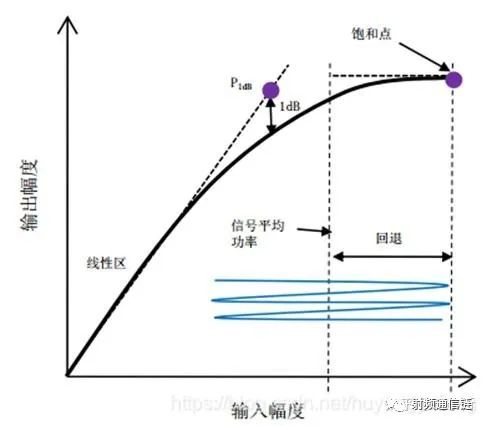

放大器

之前的文章我們講過,收發電路的設計就是設計整個收發系統的線性,整個收發電路中用的最多的也是放大器

LNA決定接收系統的NF和IIP3。

PA決定了發射系統的EVM。

放大器的選型原則是線性越高越好,效率越高越好。

混頻器

混頻器作為頻率變化的節點,它也是指標設計的關鍵節點。

很多人對指標的前后分配不知如何設計,

現有的混頻器的p-1基本上都在10左右,混頻器也是超外差方案相位噪聲的卡點處。

所以混頻器作為中間節點,就成為了指標分配的節點。

根據混頻器的p-1和頻率源的相位噪聲,就可以設計混頻前后的增益,動態范圍,濾波器,寬帶噪聲等指標的設計分配。

外圍電路

外圍電路包括檢波,ADC\DAC,運放,溫度檢測、電源等設計。

檢波器的選擇注意需要根據波形和切換時間選擇到底是峰值還是RMS檢波器。

外圍電路的選擇和設計主要是為了完成主要電路服務,在設計上按照需求選擇合適的電路。

這里主要說一下電源

上面說到鎖相環是雜散的關鍵來源之一。

還有一個雜散的關鍵來源就是電源,電路中因為P-1和器件的應用問題,所需要的電壓也不同,為了提升整個設計的效率,通常會使用DC-DC。

而在DCDC的使用過程中,就可能會出現開關頻率和cross頻率,這兩種頻率會調制到鎖相環和放大器上,形成雜散輸出。

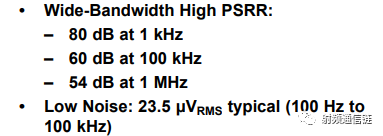

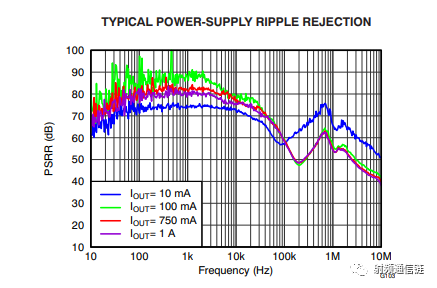

所以在DC設計時,需要注意DC的PSRR。一般來說雜散要求60dB,PSRR的要求就需要高于雜散的設計要求。

仿真、原理圖設計

關鍵器件選擇完畢,就需要設計原理圖了,原理圖的設計原則是能用簡單設計就用簡單設計,能用熟悉器件就用熟悉的器件。

仿真就不用說了,都是射頻工程師的拿手好戲。

PCB的設計原則是敏感器件離電源越遠越好,注意關鍵走線的阻抗和隔離。另外要強調一點,很多設計都說要數字地和模擬地隔離,對于射頻PCB布局來說,最好一塊地,隔離地可能會出現不想要的東西。

調試查問題

調試不怕出現問題,最怕的是出現問題卻分析不出問題。

出現問題具體分析,最多的問題就是匹配,隔離等。

問題一般來說都沒有想象的復雜,找到了之后可能就是一個走線,一個電感,甚至一個過孔。

結語

工程問題是基于可靠的理論實踐,不會出現無法解釋的問題。追本溯源,往往會射頻設計并不難。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603016 -

相位噪聲

+關注

關注

2文章

180瀏覽量

22860 -

射頻設計

+關注

關注

0文章

50瀏覽量

8618 -

零中頻

+關注

關注

0文章

64瀏覽量

9121 -

中頻濾波器

+關注

關注

1文章

6瀏覽量

5759

原文標題:射頻基礎——射頻設計的實施步驟

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一個電路板從射頻設計到實現是經過什么步驟?

一個電路板從射頻設計到實現是經過什么步驟?

評論