省流:不同的公司風(fēng)格不同,都會使用。

數(shù)字電路設(shè)計主要就是,選擇器、全加器、比較器,乘法器,幾個常用邏輯門,再加個D觸發(fā)器,電路基本都能實現(xiàn)了。

切換到具體語法System Verilog本來就是Verilog的語法擴(kuò)展,所以Verilog支持的SV都支持。

組合邏輯用assign是同樣的,用always_comb代替always @*。

時序邏輯用always_ff @(posedge clk or negedge rst_n)代替always @(posedge clk or negedge rst_n)

信號聲明logic代替wire/reg。不用再繁瑣的區(qū)分?jǐn)?shù)據(jù)類型。

端口聲明可以用多維數(shù)組。一些處理用generate for不要太爽。

以上這幾條改變不大,可以無縫適應(yīng)。

接口Interface

SystemVerilog提供了一個新的、高層抽象的模塊連接,這個連接被稱為接口(Interface)。它可以將常用的比較規(guī)范的端口定義出來,方便集成連接。

舉個例子,首先定義一組interface,文件為interface.vh

interface chip_bus (input logic clock, resetn); logic interrupt_req, grant, ready; logic [31:0] address; wire [63:0] data; modport master (input interrupt_req, input address, output grant, ready, inout data, input clock, resetn); modport slave (output interrupt_req, output address, input grant, ready, inout data, input clock, resetn); endinterface然后在子模塊中就可以include使用這一組定義。

`include "interface.vh" module primary( chip_bus.mater local_bus, chip_bus.slave primary_local_bus, input clock, input resetn ); endmodule `include "interface.vh" module secondary( chip_bus.slave local_bus, chip_bus.master secondary_local_bus, `ifdef FPGA input fpga_clk, `endif input clock, input resetn ); endmodule

最后在top中例化兩個子模塊,top上也可以定義interface,直接連接到子模塊,兩個子模塊之間的interface連接在頂層定義一個用于連線的interface。

`include "interface.vh"

module top (

chip_bus.master secondary_local_bus,

chip_bus.slave primary_local_bus,

`ifdef FPGA

input fpga_clk,

`endif

input clock,

input resetn

);

chip_bus local_bus();

primary u_primary(/*autoinst*/

.local_bus (local_bus.master ), //interface//ahb_bus.mater

.primary_local_bus (primary_local_bus ), //interface//axi_bus.slave

.clock (clock ), //input

.resetn (resetn ) //input

);

secondary u_secondary(/*autoinst*/

.local_bus (local_bus.slave ), //interface//ahb_bus.slave

.secondary_local_bus (secondary_local_bus ), //interface//axi_bus.master

`ifdef FPGA

.fpga_clk (fpga_clk ), //input

`endif

.clock (clock ), //input

.resetn (resetn ) //input

);

endmodule

使用interface可以提高集成的效率,不容易出錯,方便檢視。 當(dāng)然要是問我推薦用SV還是Verilog,我建議是遵守公司代碼規(guī)范,公司讓用啥就用啥。

審核編輯:劉清

-

比較器

+關(guān)注

關(guān)注

14文章

1655瀏覽量

107289 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110154 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

47957 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1608瀏覽量

80684

原文標(biāo)題:現(xiàn)在公司里做設(shè)計用SV還是Verilog?

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA編程是用VHDL還是verilog HDL好用?謝謝了!

我是學(xué)Verilog呢還是VHDL?

做硬件研發(fā)工作還是轉(zhuǎn)行去寫verilog代碼的工作

請問在Verilog里可以直接用'/'來做除法嗎?如果不能要怎樣做除法呀??

ISSI公司的sram verilog model使用

Quartus II 現(xiàn)在用verilog還是block dragram/schematic file

使用SpinalHDL狀態(tài)機(jī)生成的Verilog代碼如何導(dǎo)入到quartus工程中去呢

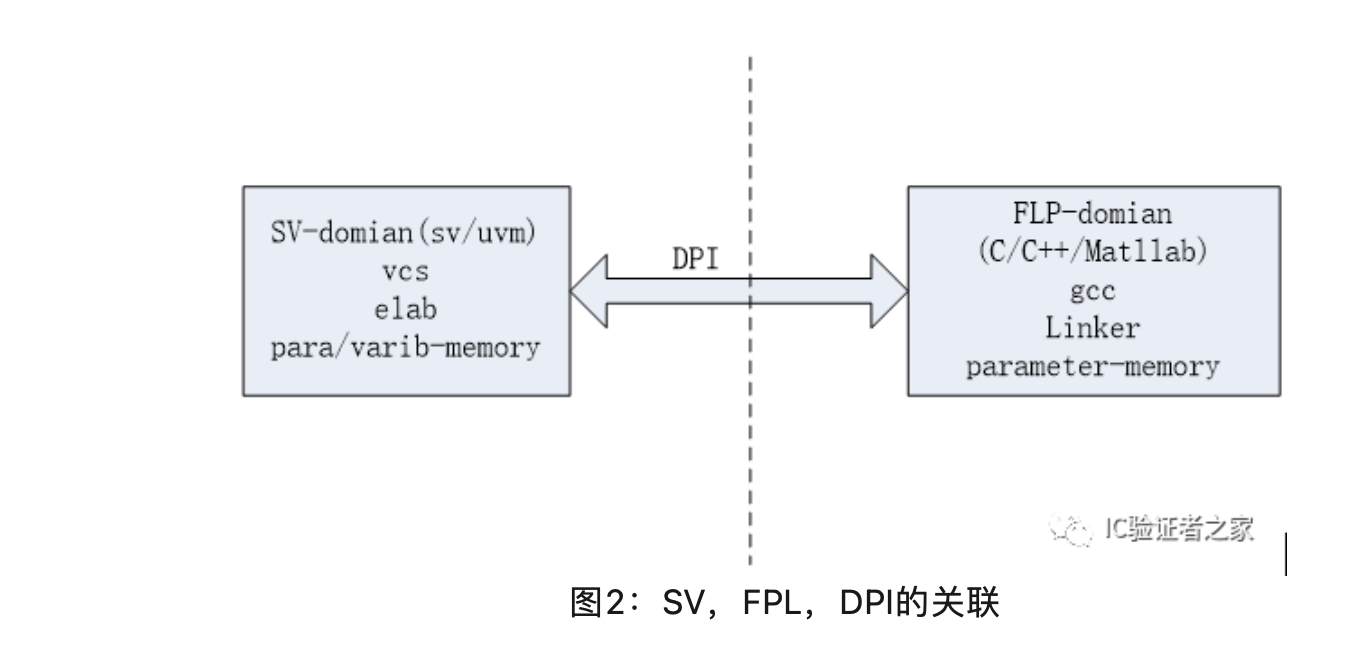

淺談System Verilog的DPI機(jī)制

做算法要學(xué)python還是C++?

現(xiàn)在公司里做設(shè)計是用SV還是Verilog?

現(xiàn)在公司里做設(shè)計是用SV還是Verilog?

評論