在今年的 DesignCon 2023 活動中,美光科技(Micron)展示了所有關于 DDR5 設計挑戰的演講,例如DRAM 內部對決策反饋均衡器 ( DFE )的需求。西門子EDA(Siemens EDA)和 Micron 聯手撰寫了一份關于該主題的 25 頁詳細白皮書,我能夠從這篇短文中歸納出一些要點。

DDR5 規范于 2020 年推出,數據傳輸帶寬為 3200MT/s,需要均衡 (EQ) 電路來解決通道損傷問題。

DFE 旨在克服符號間干擾 ( ISI ) 的影響,美光的設計人員必須考慮 DRAM DFE 中的時鐘、Rx 眼圖評估、誤碼率 (BER) 和抖動分析。IBIS-AMI模型用于對 DDR5 行為以及 EDA 工具統計仿真流程進行建模。

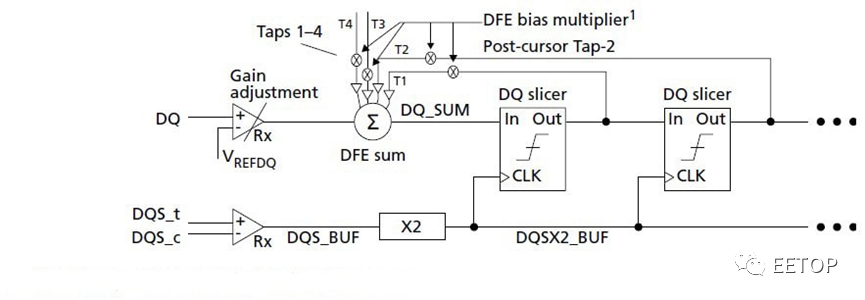

DDR5 規范的一部分是 DRAM Rx 內部的 4-tap DFE,DFE查看過去接收的數據比特,以消除比特位中的任何ISI。DFE首先應用一個電壓偏移來消除ISI,然后限幅器將當前位量化為高位或低位。EETOP編譯自semiwiki

DDR5 規范中的典型 4-tap DFE

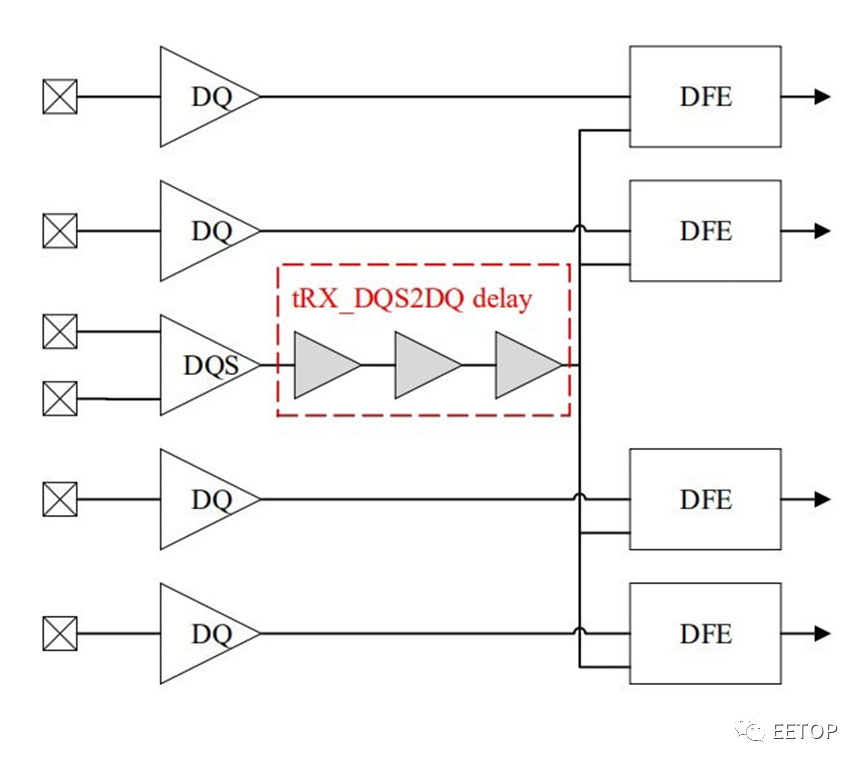

對于 DDR5,時鐘是差分選通信號(DQS_t、DQS_c),并且它沿著單端數據信號 (DQ) 轉發到 Rx。DQS 信號被緩沖,然后扇出到最多 8 個 DQ 鎖存器的時鐘輸入,從而導致時鐘樹延遲。

DQS 時鐘樹延遲

最大眼圖高度為 95mV,最大眼圖寬度為 0.25 單位間隔 (UI),或僅為 78.125ps。使用統計方法測量 1e-16 的 BER 是最實用的。

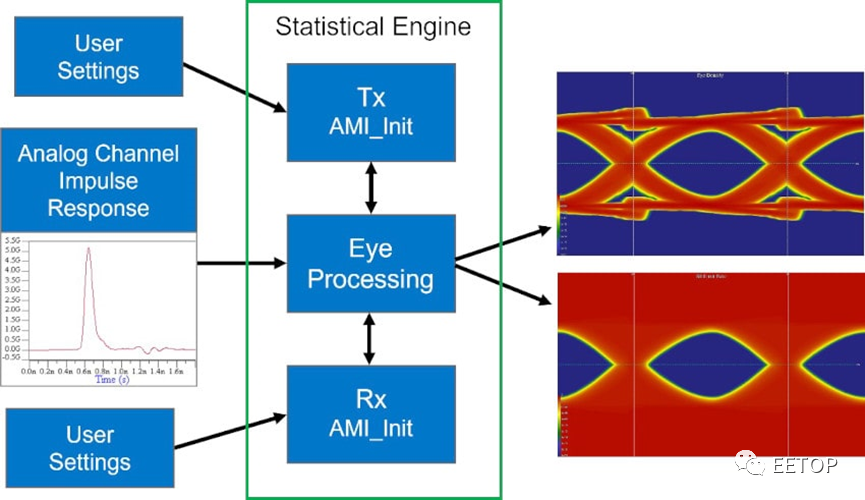

IBIS 模型已用于多代 DDR 系統,支持端到端系統仿真,但從 DDR5 開始添加 EQ 功能和 BER 眼圖模板要求,人們尋求新的仿真模型和分析。通過 IBIS-AMI 建模,可以實現快速、準確的 Si 仿真,可跨 EDA 工具移植,同時保護 IO 細節的 IP。IBIS-AMI支持統計和逐位仿真模式,統計流程如下所示。

統計仿真流程

這個流程的結果是一個統計學上的眼圖,可用于測量不同誤碼率水平下的眼圖輪廓。

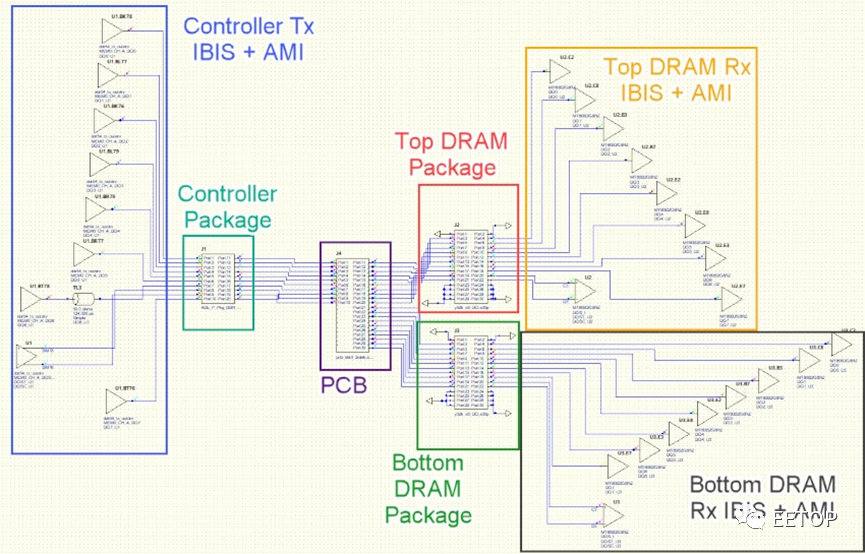

DDR5仿真實例

使用 Micron 提供的 DQ 和 DQS IBIS-AMI 模型在HyperLynx LineSim工具中對 DDR5 仿真進行建模,以下是系統原理圖。

DDR5系統原理圖

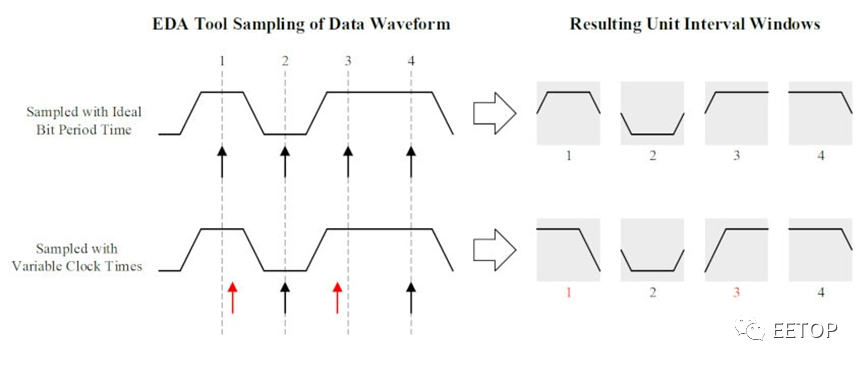

EDA工具在指定的時鐘時間捕捉波形,其中時鐘時間內的時序不確定性被轉移到所產生的輸出眼圖中,在限幅器及其時鐘量化之前重建電壓和時序裕量。

Variable clock times

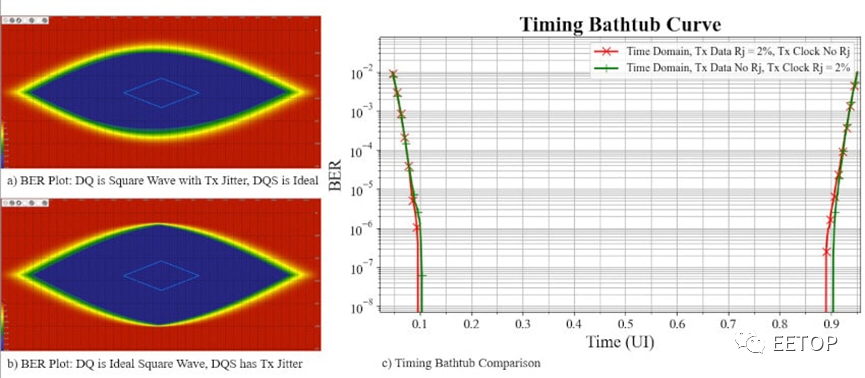

DQS 和 DQ 時序不確定性都會影響眼圖,類似于時序裕度。圖 A 顯示注入到 DQ 信號的抖動,圖 B 顯示注入到 DQS 信號的抖動。DQ(紅色)和 DQS(綠色)抖動一起顯示在圖 C 中。

Timing bathtub curve

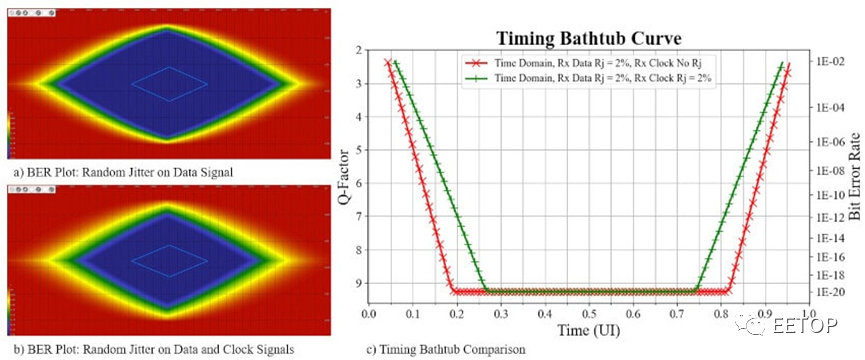

甚至可以對各種組合中的 DQ 信號和 DQS 信號進行正弦抖動效應建模,以查看 BER 和時序浴盆曲線結果。DDR5 具有 Rj、Dj 和 Tj 測量,而不是周期和周期間抖動測量。可以模擬 Rx 和 Rj 值對 BER 圖的影響以及bathtub curve時序。

數據上的 Rx Rj 與數據和時鐘組合的比較

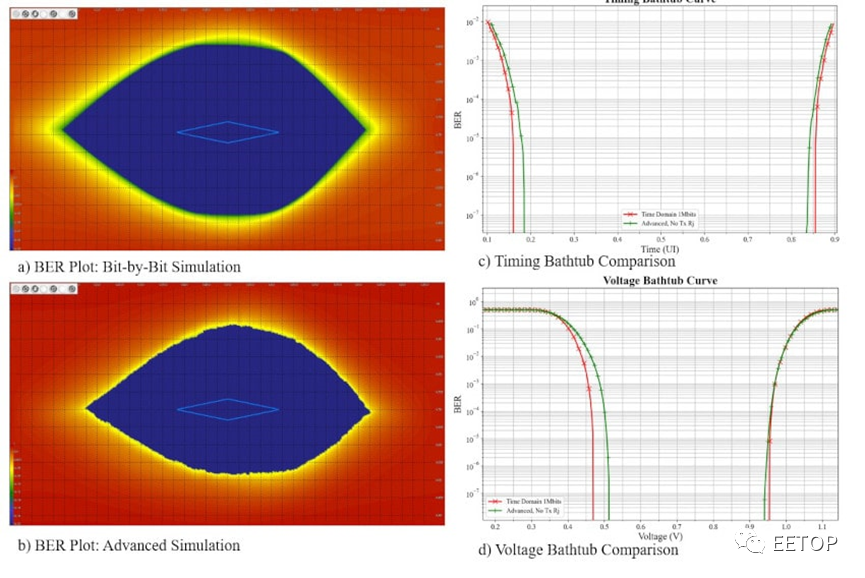

超越線性和時不變 (LTI) 建模,多重邊沿響應 (MER) 技術使用一組上升沿和下降沿。通過定制的高級 IBIS-AMI 流程,它對每個 MER 邊緣執行統計分析,然后將組合效果疊加到輸出眼圖中。

逐位高級仿真結果

在建模中添加 2% 的 Tx Rj 值可顯示更真實的 BER 降級圖結果。

總結

信號完整性效應主導 DDR5 系統的設計,因此要獲得準確的結果,需要對所有新的物理效應進行詳細建模。Rx AMI 模型的 IBS-AMI 規范已更新為使用轉發時鐘。Micron 展示了他們如何使用時鐘 DDR5 模擬流程來模擬新效應,包括非 LTI 效應,并實現 1e-16 及以下的 BER 模擬。

-

接收器

+關注

關注

14文章

2468瀏覽量

71875 -

仿真

+關注

關注

50文章

4071瀏覽量

133553 -

時鐘

+關注

關注

10文章

1733瀏覽量

131451 -

DDR5

+關注

關注

1文章

422瀏覽量

24143

發布評論請先 登錄

相關推薦

DDR5內存與DDR4內存性能差異

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

揭秘DDR5的讀寫分離技術奧秘

Rambus推出DDR5客戶端時鐘驅動器,將業界領先的內存接口芯片產品擴展到高性能 PC領域

Introspect DDR5/LPDDR5總線協議分析儀

瀾起科技率先試產DDR5時鐘驅動器( CKD )芯片

瀾起科技DDR5一代時鐘驅動器芯片試產成功

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

帶時鐘接收器的DDR5設計方法

帶時鐘接收器的DDR5設計方法

評論