AI算力在2023年呈現出快速增長態勢。一方面,千行百業的AI應用推動了算力的結構性增長機會,AI芯片繼續多樣化演進趨勢;另一方面,從大模型到AIGC,算力需求激增,且隨著模型規模和參數量的增長,算力需求仍在暴漲。

這也引發了業界的持續討論:在競逐更強、更快的未來算力時,還有哪些焦點問題不容忽視?面向更大規模的數據密集型AI應用中,居高不下的功耗問題如何解決?

國產存算一體,重大進展

在新一輪算力攻堅賽中,突破傳統馮·諾依曼架構的范式探索成為主要方向之一。存算一體架構打破了存算分離的壁壘,減少了數據的搬運,它就如同“在家辦公”的新型工作模式,消除了數據“往返通勤“的能量消耗、時間延遲,并且節約了“辦公場所”的運營成本,因而具備高能效比,成為AI算力的重要發展方向。

近來,存算一體領域有一個標志性事件值得關注:

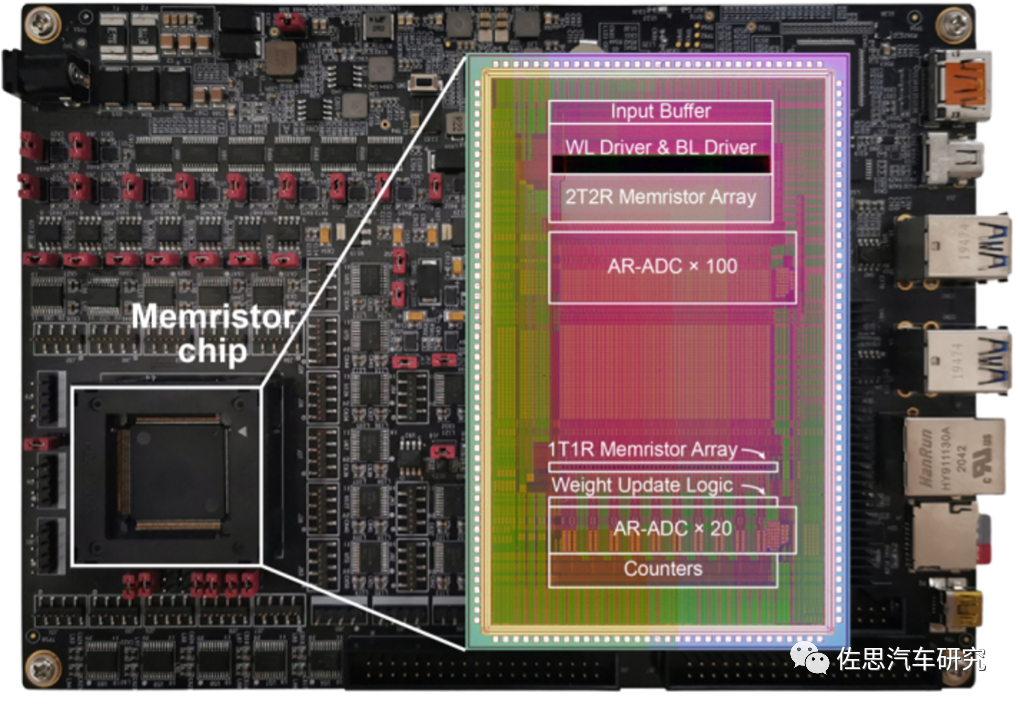

清華大學團隊研制出全球首款全系統集成、支持高效片上學習(機器學習能在硬件端直接完成)的憶阻器存算一體芯片,相關研究成果已發表在《科學》(Science)上。 憶阻器(Memristor)是繼電阻、電容、電感之后的第四種電路基本元件。它可以在斷電之后,仍能“記憶”通過的電荷,因此被當做新型納米電子突觸器件。相同任務下,該芯片實現片上學習的能耗僅為先進工藝下專用集成電路(ASIC)系統的1/35,同時有望實現75倍的能效提升。

圖:憶阻器存算一體學習芯片及測試系統(來源:清華大學官方微信)

據了解,國際上當前在該領域的研究仍停留在憶阻器陣列層面的學習功能演示,而全系統集成的憶阻器片上學習芯片仍未實現。清華大學這一突破已經走在了全球前列,展示了存算一體技術突破傳統計算架構的能效潛力和算力潛力。此外,由于具備高效的片上學習能力,可以實現數據的本地處理和動態更新,某種程度上可以降低對云端算力和網絡帶寬的依賴。

存算一體,大不相同

全球的存算一體玩家,主要可以劃分為兩大陣營:一類是國際巨頭,比如英特爾、IBM、特斯拉、三星、阿里等,巨頭對存算技術布局較早,代表存儲器未來趨勢的磁性存儲器(MRAM)、憶阻器(RRAM)等產品也相繼在頭部代工廠傳出量產消息。另一類是國內外的初創企業,比如Mythic、Tenstorrent、知存科技、后摩智能、千芯科技、億鑄科技、九天睿芯、蘋芯科技等。 由于積淀不同、優勢不同、目標場景不同,各家的存算一體方案也不盡相同,主要體現在三大差異上:技術路徑、存儲介質、以及采用的是模擬還是數字技術。

差異一:近存or存內?

先來看技術路徑的選擇。根據存儲單元與計算單元融合的程度,可以分為近存計算和存內計算兩類: 近存計算,本質上仍是存算分離架構,只不過計算模塊通常安放在存儲陣列(memory cell array)附近,數據更靠近計算單元,從而縮小了數據移動的延遲和功耗。但它依然保留了經典的馮·諾依曼架構的數據處理特點,存儲陣列通常無需改動,仍舊只提供數據的訪存功能。 近存計算的典型代表有AMD Zen系列CPU、特斯拉 Dojo、阿里達摩院使用混合鍵合3D堆疊技術實現的存算一體芯片等,還有國外創業公司Graphcore、芯片大神Jim Keller加入的創業公司Tenstorrent等,他們目前推出的存算一體芯片都屬于近存計算的范疇。 而在存內計算設計中,存儲器件參與計算操作,這通常意味著存儲陣列需要改動來支持計算。狹義上講,這才是真正的存算一體,或者說,基于器件層面實現的存算一體才真正打破了存算分離架構的壁壘。在該架構下,存儲單元和計算單元完全融合,沒有獨立的計算單元:直接在存儲器顆粒上嵌入算法,由存儲器芯片內部的存儲單元完成計算操作。 巨頭對存算一體產品的考量多是快速攻破算力和功耗瓶頸,開發出符合客戶未來需求的技術;或是利用已有成熟生態,在豐富的應用場景中快速落地。也就是說,他們除了戰略布局之外,對存算一體的一大預期是“實用、落地快”,因此,近存計算成為巨頭首選。 而初創企業由于成立時間短、技術選擇不存在路徑依賴和歷史包袱,他們反而可以另辟蹊徑,直接選擇將存儲單元和計算單元完全融合的存內計算,實現更大的突破,進一步降低對先進制程、先進封裝的依賴。例如國內的知存科技、九天睿芯、千芯科技、后摩智能等創業公司,選擇的就是存內計算路線,以期向更高性能、更通用的算力場景進行突圍。

差異二:存儲介質

存算一體依托的存儲介質呈現多樣化,比如以SRAM、DRAM為代表的易失性存儲器、以Flash為代表的非易失性存儲器等。綜合來看,不同存儲介質各有各的優點和短板。 發展較為成熟的有NOR Flash、DRAM、 SRAM等。NOR FLASH屬于非易失性存儲介質,具有低成本、高可靠性優勢,但工藝制程有瓶頸;DRAM成本低、容量大,但是速度慢,且需要電力不斷刷新;SRAM在速度方面有優勢,但容量密度小,價格高,在大陣列運算的同時保證運算精度具有挑戰。 根據<與非網>對國內多家存算一體廠商的調查來看,多數廠商當前傾向于技術成熟的SRAM設計存算一體芯片,后摩智能、千芯科技等都首先選擇SRAM啟動芯片開發。

主要原因有四點:

首先,SRAM的設計技術成熟,隨著當前工藝節點的快速發展(從90nm到3nm),SRAM位單元尺寸減小超過了35倍,最小工作電源電壓減小了超過1.25倍。

其次,跟新型非易失性存儲器相比,SRAM的制作工藝、研發工具和CMOS集成的電路模型都更加成熟穩定,同時SRAM具有更快的操作速度和耐久性,可以實時在存算單元中刷新計算數據,為大算力提供重要保障。

第三,SRAM是目前唯一一種跟先進CMOS工藝完全兼容且能大規模量產的存儲介質,這也是支持大算力的關鍵所在:從單獨存算一體宏單元的角度,SRAM跟先進工藝的兼容性使其外圍邏輯接口最能滿足當前宏單元高效利用需求。

第四,SRAM存算一體的實現途徑可以達到跟傳統馮·諾依曼架構中數字計算一致的運算精度,不需要復雜的重訓練過程,可以有效降低上層編譯器的開發難度,并提升AI模型的適用度。

不過,SRAM也有其固有瓶頸,例如較大的單元面積會導致隨著工藝發展,CMOS擴展難度相應增大,芯片計算密度增長會逐漸放緩。因此,相關企業除了考慮量產能力和落地所需,也會采用“多駕馬車”并驅的發展路線布局未來,靈汐科技、后摩智能、蘋芯科技等正在對功耗較低、存儲密度較高的新興存儲介質(比如MRAM、RRAM等)進行投入,以期隨著工藝和商業化成熟獲得更大的競爭優勢。

差異三:數字or模擬?

按照電路技術路徑分類,存算一體計算有數字存算和模擬存算的區分。近年來,學術界和工業界對二者的優缺點也有非常多的討論。總體而言,數字存算和模擬存算有其各自優缺點:

首先,數字存算保留了傳統數字電路的高抗噪性,對于不同制造工藝、電源電壓和溫度的變化呈現很強的魯棒性,因而更適合大規模高計算精度芯片的實現。而模擬存算由于模擬計算電路本身的低功耗特點,在計算精度比較固定且較低的條件下,它可以獲得更高的能量效率。

其次,數字存算要求存儲單元內容必須以數字信號形式呈現,而模擬存算可以根據存儲單元存儲機理的不同,實現不同模擬域的運算,這就意味著模擬計算可以搭載任意存儲單元來實現。

第三,相比模擬存算,數字存算實現運算靈活性較好,更適合通用性場景。模擬存算為了達到更好的能量效率,通常其關鍵模擬模塊(如A/D轉換器)的轉換精度要求相對固定,且由于不同模擬計算方式可能具有不同的計算誤差,因而這種技術路徑的擴展性略顯不足。

第四,相比數字存算,模擬計算減少了大量乘法器和加法器的面積開銷,因而在面積開銷上具有一定優勢,同時各種不同的低功耗模擬計算電路的探索,也可以進一步提升其能量效率。

技術突破疊加市場需求,存算一體來到產業化拐點

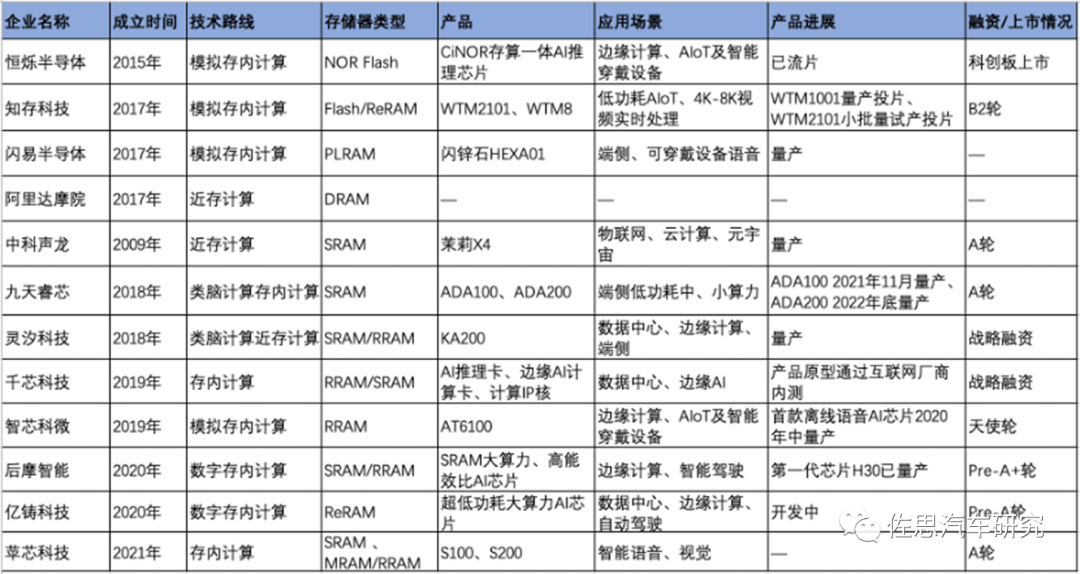

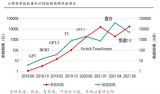

近年來,我國存算一體初創企業不斷涌現,投融資進入活躍期,迎來產業化的重要轉折點。<與非網>統計,進入2017年以來,國產存算一體芯片企業開始“扎堆”入場,并在2021年后逐步實現量產和產業化。較早成立的公司傾向于采用較為成熟的技術,主要布局低功耗、高能效需求的端側場景。隨著相關技術和應用的不斷成熟,近年來成立的初創企業藍圖更為前瞻,在大算力布局和新技術應用方面更勇于嘗新。

與非網據公開資料整理(2023.10.24)

2023年,存算一體的產業化進程有了質的突破:

小算力方面,知存科技去年量產的全球首顆基于模擬Flash存算一體的芯片WTM2101,可使用sub-mW級功耗完成大規模深度學習運算,適用于可穿戴設備中的智能語音和智能健康服務等場景,今年,該芯片出貨已經達到kk級別。

落地和產業合作方面,除了在眾多智能終端產品上的推進,知存科技聯合中國移動研究院,完成了基于 NOR Flash存算一體芯片的視頻超分技術驗證,為存算一體芯片在算力機頂盒、AR/VR 終端、邊緣視頻解碼器等場景支撐高效視覺AI應用奠定基礎。這也是存算一體芯片進一步落地廣泛終端和邊緣場景的重要基礎。

大算力方面也迎來重要的商業化轉折點。后摩智能今年上半年發布了首款存算一體智駕芯片后摩鴻途H30,最高物理算力256TOPS,典型功耗35W,成為國內率先落地存算一體大算力AI芯片的公司。據了解,H30已開始給Alpha客戶送測,第二代H50 已在研發中,將于2024年推出,支持2025年的量產車型。

放眼未來,隨著云邊端智能應用的持續增長、場景的多樣性也將繼續快速拓展,存算一體產品如何走入更廣泛應用中?相關企業仍有兩大核心挑戰需要持續攻克: 首先在存算一體AI核和SoC的架構設計和實現方面,存內計算IP雖然提供了高能效的并行計算模式,但受限于所支持運算類型的局限性,因而對架構設計的難度和復雜度要求急劇上升,既要充分利用存內計算IP本身運算的高效性,又要減少存內計算IP之間的數據傳輸,同時還要兼顧支持網絡算子的通用性和物理實現的可行性。 其次是存算一體軟件編譯器的快速部署和實現。軟件工具鏈對于發揮存算芯片的效率至關重要,軟件需要將模型切分成合適的Tensor算子,然后生成相應的指令調用底層硬件來處理。例如針對自動駕駛等場景,通過算子融合來提升計算和訪存效率是非常關鍵的一個優化目標,需要工具鏈自動化完成算子的融合、調度及對大容量存算的高效管理,以同時提升芯片的利用率和應用的開發效率等。

寫在最后

在算力越來越成為“緊俏貨”的今天,存算一體作為后摩爾時代突破芯片性能瓶頸的主流技術方向之一,開始在產業中得到越來越多的關注。國產存算一體芯片如何順流而上,早日迎來產業大發展? 短期來看,行業玩家的競爭主要集中在不同的存儲介質和技術路線。長期來看,設計方法論、測試、量產、軟件、場景的選擇等全方位競爭才是長期發展和落地的關鍵,創業公司既需要掌握從存儲器到AI芯片再到編譯器和算法的一系列技術能力,也要構建強大的生態能力。 此外,存算一體技術若能進一步融合新型憶阻器、存算一體架構、Chiplet、3D封裝等技術,將有望實現更大的有效算力、更高的能效比、實現更好的軟件兼容性,從而進一步構筑國產AI芯片的發展階梯。

編輯:黃飛

-

sram

+關注

關注

6文章

767瀏覽量

114675 -

AI

+關注

關注

87文章

30728瀏覽量

268886 -

憶阻器

+關注

關注

8文章

73瀏覽量

19863 -

機器學習

+關注

關注

66文章

8406瀏覽量

132561 -

存算一體

+關注

關注

0文章

102瀏覽量

4297

原文標題:2023年,國產存算一體走到產業化拐點

文章出處:【微信號:zuosiqiche,微信公眾號:佐思汽車研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

比存算一體更進一步,“感存算一體化”前景如何?

2PFLOPS,存算一體迎來新的卷王

不同的存算一體有什么區別?

不同的存算一體有什么區別?

評論