介紹

UART 是一種舊的串行通信機制,但仍在很多平臺中使用。它在 HDL 語言中的實現并不棘手,可以被視為本科生的作業。在這里,我將通過這個例子來展示在 HLS 中實現它是多么容易和有趣。

因此,從概念上講,這是一個微不足道的項目;然而,它對于對 HLS 感興趣的人來說是有啟發性的。

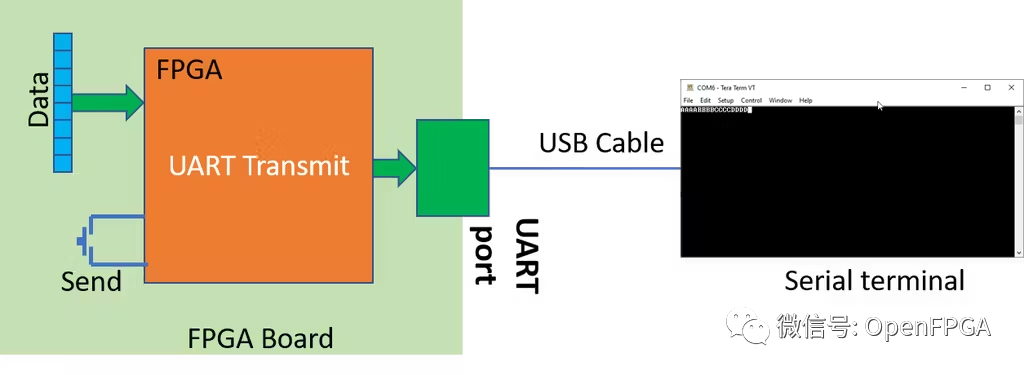

現在項目定義: 下圖顯示了項目的簡單結構。

我們在 FPGA 中的設計UART發送,每當按下按鈕時就會將其發送到計算機上的串口調試助手。

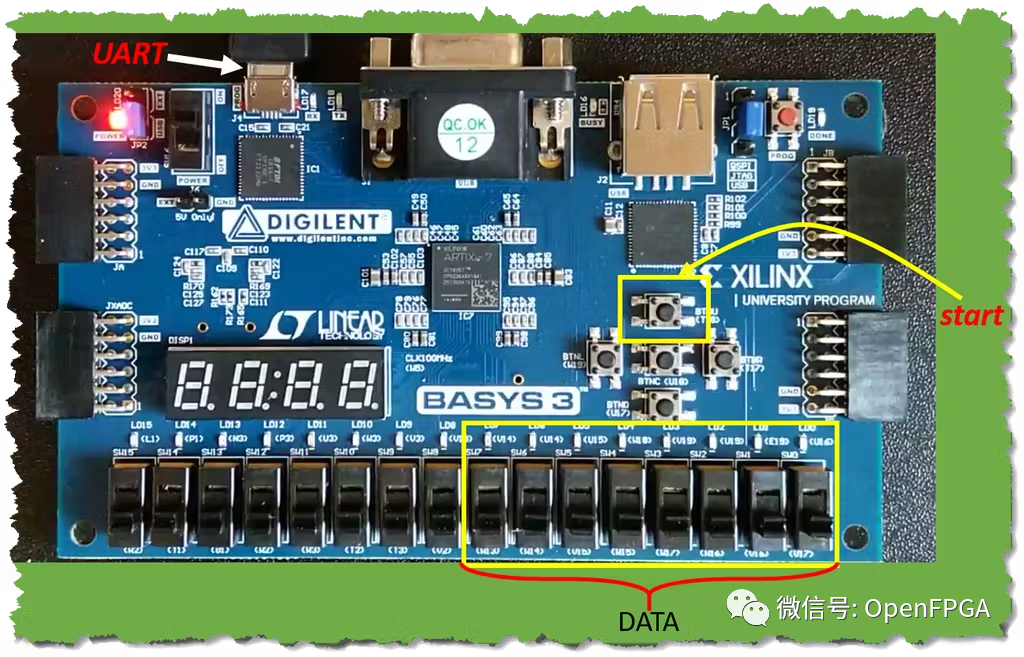

FPGA 板上的八個滑動開關用于輸入數據字節(例如字母或符號的 ASCII 代碼)。此外,UP 按鈕用作發送控制鍵。

設計很簡單,程序本身能接受開發板上撥碼開關的數據,然后添加一個“0”起始位和一個“1”停止位,最后以9600 bit/s的波特率發送出去。

首先需要根據開發板上的時鐘(本例是100MHz),進行分頻,生成串口發送所需的時鐘。

booldelay(longlongintn){

staticbooldummy=0;

for(longlongintj=0;j

生成速率時鐘后,簡單的狀態機可以將數據發送出去。

voiduart_data_transfer(bool&uart_tx,ap_uint<8>data,boolbaud_rate_clock,boolstart){

staticboolsend_bit=1;

staticboolstart_state=0;

staticbooltransfer=0;

staticunsignedintcount=0;

staticintstate=0;

ap_uint<10>d=((bool)0b1,(ap_int<8>)data,(bool)0b0);

if(start==1&&start_state==0){

transfer=1;

start_state=1;

count=0;

}

if(start==0&&start_state==1){

start_state=0;

}

if(baud_rate_clock==1&&state==0&&transfer==1){

send_bit=d[count++];

if(count==10){

transfer=0;

}

state=1;

}

if(baud_rate_clock==0&&state==1){

state=0;

}

uart_tx=send_bit;

}

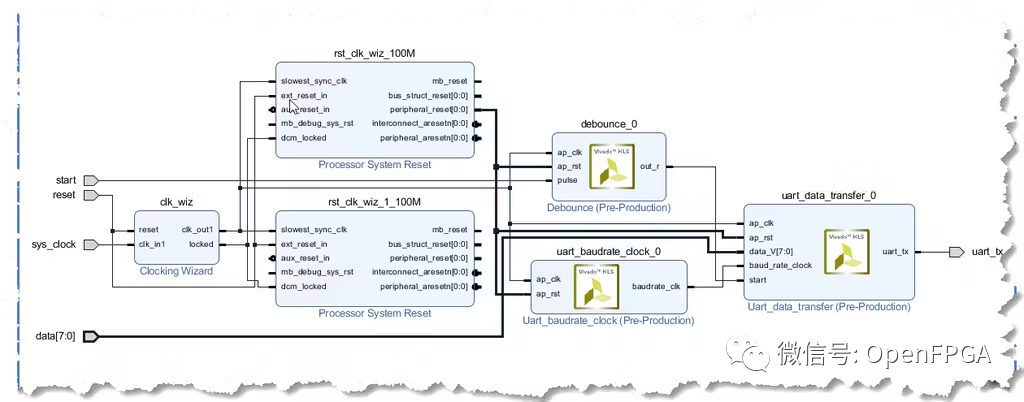

將這些代碼綜合到 RTL 模塊后,我們可以創建 Vivado 項目并生成 FPGA 比特流,并驗證。

總結

很簡單的一個實例,大家可以自行和HDL實現的方式進行對比。

審核編輯:劉清

-

FPGA

+關注

關注

1646文章

22061瀏覽量

619330 -

uart

+關注

關注

22文章

1277瀏覽量

104111 -

HDL語言

+關注

關注

0文章

48瀏覽量

9173 -

HLS

+關注

關注

1文章

133瀏覽量

24917 -

串口調試助手

+關注

關注

3文章

29瀏覽量

7020

原文標題:用 HLS 實現 UART

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

探索Vivado HLS設計流,Vivado HLS高層次綜合設計

如何用HLS實現UART

新手求助,HLS實現opencv算法加速的IP在vivado的使用

Vivado HLS設計流的相關資料分享

TI配置Hercules ARM安全MCU SCI和LIN 模塊如何用于UART通信

使用HLS封裝的縮放IP來實現視頻圖像縮放功能

FPGA——HLS簡介

HLS協議實現

調用HLS的FFT庫實現N點FFT

評論