SCR在CMOS技術的ESD保護中發揮著越來越重要的作用。一個主要的挑戰是為這些器件在ESD應力條件下開發有效的緊湊仿真模型。

前言

本文介紹一種用于LVTSCR器件SPICE仿真的簡單的宏模型等效電路建模方法。

LVTSCR介紹

隨著先進技術中器件特征尺寸的不斷減小,集成電路越來越容易受到靜電放電(ESD)的影響。可控硅整流器(SCR)通常用于為高頻引腳提供防ESD損壞的片內保護。與其他ESD器件相比,SCR占用更小的面積,具有更低的寄生電容。在CMOS技術中,通常在可控硅結構中引入MOS觸發器件以降低其固有損耗可控硅回吸觸發電壓。這種器件稱為低壓觸發可控硅(LVTSCR),具有比標準SCR更低的snapback觸發電壓。

實現LVTSCR建模的主要障礙是雪崩電流,雪崩電流是偏壓條件的復雜函數。尺寸縮小帶來的問題,隧穿電流變得重要。模型需要包含對非常快的瞬態激勵的響應,如CDM,因為它是ESD的主要失效模式。

一種新的宏觀建模方法用于模擬MOS器件中的snapback已經被報道。該模型采用標準元素構造,沒有顯式雪崩電流源。它利用了現有的先進的SPICE模型,提供了極大的簡單性,高靈活性,合理的準確性和廣泛的可用性。該方法還有一個優點,即它與大多數商業模擬器兼容。

LVTSCR中的Snapback

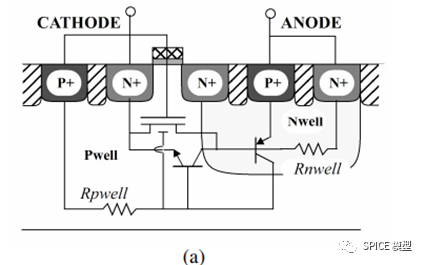

LVTSCR結構示意圖

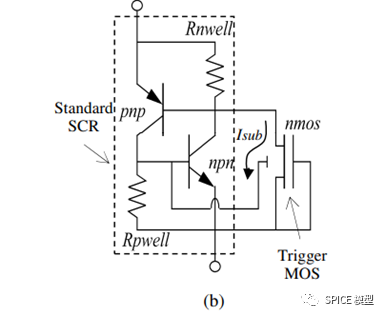

LVTSCR宏模型等效電路示意圖

LVTSCR器件的snaback物理特性:

結構可以看做一系列的PNPN擴散結,可以理解為一個PNP和一個NPN相連。添加MOS作為觸發器件,實現低snaback觸發電壓。Nwell,Pwell電阻被考慮。

原理:

LVTSCR中的snaback是由于NMOS襯底電流觸發的正反饋,主要是由NMOS Drain/Bulk 結或NPN和PNP的Base/Collector 結雪崩擊穿引起的。當正電壓施加到anode時,結是反向偏置的。當結電壓達到其擊穿電壓時,由于碰撞電離,許多空穴和電子對在耗盡層中產生。當產生的電子移動到漏極或集電極時,空穴被注入到NMOS的Pwell或Bulk。電子空穴流形成了NMOS器件的襯底電流Isub,即從漏極流向NMOS器件的襯底,或從NPN的集電極流向基極。在晶體管外部,Isub通過Rpwell電阻從NPN的基極流向發射極(從NMOS的Bulk到源極)。當Rpwell電阻上的壓降大于NPN的導通電壓(-0.7V)時,NPN導通。這導致額外的電子電流到達Drain/Bulk (Base/Collector)結耗盡區,并進一步增加產生的電子-空穴對。最終,NPN和PNP都被打開,陽極和陰極之間的電壓下降并保持在一個降低的水平。

LVTSCR器件的snaback建模的關鍵效果

Snapback之前,當NMOS占主導地位時,Drain/Bulk結起作用,isub是Vgs,Vds的函數。發生Snapback后,碰撞電離電流與Vgs的關系變得微弱。PNP, NPN占主導作用。這里介紹一種宏模型建模方法,使用標準的MOSFET, BJT模型。雪崩效應,dv/dt效應,GIDL效應和電容本質上包含在MOS和BJT模型中。BJT Mextram模型中包含了模擬雪崩擊穿效應的方程,所以可以先用BJT Mextram簡單驗證一下SCR的Snapback行為。

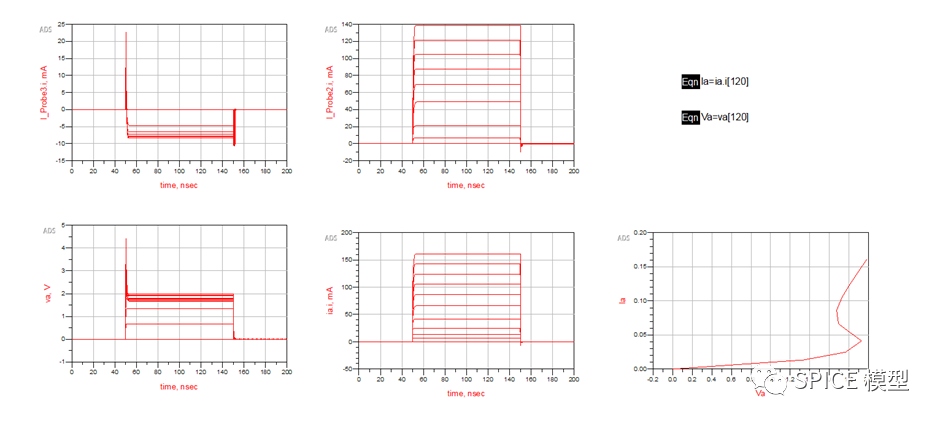

ADS中驗證電路

仿真結果

審核編輯:劉清

-

ESD

+關注

關注

50文章

2291瀏覽量

175739 -

仿真器

+關注

關注

14文章

1037瀏覽量

85379 -

等效電路

+關注

關注

6文章

293瀏覽量

33313 -

BJT

+關注

關注

0文章

238瀏覽量

18608 -

SPICE仿真

+關注

關注

1文章

27瀏覽量

6711

原文標題:使用BJT Mextram模型構建LVTSCR ESD電路仿真模型

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論