陽紅成,蘇小光

(南京航空航天大學(xué) 航空宇航學(xué)院,江蘇 南京 210016)

摘要:在現(xiàn)代電子系統(tǒng)設(shè)備和可靠性增長工作的推動下,可靠性技術(shù)和工程實踐得到了深入發(fā)展。結(jié)合工程實際經(jīng)驗,深入討論了可靠性增長過程及實現(xiàn)途徑。在保持試驗條件和改進(jìn)過程不變的條件下,實施了對具體型號電子產(chǎn)品的可靠性增長試驗,達(dá)到了預(yù)期的可靠性增長目標(biāo),并且利用可靠性增長試驗的數(shù)學(xué)模型(AMSAA模型)來評估產(chǎn)品的可靠性增長,對開展可靠性增長與可靠性增長試驗工作具有重要的實際意義。

任何產(chǎn)品的研制設(shè)計,都存在某些設(shè)計缺陷。大量的工程實踐表明,設(shè)計研制出來的整機(jī),開始的可靠性水平(MTBF)通常只有預(yù)計值的10%~30%。承制方為了達(dá)到使用方要求的使用MTBF,必須通過可靠性增長。可靠性增長的最主要作用就是通過排除系統(tǒng)性失效的原因或者減少失效發(fā)生的概率來提高產(chǎn)品的可靠性水平。

1 可靠性增長試驗

通過不斷地消除產(chǎn)品在設(shè)計或制造過程中的薄弱環(huán)節(jié),使產(chǎn)品可靠性隨時間而提高的過程,稱為可靠性增長。

產(chǎn)品的固有可靠性是由設(shè)計確定并通過制造實現(xiàn)的。由于產(chǎn)品復(fù)雜性的不斷增加和新材料、新工藝、新技術(shù)的廣泛應(yīng)用,產(chǎn)品設(shè)計需要有一個不斷認(rèn)識、不斷改進(jìn)、完善的過程。樣機(jī)在試驗或運(yùn)行當(dāng)中,不斷暴露出薄弱環(huán)節(jié),再不斷糾正、改進(jìn),從而提高產(chǎn)品的可靠性水平,逐步達(dá)到可靠性目標(biāo)值。

有計劃地激發(fā)失效,分析失效原因和改進(jìn)設(shè)計,并證明改進(jìn)措施的有效性而進(jìn)行的試驗,稱為可靠性增長試驗。大量工程實踐證明,可靠性增長試驗是提高產(chǎn)品可靠性非常重要的途徑。GJB1407-92也強(qiáng)調(diào),可靠性增長試驗是GJB450 的一個工作項目,是實現(xiàn)可靠性增長的正規(guī)途徑和主要手段。

可靠性增長是保證現(xiàn)代復(fù)雜系統(tǒng)投入使用后具有所要求的可靠性的一種有效途徑,貫穿于產(chǎn)品壽命周期的各個階段。在不同的壽命周期階段,可采用不同的方法及技術(shù)實現(xiàn)可靠性增長。

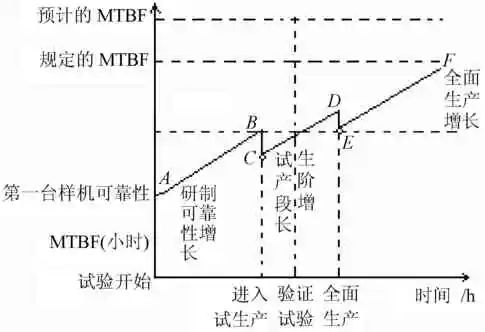

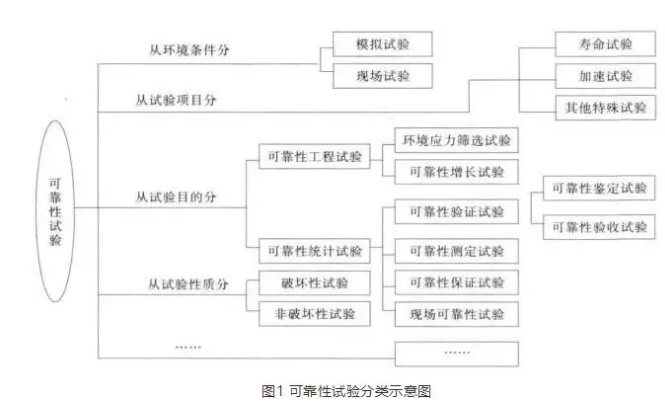

圖1直觀地表示一個理想的可靠性增長過程。

圖1 理想的可靠性增長過程

第一階段:研制階段。第一臺樣機(jī)研制出來時,由于存在設(shè)計缺陷等系統(tǒng)性薄弱環(huán)節(jié),初始的平均故障間隔時間(MTBF)較低(A點(diǎn))。在可靠性增長研制試驗以及其他試驗中,不斷地暴露出系統(tǒng)性失效,通過分析,有針對性地采取糾正措施,進(jìn)行設(shè)計更改,一直到研制階段結(jié)束,可靠性在不斷增長,達(dá)到B點(diǎn)。

第二階段:試生產(chǎn)階段。由于設(shè)計階段樣機(jī)數(shù)量較少,設(shè)計缺陷很難充分暴露出來,特別是批次性的元器件缺陷不能充分暴露出來;設(shè)計階段元器件由設(shè)計人員掌握,設(shè)計更改、元器件更換隨意性較大,往往會掩蓋設(shè)計方面的不足和元器件方面的缺陷;樣機(jī)的應(yīng)力篩選試驗很充分,而生產(chǎn)階段的產(chǎn)品不可能有如此長的環(huán)境應(yīng)力篩選周期。所以,在試生產(chǎn)開始的時候,使產(chǎn)品的可靠性低于樣品研制結(jié)束時的可靠性,從B點(diǎn)下降到C點(diǎn)。在試生產(chǎn)過程中,通過繼續(xù)采用糾正、改進(jìn)措施,可靠性將不斷增長,達(dá)到D點(diǎn)。

第三階段:批生產(chǎn)和使用階段。在批生產(chǎn)開始的時候,由于工藝缺陷、裝配缺陷以及質(zhì)量控制問題,可能使批生產(chǎn)產(chǎn)品的可靠性水平從D點(diǎn)下降到E點(diǎn)。隨著關(guān)鍵問題的不斷解決,各種工藝缺陷、裝配缺陷得到糾正,可靠性將繼續(xù)增長,達(dá)到規(guī)定的MTBF。

由以上可知,實現(xiàn)可靠性增長是反復(fù)設(shè)計、反復(fù)糾正的結(jié)果。隨著設(shè)計的成熟,研究確定實際存在(通過試驗)的或潛在(通過分析)的故障源,進(jìn)一步的設(shè)計工作應(yīng)當(dāng)放在改正這些問題上。從理論上講,產(chǎn)品壽命期的各個階段都可以實現(xiàn)可靠性增長,但是對于各階段所進(jìn)行的可靠性增長,在經(jīng)濟(jì)性和及時性方面又都各不相同。

研制階段實現(xiàn)可靠性增長的主要優(yōu)點(diǎn)是費(fèi)用低,更改設(shè)計方便、及時。研制階段進(jìn)行可靠性增長的主要信息來源有3個方面。

(1) 經(jīng)驗信息

包括同類產(chǎn)品使用信息、同類產(chǎn)品可靠性增長經(jīng)驗、歷史經(jīng)驗數(shù)據(jù)、技術(shù)經(jīng)驗、各種數(shù)據(jù)庫及出版物。這些信息在方案設(shè)計階段就可利用,以通過更改早期設(shè)計來實現(xiàn)可靠性增長,因此具有很好的及時性和經(jīng)濟(jì)性。

(2) 分析信息

在對新產(chǎn)品的研制進(jìn)行方案論證時,對新研制系統(tǒng)進(jìn)行分析、產(chǎn)品研制成熟程度、研究及評審所獲得的信息,如可行性研究、權(quán)衡分析、可靠性預(yù)計、FMECA、故障樹分析、以及設(shè)計評審等所獲得的信息。利用分析信息實現(xiàn)可靠性增長的優(yōu)點(diǎn)是及時性和經(jīng)濟(jì)性較好,特別是對于高可靠性要求的產(chǎn)品,可以減少或避免某些費(fèi)時和昂貴的試驗。

(3) 試驗信息

產(chǎn)品在研制階段可利用的試驗信息種類多、范圍廣。研制過程各個階段、各個層次的產(chǎn)品在各種環(huán)境條件下進(jìn)行各種類型的試驗都能提供有價值的信息。試驗信息是實現(xiàn)可靠性增長最為通用的信息源,利用試驗信息實現(xiàn)可靠性增長的主要優(yōu)點(diǎn)是具有很高的確實性。盡管試驗費(fèi)用是影響利用試驗信息實現(xiàn)可靠性增長的主要障礙,但是,在實現(xiàn)可靠性增長的過程中,最經(jīng)濟(jì)有效的方法仍是在研制階段合理安排各種可靠性試驗,比如可靠性增長試驗,他便于在產(chǎn)品研制早期確定故障模式,設(shè)計更改更容易,試驗費(fèi)用和風(fēng)險更低,具有更好的及時性和經(jīng)濟(jì)性。其與環(huán)境試驗及性能試驗相比,具有更系統(tǒng)、全面和深入發(fā)現(xiàn)故障,確實性好,效費(fèi)比更高的優(yōu)點(diǎn),因此,可靠性增長試驗是目前國外在實現(xiàn)可靠性增長過程中廣泛采用的方法。

2 可靠性增長試驗的AMSAA模型

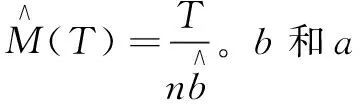

AMSAA模型假設(shè)產(chǎn)品在開發(fā)期(0,t]內(nèi)失效次數(shù)N(t)是具有均值函數(shù)EN(t)=abt及瞬時強(qiáng)度λ(t)=abtb-1的非齊次Poisson過程,參數(shù)a>0,b>0。a和b分別稱為尺度參數(shù)和形狀參數(shù)。當(dāng)b=1,λ(t)=a,非齊次Poisson過程退化為Poisson過程,失效時間間隔服從指數(shù)分布,產(chǎn)品可靠性沒有趨勢,既不增長也不下降。當(dāng)b<1時,A(t)遞減,表明可靠性增長。當(dāng)b>1時,A(t)遞增,表明可靠性下降。

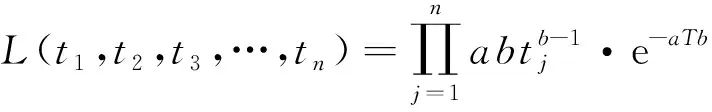

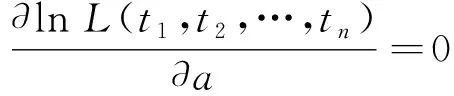

對于時間截尾,給定Tj,在(0,T)內(nèi)發(fā)生n>1次失效,失效時間為0

則:

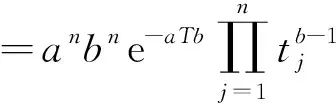

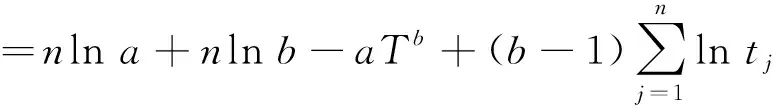

lnL(t1,t2,…,tn)

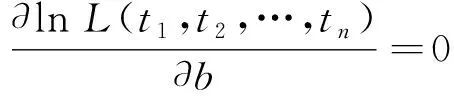

可得:

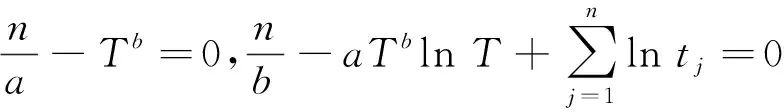

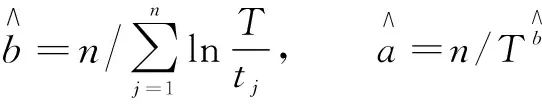

因此,解方程組得b和a的極大似然估計為:

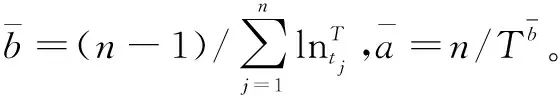

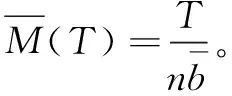

在時刻T,產(chǎn)品MTBF的極大似然估計為 的無偏估計值為

的無偏估計值為 在時刻T,產(chǎn)品MTBF的無偏估計值為

在時刻T,產(chǎn)品MTBF的無偏估計值為

3 利用AMSAA模型對某型產(chǎn)品的可靠性增長試驗分析

某臺產(chǎn)品在可靠性增長試驗中共發(fā)生了52次失效,失效發(fā)生時刻(h)分別在2,5,9,16,18,19,21,25,38,40,42,45,47,65,89,97,104,105,120,193,214,217,250,261,285,287,289,305,329,357,372,374,393,403,466,521,556,571,621,628,642,684,732,735,754,790,805,807,830,835,872,972。試驗在T=1 000 h結(jié)束,現(xiàn)對失效數(shù)據(jù)進(jìn)行分析,并且求出試驗結(jié)束時的MTBF。

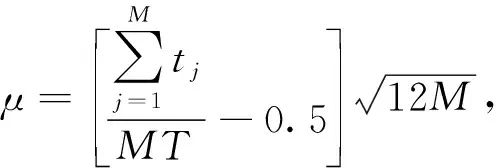

(1) 趨勢分析

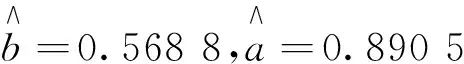

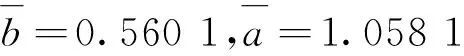

(2) 參數(shù)估計

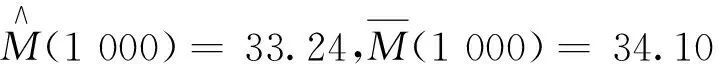

(3) MTBF的估計

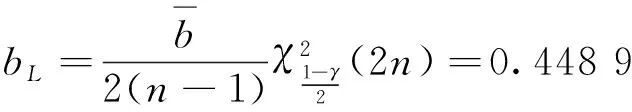

(4)b的置信區(qū)間

對置信水平γ=0.90,形狀參數(shù)b的置信區(qū)間[bLbU]為:

通過可靠性增長試驗,到試驗結(jié)束時刻產(chǎn)品的MTBF比初始MTBF增長了近10倍,達(dá)到可靠性的目標(biāo)值。

4 結(jié) 語

在產(chǎn)品研制過程中,除了可靠性試驗外,還經(jīng)常會進(jìn)行許多試驗,如工程設(shè)計試驗、性能試驗、環(huán)境試驗等。這些試驗當(dāng)中含有大量失效信息,各方應(yīng)盡可能地利用產(chǎn)品各個階段的資源與信息,將各種試驗信息結(jié)合起來,進(jìn)行科學(xué)的可靠性增長管理,經(jīng)濟(jì)、高效地促使產(chǎn)品達(dá)到預(yù)定的可靠性目標(biāo)。

來源 |《現(xiàn)代電子技術(shù)》

審核編輯:湯梓紅

-

電子產(chǎn)品

+關(guān)注

關(guān)注

6文章

1190瀏覽量

58948 -

模型

+關(guān)注

關(guān)注

1文章

3440瀏覽量

49642 -

現(xiàn)代電子系統(tǒng)

+關(guān)注

關(guān)注

0文章

2瀏覽量

5400

原文標(biāo)題:電子產(chǎn)品研制階段可靠性增長試驗研究

文章出處:【微信號:現(xiàn)代電子技術(shù),微信公眾號:現(xiàn)代電子技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

淺談手機(jī)環(huán)境可靠性試驗

汽車電子產(chǎn)品環(huán)境可靠性測試

汽車電子產(chǎn)品環(huán)境可靠性測試

電子產(chǎn)品的失效原因分析

六類可靠性試驗的異同,終于搞懂了!

電子產(chǎn)品研制階段可靠性增長試驗研究

電子產(chǎn)品的可靠性與噪聲

電子產(chǎn)品的可靠性試驗類型和目的資料詳細(xì)說明

詳解電子產(chǎn)品的可靠性試驗

評論