導(dǎo)讀:

在選擇FPGA時(shí),關(guān)注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因?yàn)樗鼈兪荈PGA架構(gòu)中的兩個(gè)核心資源,對(duì)于設(shè)計(jì)的性能和資源利用至關(guān)重要。

BRAM(Block Random Access Memory,隨機(jī)存取內(nèi)存塊),塊RAM是嵌在FPGA內(nèi)部、固定大小(容量)的硬IP。

為什么要嵌入豐富的塊RAM?對(duì)于需要大量存儲(chǔ)器的應(yīng)用,比如需要大規(guī)模的數(shù)據(jù)存儲(chǔ),如圖像、視頻、音頻等,塊RAM是一個(gè)理想的選擇。塊RAM提供了高密度的存儲(chǔ),能夠有效地存儲(chǔ)和檢索大量數(shù)據(jù);對(duì)于需要頻繁訪問(wèn)的數(shù)據(jù),塊RAM可以用作數(shù)據(jù)緩存;一些算法可能需要大量的中間數(shù)據(jù)存儲(chǔ),使用塊RAM可以提供快速且容量大的存儲(chǔ),用來(lái)支持這些算法的運(yùn)行;異步時(shí)鐘域之間的數(shù)據(jù)傳輸通常需要使用FIFO(First-In-First-Out)緩沖區(qū)。

在FPGA開(kāi)發(fā)中,使用塊RAM的多少取決于設(shè)計(jì)的性質(zhì)和對(duì)性能的需求。在設(shè)計(jì)過(guò)程中,通過(guò)合理的資源規(guī)劃和優(yōu)化,可以有效地利用塊RAM以滿足應(yīng)用的需求。

注:以xilinx7系列690T為例

塊RAM的分布

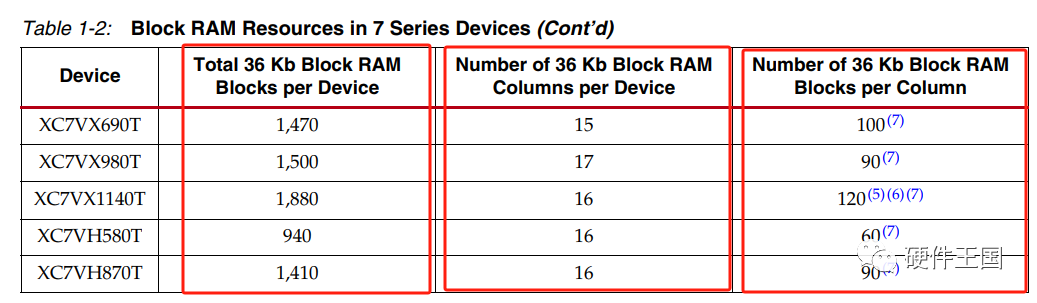

圖1:產(chǎn)品選型指南

一些應(yīng)用可能更加側(cè)重于邏輯資源,而另一些應(yīng)用可能更加側(cè)重于存儲(chǔ)資源,如上圖1所示,以690t為例,Block RAM總數(shù)目為1470,總?cè)萘繛?2920kb。上圖中的Distributed RAM 是 FPGA中的一種內(nèi)置存儲(chǔ)器資源。與塊RAM不同,分布式RAM分散在FPGA的邏輯區(qū)域中,而不是集中在特定的塊中。分布式RAM主要由可編程邏輯元件(LUTs)和觸發(fā)器(Flip-Flops)組成。每個(gè)LUT都有一些存儲(chǔ)單元,用于存儲(chǔ)少量的數(shù)據(jù)。這些存儲(chǔ)單元可以被組合起來(lái),形成一個(gè)分布式的存儲(chǔ)器。簡(jiǎn)單的說(shuō)Distributed RAM就是FPGA用內(nèi)部的邏輯單元拼湊而來(lái)的。一般較少使用,本文不重點(diǎn)討論。

圖2:7系列 塊RAM資源

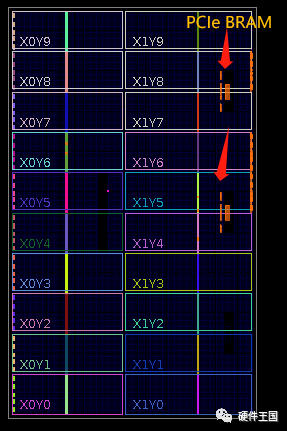

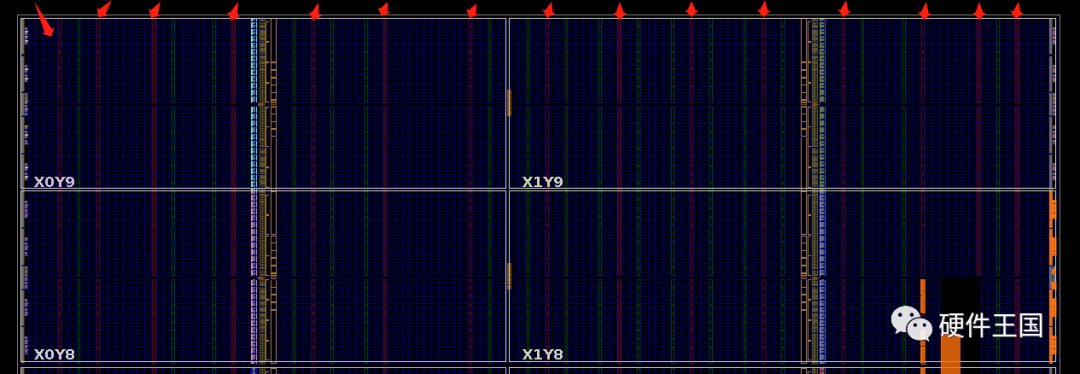

如圖2可知,690T一共包含1470個(gè)塊RAM,一個(gè)有15“列” 36Kb的BRAM,每“列”有100個(gè)36Kb的BRAM。結(jié)合下文圖3、圖4用Vivado打開(kāi)實(shí)際device(690T)的視圖說(shuō)明,看過(guò)我前面文章的讀者可知,690T一共20個(gè)時(shí)鐘區(qū)域,圖4是將圖3最上方4個(gè)時(shí)鐘區(qū)域放大后的截圖,先看圖4,其中每一個(gè)小紅箭頭代表1“列”36kb的BRAM,一共15個(gè)小紅箭頭(每以列共100個(gè)36kb的BRAM)。細(xì)心的讀者可能發(fā)現(xiàn),圖2的表格一共有15列,每列100個(gè),總數(shù)應(yīng)該是1500個(gè),為什么圖2的表格總數(shù)只有1470?答案就在圖3里面,因?yàn)橛幸恍〣RAM已經(jīng)分配給一些高速硬核使用了,比如690T的PCIe 硬IP。

圖3:Device視圖

圖4:Device視圖(圖3最上方4個(gè)時(shí)鐘區(qū)域放大截圖)

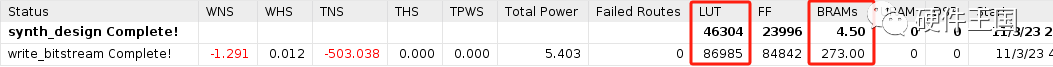

圖5:工程“綜合實(shí)現(xiàn)”后的資源消耗指示圖

圖5是筆者基于690T開(kāi)發(fā)的一個(gè)實(shí)際工程綜合實(shí)現(xiàn)后的資源消耗,BRAM一共使用273個(gè),評(píng)估你所選擇的FPGA是否合適,最主要就是看邏輯資源和BRAM使用情況,當(dāng)然特殊要求除外(如DSP、其他硬IP等)

塊RAM的特性和按“列”分布原因

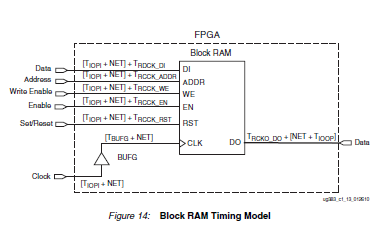

FPGA塊RAM的特性很多,讀者不在這里細(xì)述每一個(gè)特性,讀者自行參考廠商原文檔,因?yàn)槭怯睮P。可能每個(gè)廠商支持的特性各不相同,使用時(shí)需要注意幾點(diǎn)的是:

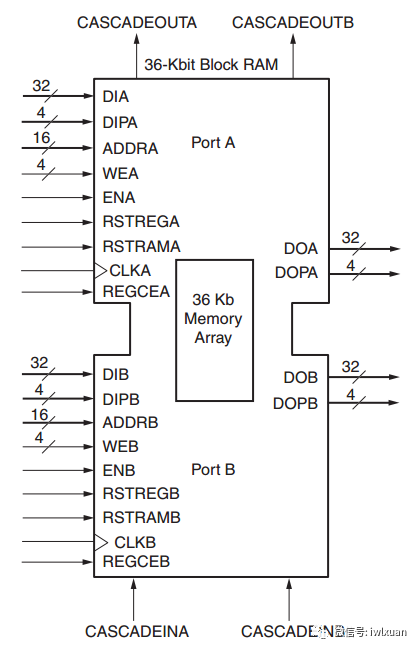

- 每個(gè)塊RAM均可存儲(chǔ)最多36 Kbits的數(shù)據(jù)(每個(gè)廠商的內(nèi)嵌的塊大小可能不一樣);

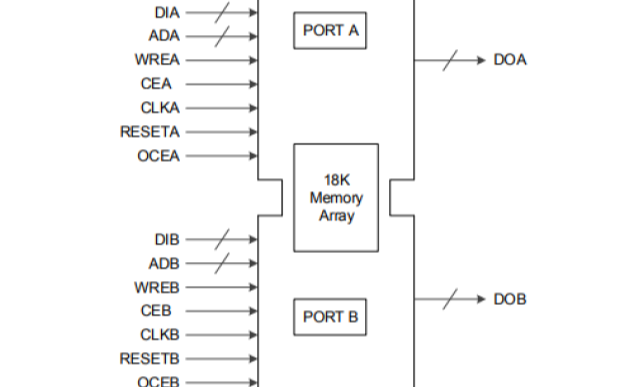

- 支持將一個(gè)單獨(dú)的36Kb塊RAM分成兩個(gè)獨(dú)立的18Kb塊使用(具體看廠商規(guī)格書(shū));

- 兩個(gè)相鄰的塊RAM可以組合成一個(gè)更深的64K x 1內(nèi)存(具體看廠商規(guī)格書(shū));

- 支持端口模式(簡(jiǎn)單雙端口(SDP)、真雙端口(TDP)。(具體看廠商規(guī)格書(shū))。

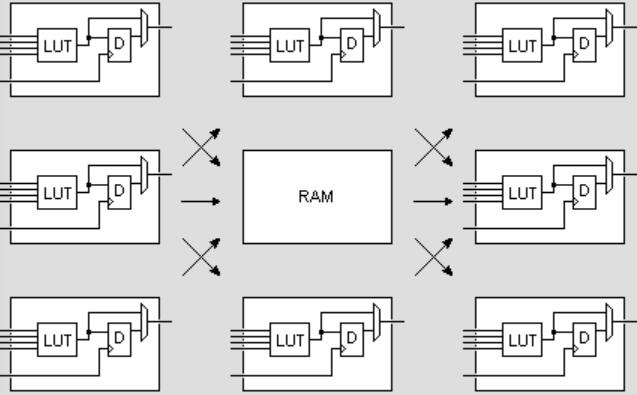

FPGA中的塊RAM按列分布的設(shè)計(jì)選擇通常是出于性能和資源利用的考慮。這種設(shè)計(jì)決策涉及到FPGA內(nèi)部架構(gòu)和數(shù)據(jù)流的優(yōu)化。

- 性能優(yōu)化: FPGA內(nèi)部的塊RAM通常是在每個(gè)列中集中分布。這樣設(shè)計(jì)有助于減小數(shù)據(jù)路徑的長(zhǎng)度,從而減小延遲,提高訪問(wèn)速度。如果塊RAM散布在整個(gè)FPGA芯片上,可能需要更長(zhǎng)的路徑來(lái)連接塊RAM和其他邏輯單元,導(dǎo)致性能下降。

- 資源共享: FPGA中的資源是有限的,通過(guò)將塊RAM集中在每個(gè)列中,可以更好地進(jìn)行資源共享。這有助于防止資源爭(zhēng)用和碎片化,使得在某一列中的塊RAM更容易分配給鄰近的邏輯單元,減少資源沖突。

- 時(shí)序和布線簡(jiǎn)化: FPGA中的時(shí)序分析和布線操作通常是按列進(jìn)行的。將塊RAM集中在每一列中可以簡(jiǎn)化時(shí)序分析,減小時(shí)序問(wèn)題的復(fù)雜性,使得設(shè)計(jì)更容易達(dá)到目標(biāo)時(shí)鐘頻率。

總結(jié)

按列分布?jí)KRAM是一種有效的設(shè)計(jì)選擇,有助于提高性能、優(yōu)化資源利用,并簡(jiǎn)化時(shí)序和布線操作。不過(guò),具體的FPGA架構(gòu)和設(shè)計(jì)工具可能會(huì)有一些差異,因此在具體的FPGA系列和工具鏈中可能會(huì)有一些微妙的差異。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163765 -

RAM

+關(guān)注

關(guān)注

8文章

1368瀏覽量

114643 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3019瀏覽量

74005 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2000瀏覽量

61132

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA芯片內(nèi)部結(jié)構(gòu)解析(2)

介紹FPGA開(kāi)發(fā)板內(nèi)部ram操作

Vivado的多種RAM編寫(xiě)方式

在FPGA設(shè)計(jì)中如何用LUT組建分布式的RAM

FPGA內(nèi)嵌的塊RAM在FFT算法中的應(yīng)用

采用FPGA與IP來(lái)實(shí)現(xiàn)DDR RAM控制和驗(yàn)證的方法

Spartan-6 FPGA塊RAM的技術(shù)參考資料免費(fèi)下載

詳細(xì)介紹關(guān)于FPGA開(kāi)發(fā)板內(nèi)部ram是如何操作的

FPGA的RAM存儲(chǔ)資源詳細(xì)資料說(shuō)明

FPGA中塊RAM的分布和特性

FPGA中塊RAM的分布和特性

評(píng)論