作者:Coventor(泛林集團旗下公司)半導體工藝與整合團隊成員Yu De Chen

介紹

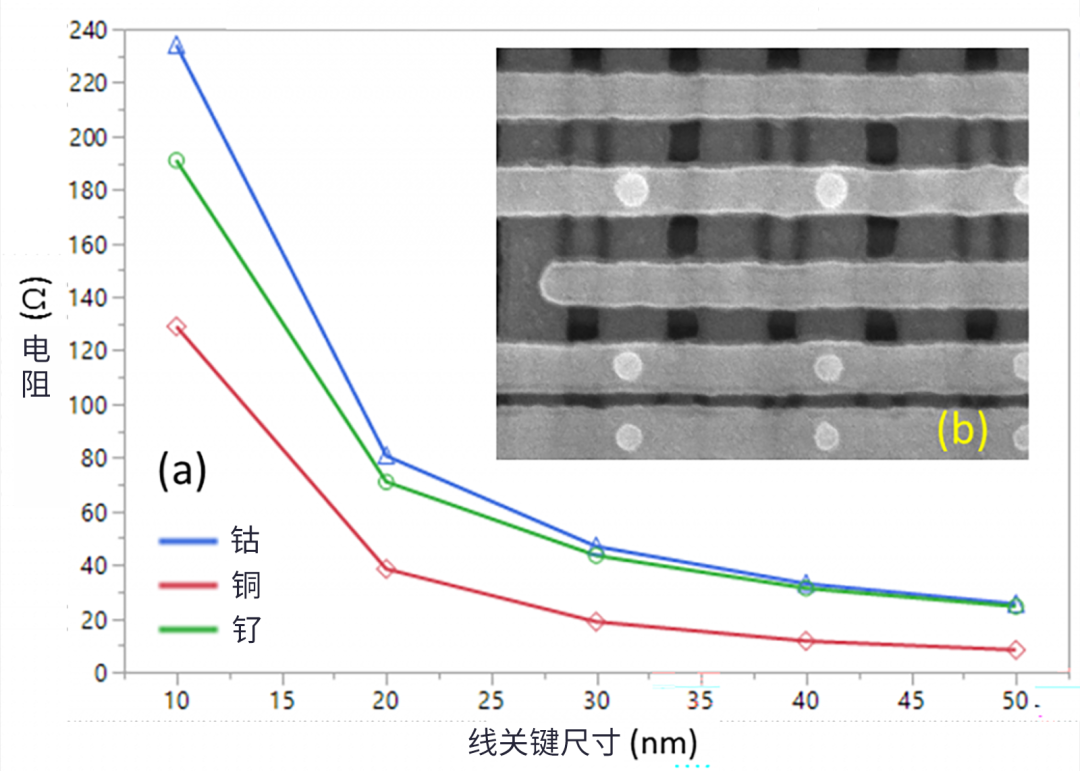

由后段制程(BEOL)金屬線寄生電阻電容(RC)造成的延遲已成為限制先進節點芯片性能的主要因素[1]。減小金屬線間距需要更窄的線關鍵尺寸(CD)和線間隔,這會導致更高的金屬線電阻和線間電容。圖1對此進行了示意,模擬了不同后段制程金屬的線電阻和線關鍵尺寸之間的關系。即使沒有線邊緣粗糙度(LER),該圖也顯示電阻會隨著線寬縮小呈指數級增長[2]。為緩解此問題,需要在更小的節點上對金屬線關鍵尺寸進行優化并選擇合適的金屬材料。

除此之外,線邊緣粗糙度也是影響電子表面散射和金屬線電阻率的重要因素。圖1(b)是典邏輯5nm后段制程M2線的掃描電鏡照片,可以看到明顯的邊緣粗糙度。最近,我們使用虛擬工藝建模,通過改變粗糙度振幅(RMS)、相關長度、所用材料和金屬線關鍵尺寸,研究了線邊緣粗糙度對線電阻的影響。

圖1:(a) 線電阻與線關鍵尺寸的關系;(b) 5nm M2的掃描電鏡俯視圖(圖片來源:TechInsights)

實驗設計與執行

在晶圓廠里,通過改變線關鍵尺寸和金屬來進行線邊緣粗糙度變化實驗很困難,也需要花費很多時間和金錢。由于光刻和刻蝕工藝的變化和限制,在硅晶圓上控制線邊緣粗糙度也很困難。因此,虛擬制造也許是一個更直接和有效的方法,因為它可以“虛擬地”生成具有特定線邊緣粗糙度的金屬線結構,進而計算出相應顯粗糙度條件下金屬的電阻率。

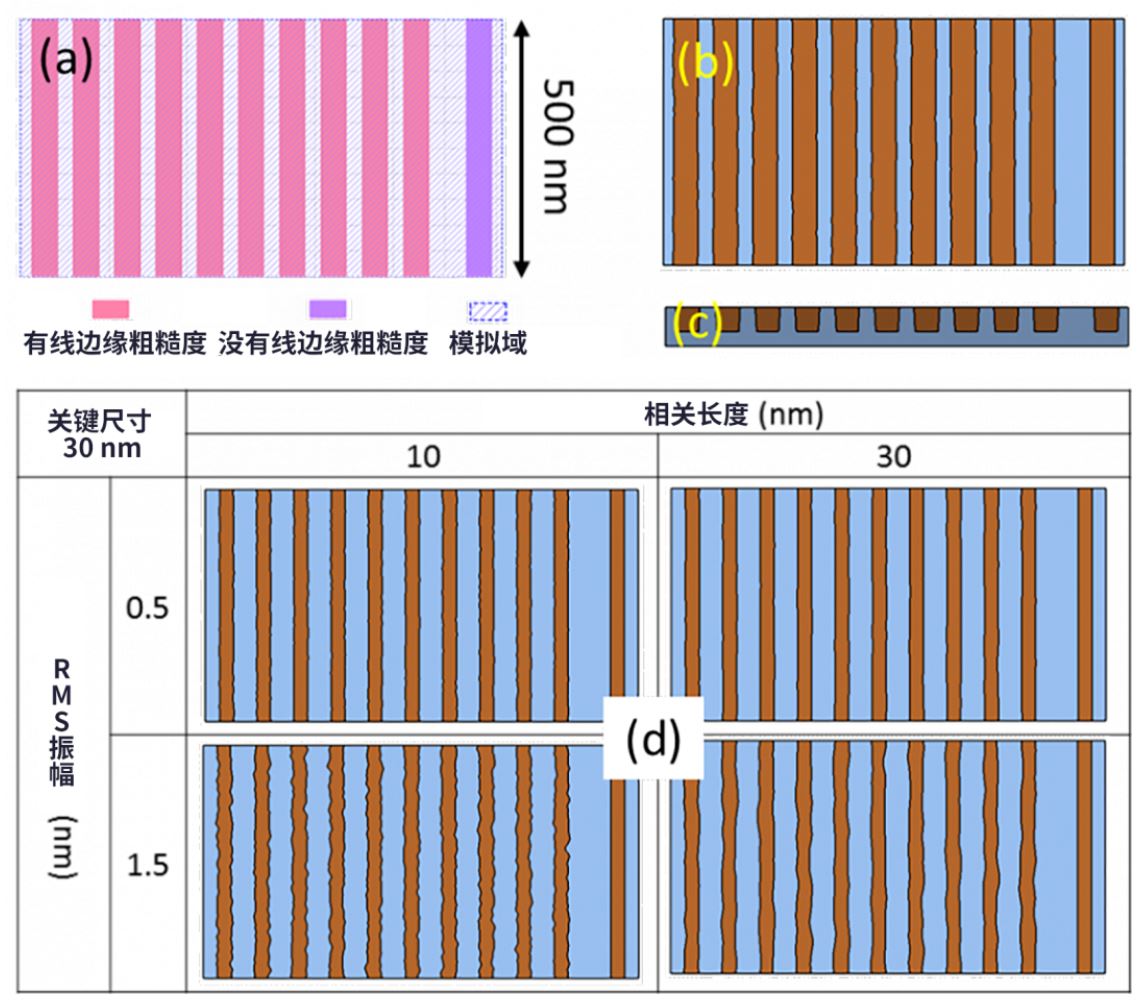

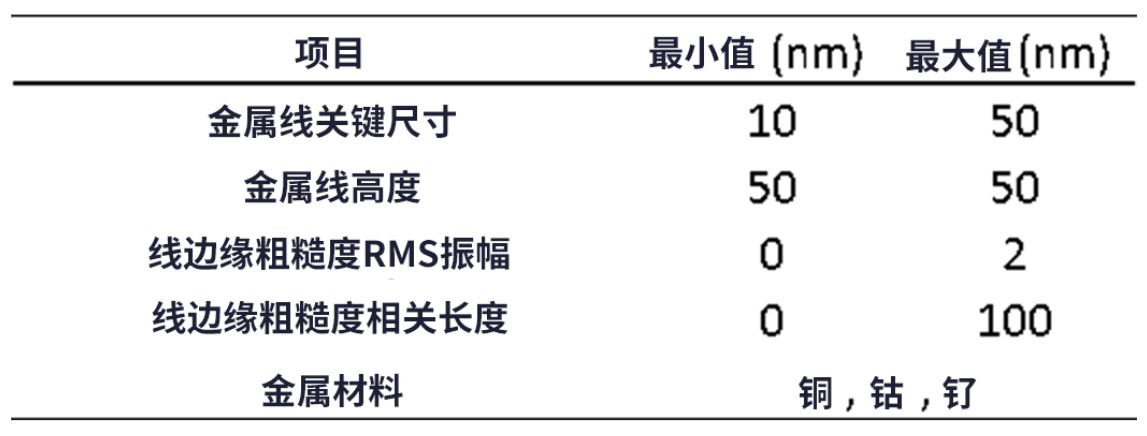

圖2(a)顯示了使用虛擬半導體建模平臺 (SEMulator3D?) 模擬金屬線邊緣粗糙度的版圖設計。圖2(b)和2(c)顯示了最終的虛擬制造結構及其模擬線邊緣粗糙度的俯視圖和橫截面圖。通過設置具體的粗糙度振幅(RMS)和相關長度(噪聲頻率)值,可以在虛擬制造的光刻步驟中直接修改線邊緣粗糙度。圖2(d)顯示了不同線邊緣粗糙度條件的簡單實驗。圖中不同RMS振幅和相關長度設置條件下,金屬的線邊緣展示出了不同的粗糙度。這些數據由SEMulator3D的虛擬實驗仿真生成。為了系統地研究不同的關鍵尺寸和材料及線邊緣粗糙度對金屬線電阻的影響,使用了表1所示的實驗條件進行結構建模,然后從相應結構中提取相應條件下的金屬線電阻。需要說明的是,為了使實驗更為簡單,模擬這些結構時沒有將內襯材料納入考慮。

圖2:(a) 版圖設計;(b) 生成的典型金屬線俯視圖;(c) 金屬線的橫截面圖;(d) 不同RMS和相關長度下的線邊緣粗糙度狀態

表1: 實驗設計分割條件

實驗設計結果與分析

為了探究線邊緣粗糙度對金屬線電阻的影響,用表1所示條件完成了約1000次虛擬實驗設計。從這些實驗中,我們了解到:

1. 當相關長度較小且存在高頻噪聲時,電阻受到線邊緣粗糙度的影響較大。

2. 線關鍵尺寸較小時,電阻受線邊緣粗糙度RMS振幅和相關長度的影響。

3. 在所有線關鍵尺寸和線邊緣粗糙度條件下,應選擇特定的金屬來獲得最低的絕對電阻值。

結論

由于線邊緣粗糙度對較小金屬線關鍵尺寸下的電阻有較大影響,線邊緣粗糙度控制在先進節點將變得越來越重要。在工藝建模分割實驗中,我們通過改變金屬線關鍵尺寸和金屬線材料研究了線邊緣粗糙度對金屬線電阻的影響。

在EUV(極紫外)光刻中,由于大多數EUV設備測試成本高且能量密度低,關鍵尺寸均勻性和線邊緣粗糙度可能會比較麻煩。在這種情況下,可能需要對光刻顯影進行改進,以盡量降低線邊緣粗糙度。這些修改可以進行虛擬測試,以降低顯影成本。新的EUV光刻膠方法(例如泛林集團的干膜光刻膠技術)也可能有助于在較低的EUV曝光量下降低線邊緣粗糙度。

在先進節點上,需要合適的金屬線材料選擇、關鍵尺寸優化和光刻膠顯影改進來減小線邊緣粗糙度,進而減少由于電子表面散射引起的線電阻升高。未來的節點上可能還需要額外的線邊緣粗糙度改進工藝(光刻后)來減少線邊緣粗糙度引起的電阻。

參考資料:

[1] Chen, H. C., Fan, S. C., Lin, J. H., Cheng, Y. L., Jeng, S. P., Wu, C. M. (2004). The impact of scaling on metal thickness for advanced back end of line interconnects. Thin solid films, 469, 487-490.

[2] van der Veen, M. H., Heyler, N., Pedreira, O. V., Ciofi, I., Decoster, S., Gonzalez, V. V., … T?kei, Z. (2018, June). Damascene benchmark of Ru, Co and Cu in scaled dimensions. In 2018 IEEE International Interconnect Technology Conference (IITC) (pp. 172-174). IEEE.

[3] Techinsights TSMC 5nm logic tear down report.

審核編輯 黃宇

-

半導體

+關注

關注

335文章

28563瀏覽量

232166 -

節點

+關注

關注

0文章

220瀏覽量

24822 -

RMS

+關注

關注

2文章

149瀏覽量

36466

發布評論請先 登錄

大量程粗糙度輪廓儀適用于哪些材質和表面?

大量程粗糙度輪廓儀適用于哪些材質和表面?

優可測白光干涉儀AM系列:量化管控納米級粗糙度,位移傳感器關鍵零件壽命提升50%

先楫半導體MCU具有哪些優勢?

白光干涉儀:表面形貌分析,如何區分波紋度與粗糙度?

砥礪創新 芯耀未來——武漢芯源半導體榮膺21ic電子網2024年度“創新驅動獎”

關于粗糙度輪廓儀一體機的常見提問及回答

粗糙度輪廓儀的測量原理是怎樣的

使用SIDesigner進行銅箔粗糙度建模及仿真分析

測量表面粗糙度:白光共聚焦顯微鏡的優點

如何測曲面粗糙度:一體型輪廓儀提供精確的測量解決方案

粗糙度輪廓儀功能簡介:SJ5800一體型輪廓儀功能亮點

三維輪廓儀測粗糙度:SuperView W光學3D表面輪廓儀功能詳解

表面粗糙度用什么儀器測量?

評論