本文轉(zhuǎn)載自:SK海力士

沉積:“加法工藝”

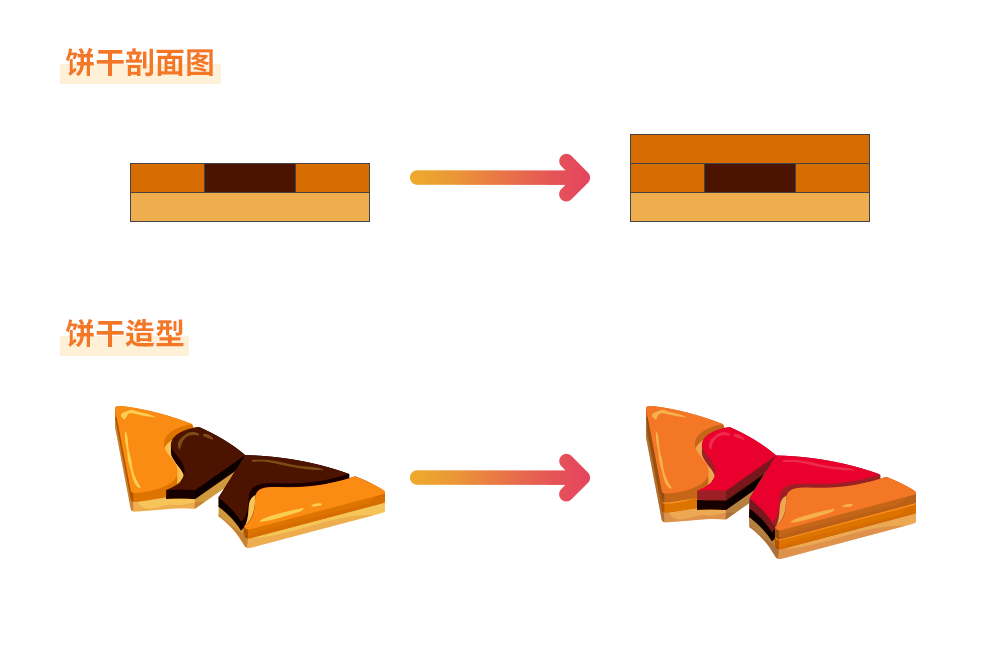

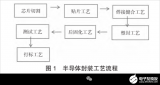

在前幾篇文章,我們一直在借用餅干烘焙過程來形象地說明半導(dǎo)體制程 。在上一篇我們說到,為制作巧克力夾心,需通過“刻蝕工藝”挖出餅干的中間部分,然后倒入巧克力糖漿,再蓋上一層餅干層。“倒入巧克力糖漿”和“蓋上餅干層”的過程在半導(dǎo)體制程中就相當(dāng)于“沉積工藝”。

圖1:倒入巧克力糖漿后,再蓋上一層餅干層

沉積工藝非常直觀:將晶圓基底投入沉積設(shè)備中,待形成充分的薄膜后,清理殘余的部分即可以進(jìn)入下一道工藝了。

在半導(dǎo)體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實(shí)也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨(dú)要強(qiáng)調(diào)“沉積”工藝呢?

這背后的原因,正是半導(dǎo)體的微細(xì)化趨勢(shì)。如今,市場(chǎng)對(duì)電子產(chǎn)品的性能和低電耗的要求越來越高,這就需要更加“微細(xì)”的半導(dǎo)體來做支撐。如果采用體積更小、耗能更低的半導(dǎo)體,就可以在電子產(chǎn)品中添加更多功能。想實(shí)現(xiàn)半導(dǎo)體的微細(xì)化,就需要由不同材料沉積而成的薄膜層,使芯片內(nèi)部不同部分各司其職。金屬層就是其中的一種。過去,半導(dǎo)體制造商曾采用導(dǎo)電性1較高的鋁做芯片的金屬布線。但隨著鋁微細(xì)化技術(shù)遇到瓶頸,制造商就利用導(dǎo)電性更高的銅代替鋁布線。但采用銅就出現(xiàn)了一個(gè)新問題,與鋁不同,銅會(huì)擴(kuò)散到不應(yīng)擴(kuò)散的地方(二氧化硅,SiO2)。為防止銅擴(kuò)散,制造商們就必須在銅布線區(qū)形成阻擋層,即一種高質(zhì)量的薄膜涂層。

1導(dǎo)電性:物體傳導(dǎo)電流的能力;金屬等材料的導(dǎo)電性較高。

半導(dǎo)體核心元件層與布線層厚度只有頭發(fā)的數(shù)千分之一,想堆疊如此微細(xì)的元件和布線層,就需要沉積超薄且厚度極均勻的薄膜。這也是為什么沉積技術(shù)在半導(dǎo)體制程技術(shù)如此重要。本期文章所涉及的“沉積工藝”,又稱為薄膜(Thin film)工藝,希望能為讀者提供參考。

薄膜的分類與作用

“加法工藝”在半導(dǎo)體制程中至關(guān)重要,因?yàn)榘雽?dǎo)體是無法僅憑硅一種材料完成任何操作的:薄膜可以劃分兩個(gè)區(qū)域,使其不互相干擾;或通過互連電線,連接兩個(gè)區(qū)域;必要時(shí),還需要通過特殊的薄膜涂層來加強(qiáng)或減弱電場(chǎng)的力度;還可提前生成薄膜,為下一道工藝做準(zhǔn)備等。接下來我們將詳細(xì)講解一下薄膜的幾種作用。

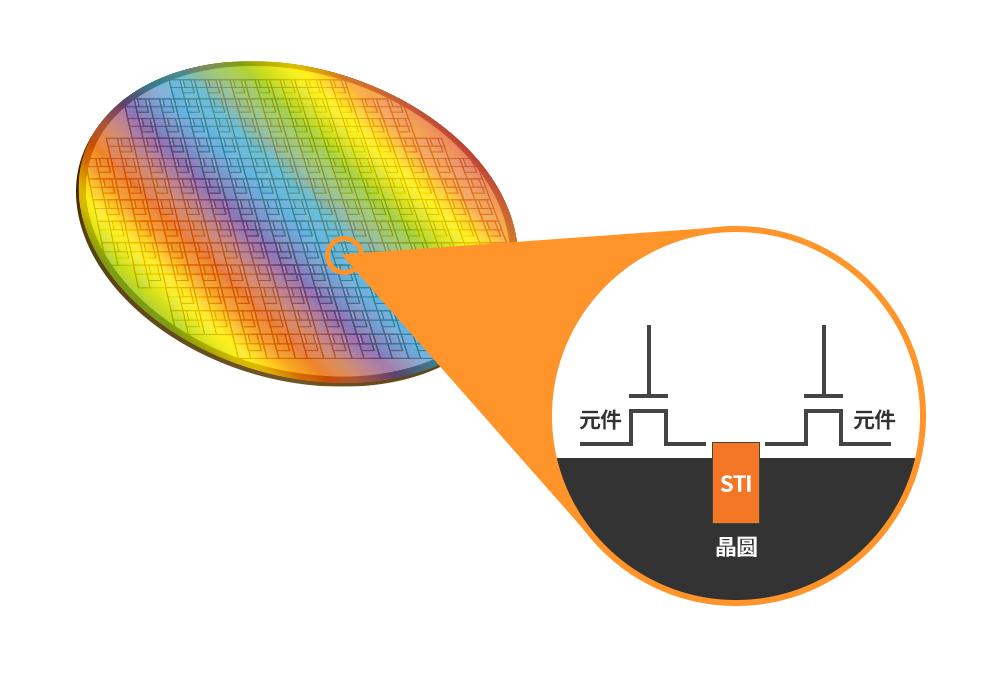

介質(zhì)薄膜是重要的半導(dǎo)體薄膜之一。它可用作電路間的絕緣層,掩蔽半導(dǎo)體核心元件的相互擴(kuò)散和漏電現(xiàn)象,從而進(jìn)一步改善半導(dǎo)體操作性能的可靠性;它還可用作保護(hù)膜,在半導(dǎo)體制程的最后環(huán)節(jié)生成保護(hù)膜,保護(hù)芯片不受外部沖擊;或用作隔離膜,在堆疊一層層元件后進(jìn)行刻蝕時(shí),防止無需移除的部分被刻蝕。淺槽隔離(STI,Shallow Trench Isolation)2和金屬層間電介質(zhì)層(IMD,Intermetal Dieletric)3就是典型的例子。沉積材料主要有二氧化硅(SiO2),碳化硅(SiC)和氮化硅(SiN)等。

2淺槽隔離(STI,Shallow Trench Isolation):在相鄰的元件之間形成陡峭的溝渠,在溝渠中填入氧化物形成元件隔離結(jié)構(gòu),以防止漏電。

3金屬層間電介質(zhì)層(IMD,Intermetal Dieletric):阻止金屬布線層之間不必要電流的流動(dòng)的保護(hù)膜。

圖2:STI在相鄰元件之間形成陡峭溝渠,防止漏電

另外,還有金屬薄膜。芯片底部的元件(晶體管)如果未經(jīng)連接是起不到任何作用的。想要使不同的元件各司其職,必須將它們與其他元件和電源連接起來。元件的連接需要通過鈦、銅或鋁等金屬進(jìn)行布線,連接金屬布線和元件,還需要生成接觸點(diǎn)(Contact)。這就像家電產(chǎn)品中連接電子線路板上的元件與元件時(shí)需焊接電線一樣:連在電子線路板上的電線相當(dāng)于半導(dǎo)體的金屬布線,焊接點(diǎn)就相當(dāng)于半導(dǎo)體內(nèi)的接觸點(diǎn)。

除此之外,沉積工藝在晶體管的高介電性薄膜和用于多重曝光4的硬掩模等方面應(yīng)用范圍也非常廣泛。可以說,沉積在制造工藝中無處不在。不僅如此,過去沒有采用沉積方式的工藝如今也開始采用沉積方式。高介電性薄膜就是其中之一。隨著半導(dǎo)體的微細(xì)化發(fā)展,半導(dǎo)體需要更高質(zhì)量、更精準(zhǔn)的薄膜。因此,過去以氧化工藝制作的高介電性薄膜,如今也開始以沉積方式制作。

4多重曝光(Multi Patterning):通過重復(fù)的曝光和刻蝕工藝,追求更高圖形密度和更小工藝節(jié)點(diǎn)的技術(shù)。

衡量沉積質(zhì)量的主要指標(biāo):均勻度、臺(tái)階覆蓋率、溝槽填充

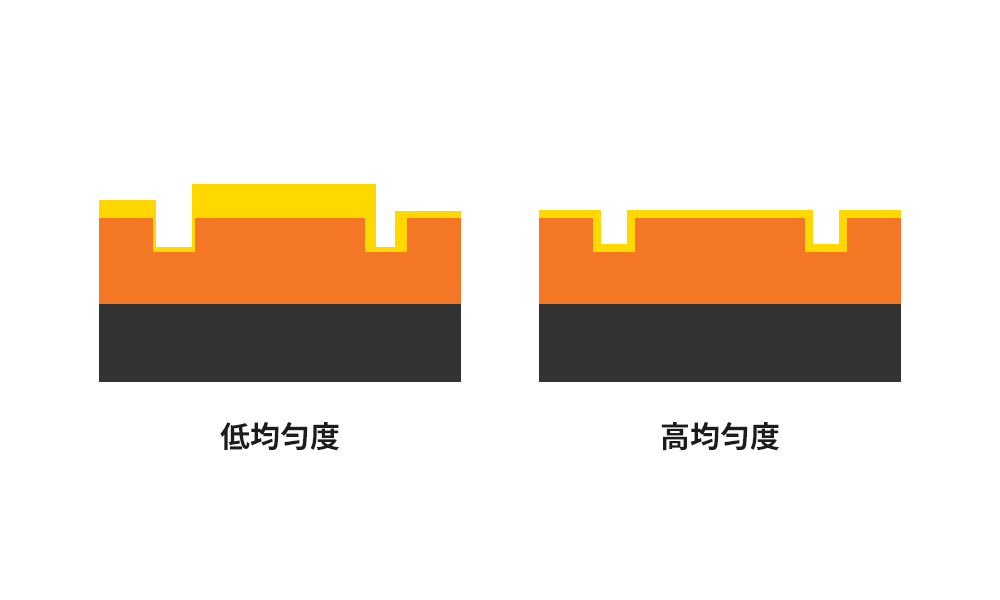

圖3:高均勻度 低均勻度的示例

在講解薄膜沉積方式之前,我們先來了解幾個(gè)衡量沉積質(zhì)量的主要指標(biāo)。這些指標(biāo)與刻蝕工藝有很多相似之處。第一個(gè)指標(biāo)就是均勻度。顧名思義,該指標(biāo)就是衡量沉積薄膜厚度均勻與否的參數(shù)。薄膜沉積和刻蝕工藝一樣,需將整張晶圓放入沉積設(shè)備中。因此,晶圓表面不同角落的沉積涂層有可能厚度不一。高均勻度表明晶圓各區(qū)域形成的薄膜厚度非常均勻。

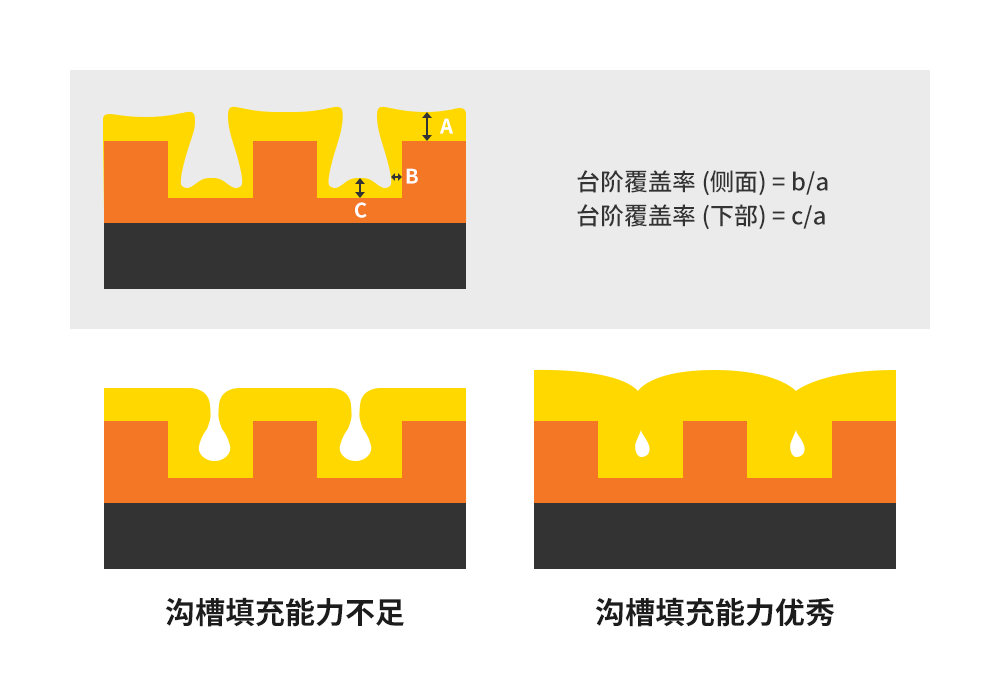

第二個(gè)指標(biāo)為臺(tái)階覆蓋率(StepCoverage)。如果晶圓表面有斷層或凹凸不平的地方,就不可能形成厚度均勻的薄膜。臺(tái)階覆蓋率是考量膜層跨臺(tái)階時(shí),在臺(tái)階處厚度損失的一個(gè)指標(biāo),即跨臺(tái)階處的膜層厚度與平坦處膜層厚度的比值。臺(tái)階覆蓋率越接近1,表明跨臺(tái)階處(底部或側(cè)壁)膜層厚度與平坦處膜層相差越少,越遠(yuǎn)離1(即越小于1)表明跨臺(tái)階處的膜層厚度對(duì)比平坦處膜層厚度越薄。

圖4:臺(tái)階覆蓋率(上圖) 溝槽填充(下圖)示例

最后一個(gè)指標(biāo)是溝槽填充(Gapfill)。溝槽填充是衡量溝槽(Gap)填充程度的一個(gè)參數(shù)。如圖4所示,半導(dǎo)體表面有很多凹凸不平的溝槽,沉積過程中很難保證可以把所有溝槽都填得嚴(yán)嚴(yán)實(shí)實(shí)。溝槽填充能力差,就會(huì)形成孔洞(Void),會(huì)影響材料的致密性,從而影響薄膜強(qiáng)度,造成坍塌。如果說“等向性刻蝕”是沒有方向選擇性地移除了不該移除的部分,沉積工藝中的“溝槽填充能力差”即表明沒有填充到該填充的地方。

沉積方式

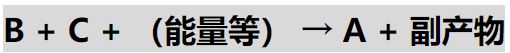

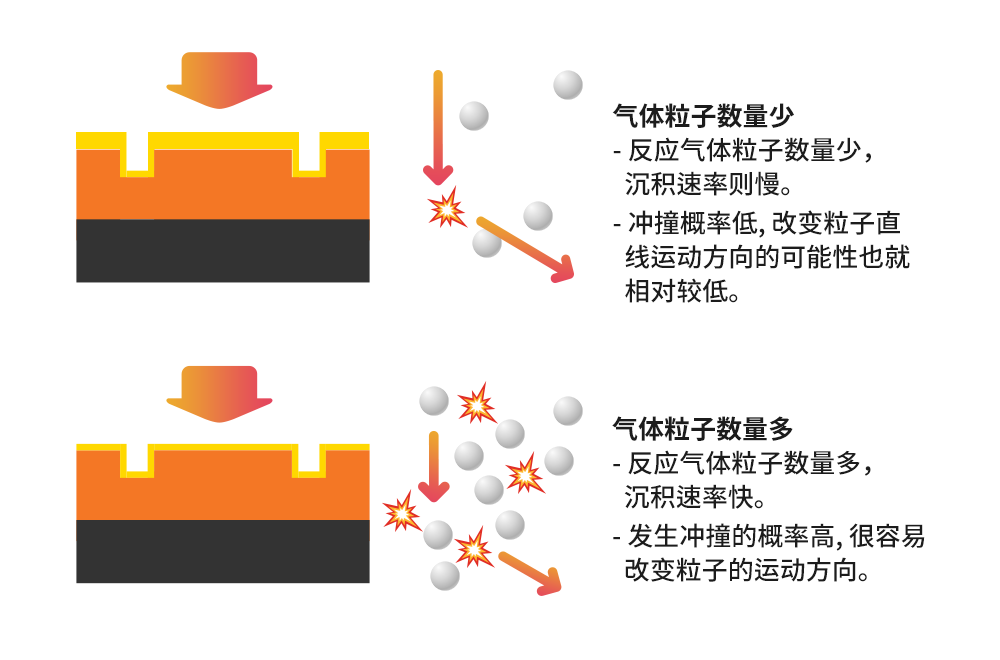

與前面我們所講的工藝相同,沉積工藝也可分為化學(xué)氣相沉積(CVD,Chemical Vapor Deposition)和物理氣相沉積(PVD, Physical Vapor Deposition)。CVD是指通過化學(xué)方法在晶圓表面沉積涂層的方法,一般是通過給混合氣體施加能量來進(jìn)行。假設(shè)想在晶圓表面沉積物質(zhì)(A),則需先向沉積設(shè)備輸入可生成物質(zhì)(A)的兩種氣體(B和C),然后給氣體施加能量,促使氣體B和C發(fā)生化學(xué)反應(yīng)。

化學(xué)方程式如下:

CVD的優(yōu)點(diǎn)是速率快,且由于在晶圓表面發(fā)生化學(xué)反應(yīng),擁有優(yōu)秀的臺(tái)階覆蓋率。但從上述化學(xué)方程式中不難看出,其缺點(diǎn)就是產(chǎn)生副產(chǎn)物廢氣。在半導(dǎo)體制程中,很難將這些廢氣完全排出,難免會(huì)參雜些不純物質(zhì)。因此,CVD多用于不需要精準(zhǔn)把控材料特性的沉積涂層,如沉積各種消耗性的膜層(硬掩模)或各種厚絕緣薄膜等。

圖5:化學(xué)氣相沉積 vs 物理氣相沉積

PVD則向晶圓表面直接轟擊要沉積的材料。也就是說,如果想在晶圓表面沉積A物質(zhì),則需將A物質(zhì)氣化后,使其沉積到晶圓表面。常用的PVD方法有濺射(Sputtering)5,這在刻蝕工藝中也曾涉及過。在這種方法中,我們先向A物質(zhì)靶材(Target)轟擊離子束(主要采用惰性氣體),使A物質(zhì)粒子濺射出來,再將脫落的粒子轉(zhuǎn)移至硅片表面,并形成薄膜。

5濺射(Sputtering):利用高能量轟擊靶材,使其粒子離開其表面的物理過程。

PVD的優(yōu)點(diǎn)是無副產(chǎn)物,沉積薄膜的純度高,且還可以沉積鎢(W)、鈷(Co)等無反應(yīng)能力的純凈物材料。因此,多用于純凈物的金屬布線。

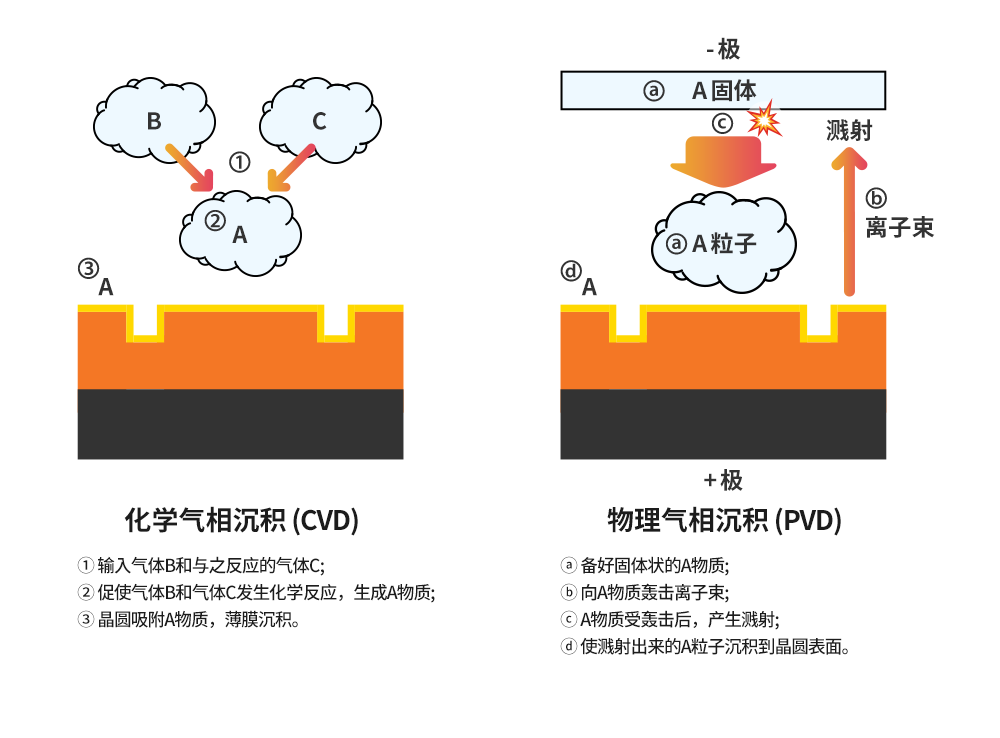

還有一種比較特殊的方法,即原子層沉積(ALD,Atomic Layer Deposition)。前面說到的CVD和PVD兩種方式,要么是通過氣體的化學(xué)反應(yīng)在晶圓表面沉積所需物質(zhì),要么是通過轟擊離子束的物理過程沉積所需物質(zhì)。ALD則與上述兩種方式有所不同。如果想用這種方法在晶圓表面上沉積薄薄的一層A物質(zhì),則要先備好經(jīng)反應(yīng)后可生成A物質(zhì)的反應(yīng)物B和C。反應(yīng)物B必須是容易被晶圓表面吸附的氣體(前驅(qū)體,Precursor),反應(yīng)物C則應(yīng)具有較強(qiáng)的反應(yīng)活性。在ALD過程中,需先把氣體B吸附到晶圓表面,如果氣體B之間很難相互吸附,晶圓表面將形成一層由氣體B組成的原子層。然后,除去剩余氣體B并輸入氣體C,使吸附在晶圓表面上的氣體B和氣體C發(fā)生反應(yīng),形成A物質(zhì)和其他副產(chǎn)物氣體,再除去多余的氣體A和副產(chǎn)物氣體。不斷反復(fù)上述過程,以單原子膜形式一層一層地在基底表面鍍膜。

圖6:傳統(tǒng)CVD vs ALD (摘自:(株)圖書出版HANOL出版社[半導(dǎo)體制造技術(shù)的理解293p])

ALD的最大優(yōu)勢(shì)在于沉積層極均勻的厚度與優(yōu)異的臺(tái)階覆蓋率。氣態(tài)前驅(qū)體可縱橫吸附,且ALD一個(gè)周期只沉積一層原子層。但正是因?yàn)閱卧訉有枰鸫纬练e,沉積速率也就慢了下來。因此,ADL多用于DRAM電容器等縱橫比6高,需要高質(zhì)量膜層的區(qū)域。

6縱橫比:高度與寬度的比值,縱橫比高表示結(jié)構(gòu)物的寬度相對(duì)較窄,高度卻相對(duì)較高。

從上述對(duì)沉積工藝的說明中不難看出,沉積工藝中也存在需權(quán)衡之處:要提高均勻度等精確度,只能犧牲沉積速率。在整個(gè)半導(dǎo)體制程中,精確度和速率似乎永遠(yuǎn)位于蹺蹺板的兩端,需要不斷權(quán)衡。這對(duì)于沉積工藝來說也不例外。

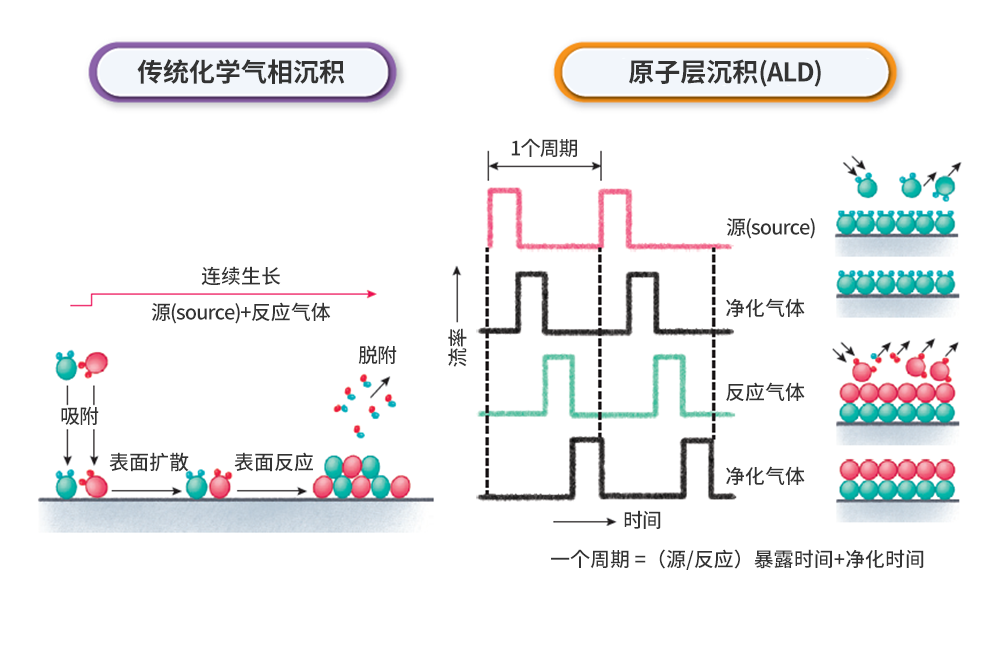

壓力與溫度

和在刻蝕工藝中一樣,半導(dǎo)體制造商在沉積過程中也會(huì)通過控制溫度、壓力等不同條件來把控膜層沉積的質(zhì)量。例如,降低壓強(qiáng),沉積速率就會(huì)放慢,但可以提高垂直方向的沉積質(zhì)量。因?yàn)椋瑝簭?qiáng)低表明設(shè)備內(nèi)反應(yīng)氣體粒子的數(shù)量少,粒子之間發(fā)生沖撞的概率就少,不會(huì)妨礙粒子的直線運(yùn)動(dòng)。施加高溫則可以提高膜層的純度。當(dāng)然,這樣一來就無法使用鋁(其熔點(diǎn)為550度)等熔點(diǎn)低的金屬材料。

圖7:壓強(qiáng)對(duì)沉積工藝的影響

因此,在不同需求下,沉積相同材料也可采用完全不同的沉積方式。例如,同樣是沉積二氧化硅(SiO2),柵極絕緣層與STI所需特性就不同,其沉積的方式也不同。柵極絕緣層是核心元件區(qū)域,要求較高的沉積質(zhì)量,應(yīng)采用高溫低壓的方式;STI則不然,它只要起到兩個(gè)元件間的絕緣作用即可,通過低溫高壓的方式加快沉積速率才是關(guān)鍵。

材料選擇上的難題

您或許常會(huì)在新聞中看到這樣的報(bào)道:“發(fā)現(xiàn)了性能高出XX倍的新材料”。只看新聞內(nèi)容,會(huì)感覺一場(chǎng)翻天覆地的半導(dǎo)體革命似乎即將來臨。但在所謂的“新材料”中,真的能派上用場(chǎng)的卻寥寥無幾。因?yàn)椋牧媳旧淼奶匦院茫⒉淮硭欢苤瞥筛咝阅艿陌雽?dǎo)體。對(duì)沉積材料的要求可不比沉積設(shè)備低。下面,我們來看一看材料的特性會(huì)對(duì)半導(dǎo)體制程產(chǎn)生什么樣的影響。

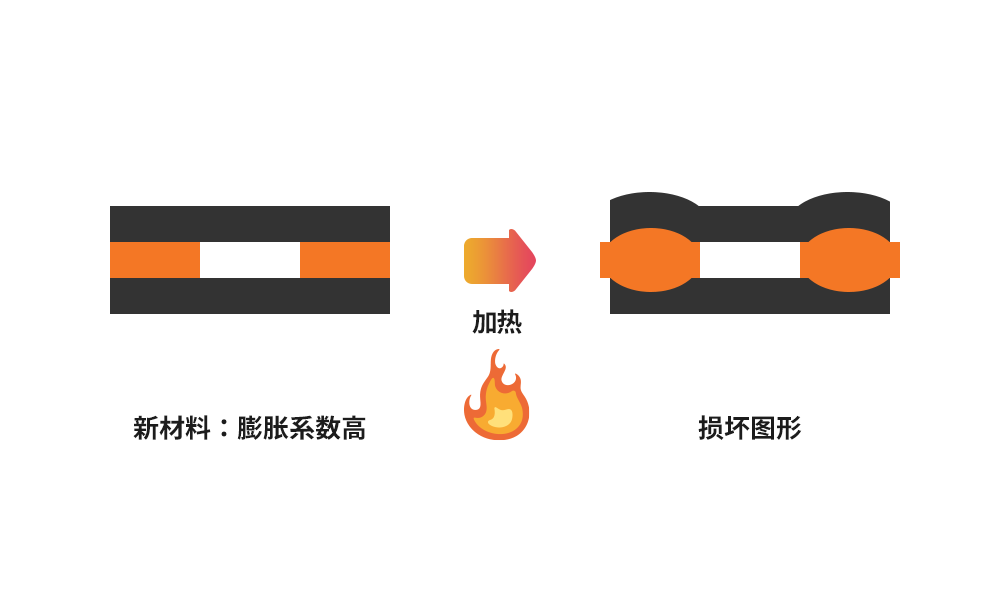

圖8:加熱導(dǎo)致圖形損壞

物體遇熱體積會(huì)變大,這種現(xiàn)象被稱作熱膨脹。鐵軌之間留有縫隙就是為了防止鐵軌在炎熱的夏天因膨脹變形。半導(dǎo)體制程中也會(huì)出現(xiàn)這種熱膨脹現(xiàn)象。問題在于,每一種材料的熱膨脹程度不同,例如鋁的熱膨脹系數(shù)是氧化硅的40倍之多。舉個(gè)比較極端的例子:如果在氧化硅上沉積了鋁薄膜,即便鋁薄膜沉積很成功,一旦進(jìn)入后續(xù)的高溫工藝,其內(nèi)部結(jié)構(gòu)就會(huì)完全被破損。換句話說,如果采用膨脹系數(shù)完全不同的材料替代之前的沉積材料,會(huì)嚴(yán)重影響高溫條件下的產(chǎn)品良率。

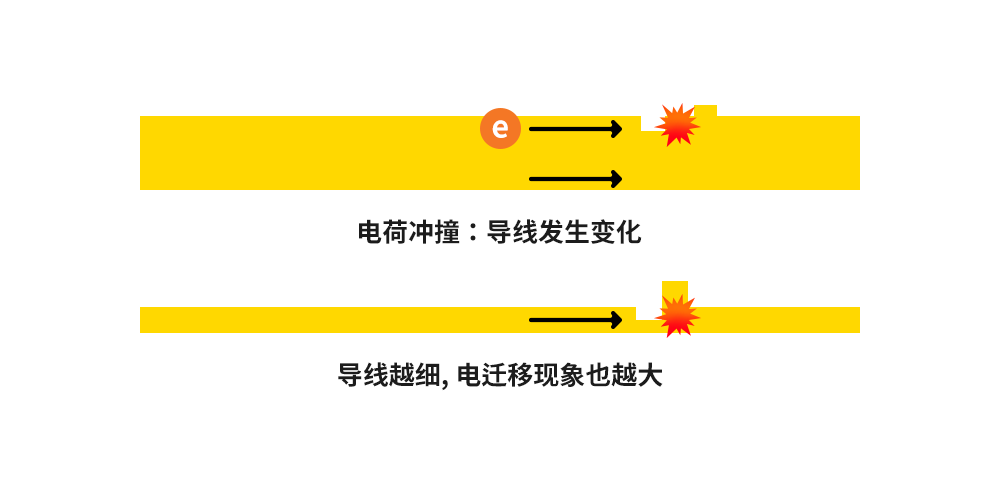

圖9:電遷移現(xiàn)象

除此之外,還要考慮材料的電遷移(EM,Electromigration)現(xiàn)象。電遷移是指在金屬布線上施加電流時(shí),移動(dòng)的電荷撞擊金屬原子,使其發(fā)生遷移的現(xiàn)象。鋁等輕金屬很容易發(fā)生這種電遷移現(xiàn)象。為防止鋁的電遷移現(xiàn)象,半導(dǎo)體制造商們開始用銅布線替代鋁,結(jié)果是又多了一道防止銅擴(kuò)散的阻擋層沉積工藝。隨著半導(dǎo)體不斷微細(xì)化發(fā)展,銅布線也開始出現(xiàn)電遷移現(xiàn)象。為攻克這一難關(guān),英特爾又用鈷布線取代了銅。而既然核心金屬布線層的材料發(fā)生了變化,上下層的工藝也肯定要跟著變。可見,想解決材料的電遷移現(xiàn)象,前后方的工藝也要隨之發(fā)生很大變化。

要始終銘記:半導(dǎo)體制程是數(shù)百個(gè)工藝錯(cuò)綜復(fù)雜緊密連接而成的,牽一發(fā)而動(dòng)全身。新材料是好是壞,不能單看材料本身的特性,還要看能不能與前后方工藝相連,畢竟沉積材料不能獨(dú)立存在。

結(jié)論:一種材料,多種方法

讀到這兒,估計(jì)讀者們已經(jīng)發(fā)現(xiàn)了幾點(diǎn)有趣之處了:首先,同樣的材料可以通過不同的方法制成。例如,二氧化硅(SiO2)可以通過氧化工藝,也可以通過沉積工藝形成。即便是相同的材料,如果通過不同工藝涂敷到半導(dǎo)體上,其物理特性也會(huì)截然不同。

其次,氧化、刻蝕、沉積等看似完全不同的工藝其實(shí)有很多共同之處。比如,物理刻蝕中采用的濺射方法,在沉積工藝中同樣也會(huì)使用,區(qū)別在于“是濺射要刻蝕的晶圓本身”,還是“把濺射出來的粒子沉積到晶圓上”。化學(xué)刻蝕中最重要的一點(diǎn)就是刻蝕氣體與反應(yīng)源生成的廢氣是否易于排放,化學(xué)氣相沉積也同樣如此。CVD過程中生成的副產(chǎn)物也要易于揮發(fā)、易于排放,這樣后續(xù)工藝才會(huì)變得更容易。

可見,受半導(dǎo)體制造商青睞的新材料,并不是其本身特性有多優(yōu)秀的材料,而是其沉積速率、純度等特性易于控制的材料。而且,沉積材料還要易于通過刻蝕或CMP7等工藝去除。如果采用需要過高溫度的材料,可能會(huì)因高溫改變已沉積的其他材料。而若采用對(duì)溫度非常敏感的材料,又會(huì)出現(xiàn)在下一道工藝中無法加熱的問題。

7化學(xué)機(jī)械拋光(CMP,Chemical Mechanical Polishing):通過物理、化學(xué)反應(yīng)研磨, 去除非所需物質(zhì),使半導(dǎo)體晶圓表面變得平坦。

如上文所述,“半導(dǎo)體制程由數(shù)百個(gè)制造工藝緊密連接而成”。想做好每一道工藝,對(duì)其他相關(guān)部門的業(yè)務(wù)也要有很好的把握。要擅于與同事溝通,更要懂得準(zhǔn)確無誤地傳達(dá)自己的想法。一個(gè)半導(dǎo)體產(chǎn)品需要多人合作才可以完成,雖然過程有些辛苦,但也很值得。

※ 本文為外部專家對(duì)半導(dǎo)體/ICT的見解,并不代表SK海力士的立場(chǎng)。

審核編輯 黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27290瀏覽量

218084 -

晶圓

+關(guān)注

關(guān)注

52文章

4890瀏覽量

127931 -

Sti

+關(guān)注

關(guān)注

0文章

9瀏覽量

13092 -

刻蝕

+關(guān)注

關(guān)注

2文章

180瀏覽量

13085

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

意瑞半導(dǎo)體亮相第五屆汽車電驅(qū)動(dòng)及關(guān)鍵技術(shù)大會(huì)

Bumping工藝升級(jí),PVD濺射技術(shù)成關(guān)鍵推手

淺談薄膜沉積

一文詳解半導(dǎo)體薄膜沉積工藝

半導(dǎo)體靶材:推動(dòng)半導(dǎo)體技術(shù)飛躍的核心力量

芯干線科技第五屆國產(chǎn)半導(dǎo)體應(yīng)用技術(shù)大會(huì)精彩回顧

周星工程研發(fā)ALD新技術(shù),引領(lǐng)半導(dǎo)體工藝革新

流量控制器在半導(dǎo)體加工工藝化學(xué)氣相沉積(CVD)的應(yīng)用

半導(dǎo)體發(fā)展的四個(gè)時(shí)代

深圳市薩科微半導(dǎo)體有限公司,技術(shù)骨干來自清華大學(xué)和韓國延世大學(xué)...

半導(dǎo)體發(fā)展的四個(gè)時(shí)代

京東方PCT專利申請(qǐng)量全球第五,展現(xiàn)半導(dǎo)體顯示行業(yè)創(chuàng)新領(lǐng)導(dǎo)力

半導(dǎo)體封裝工藝面臨的挑戰(zhàn)

半導(dǎo)體封裝工藝的研究分析

半導(dǎo)體前端工藝(第五篇):沉積——“更小、更多”,微細(xì)化的關(guān)鍵

半導(dǎo)體前端工藝(第五篇):沉積——“更小、更多”,微細(xì)化的關(guān)鍵

評(píng)論