在電路設計中,DAC時鐘通常是DAC中產生相位噪聲的首要原因。為什么這么說?本文將來做一些探討。

時鐘相位噪聲的產生

時鐘決定何時發送下一樣本,故相位(或時序)中的任何噪聲都會直接影響輸出的相位噪聲。

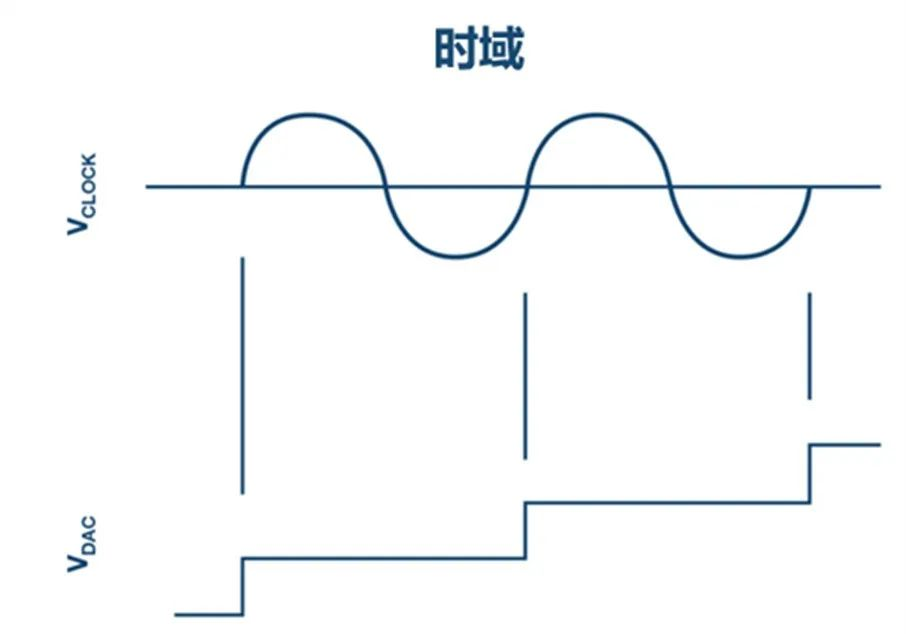

圖 1:時鐘與相位噪聲的相關性

如上圖所示,時鐘對相位噪聲的影響,可以視作各相繼離散值與一個矩形函數相乘,其時序由時鐘定義。

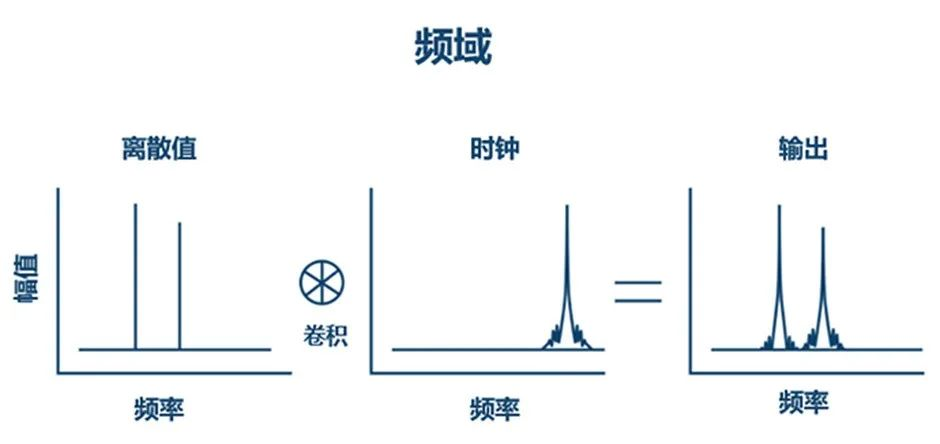

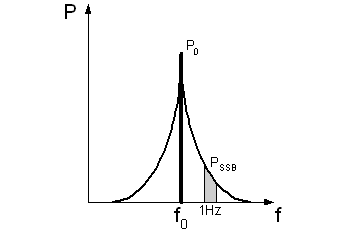

圖 2:相位噪聲卷積

如上圖所示,在頻域中,乘法轉換為卷積運算。結果,期望的頻譜被時鐘相位噪聲所破壞。這就是整個時鐘相位噪聲的產生的過程。

信號頻率與相位噪聲

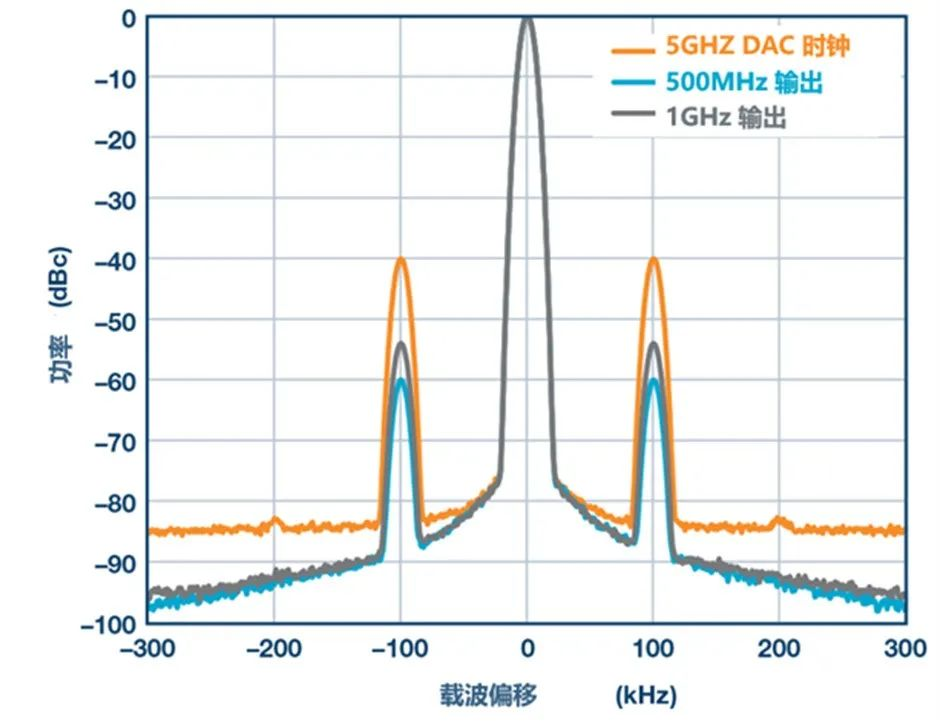

根據信號頻率與時鐘頻率之比,相對于載波的噪聲放大或縮小。信號頻率每降低一半,噪聲改進6dB。為了證明這一點,下圖是不同頻率(5GHz,1GHz,500MHz)下,混入一個帶有輕度100kHz相位偏移的調制時鐘信號(精密受控),來模擬相位噪聲,來看看信號頻率與相位噪聲的關系。

圖 3 :帶100kHz相位調制的時鐘輸出相位噪聲 (圖片來源:ADI)

我們可以看到,從5GHz時鐘到500 MHz DAC輸出觀測到20dB降幅,從500MHz輸出到1GHz輸出觀測到6dB增幅。

時鐘噪聲對于DAC相位噪聲的影響很大。選擇一個高精度的晶振可能是最簡單的方案。

文章來源:得捷電子DigiKey

審核編輯 黃宇

-

電路設計

+關注

關注

6673文章

2451瀏覽量

204167 -

dac

+關注

關注

43文章

2291瀏覽量

190980 -

相位噪聲

+關注

關注

2文章

180瀏覽量

22860

發布評論請先 登錄

相關推薦

數字振蕩器的相位噪聲是多少

鎖相環相位噪聲的影響因素

如何描述相位噪聲的大小 相位噪聲測試和意義

高速DAC相位噪聲從何而來?首要的原因原來是它……

高速DAC相位噪聲從何而來?首要的原因原來是它……

評論