1、同步異常和異步異常的概念

具備以下3個行為的稱之為同步異常:

- The exception is generated as a result of direct execution or attempted execution of an instruction.

- The return address presented to the exception handler is guaranteed to indicate the instruction that caused the exception.

- The exception is precise

其實就是說:

- 異常是由執(zhí)行或嘗試執(zhí)行指令產(chǎn)生的

- 產(chǎn)生異常的那個位置是確定的,即每次執(zhí)行到“那個指令處”就會產(chǎn)生

- 異常是precise的

具備以下3個行為的稱之為異步異常:

- The exception is not generated as a result of direct execution or attempted execution of the instruction stream. The return address presented to the exception handler is not guaranteed to indicate the instruction that caused the exception.

- The exception is imprecise.

其實就是說:

- 異常不是由執(zhí)行或嘗試執(zhí)行指令產(chǎn)生的

- 產(chǎn)生異常的那個位置不是確定的,即不知道執(zhí)行到哪里,就產(chǎn)生了異常

- 異常是imprecise的

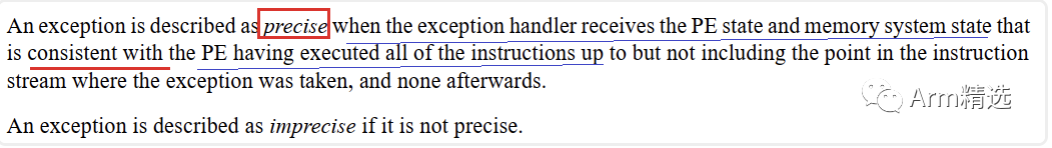

那么precise 和 imprecise 又是什么意思呢??

比較繞、比較難懂,咱們換一個說法:按照預期產(chǎn)生的異常稱之precise,反之imprecise

2、系統(tǒng)中有哪些同步異常?

- 嘗試執(zhí)行UNDEFINED指令產(chǎn)生的任何異常,包括:

(1)、嘗試在不適當?shù)漠惓<墑e執(zhí)行指令。

(2)、當指令被禁用時嘗試執(zhí)行指令。

(3)、嘗試執(zhí)行尚未分配的指令位模式。 - 非法執(zhí)行狀態(tài)異常。這些是由嘗試執(zhí)行指令引起的

PSTATE.IL為 1,(詳細可參考D1-2486 頁上的AArch64 狀態(tài)的非法返回事件) - 使用未對齊的 SP 導致的異常。

- 嘗試使用未對齊的 PC 執(zhí)行指令導致的異常。

- 由異常生成指令SVC、HVC或SMC引起的異常。

- 嘗試執(zhí)行系統(tǒng)寄存器定義為被捕獲到更高的異常級別。(詳細可參考可配置的指令使能和禁止,在D1-2510 頁)

- 由內(nèi)存地址轉換系統(tǒng)生成的指令中止與嘗試相關聯(lián)從產(chǎn)生故障的內(nèi)存區(qū)域執(zhí)行指令。

- 內(nèi)存地址轉換系統(tǒng)生成的數(shù)據(jù)中止與嘗試讀取或寫入產(chǎn)生故障的內(nèi)存。

- 由地址未對齊引起的數(shù)據(jù)中止。

- 如果實施FEAT_MTE2,則由標記檢查故障引起的數(shù)據(jù)中止。。

- 所有調(diào)試異常:(1)、Breakpoint Instruction exceptions. (2)、Breakpoint exceptions. (3)、Watchpoint exceptions. (4)、Vector Catch exceptions. (5)、Software Step exceptions.

- 在支持捕獲浮點異常的實現(xiàn)中,由捕獲的IEEE 浮點異常引起的異常

- 在某些實現(xiàn)中,外部中止。外部中止是失敗的內(nèi)存訪問,包括訪問地址轉換期間發(fā)生的內(nèi)存系統(tǒng)的那些部分。

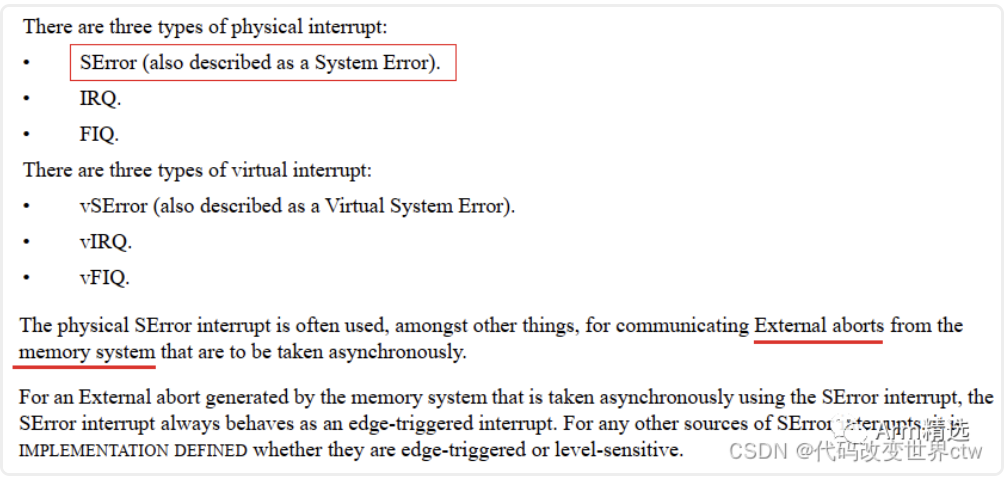

3、Serror的理解

Serror(也稱System Error),是異步異常的一種,一般是來自 Externalaborts, 當memory system訪問時bus上產(chǎn)生的 Externalaborts 。例如

- 訪問內(nèi)存被TZC擋住時,bus會返回的一個異常

注意,像MMU產(chǎn)生的異常,它屬于 internalabort,它是同步異常。像未定義指令異常,它也是同步異常

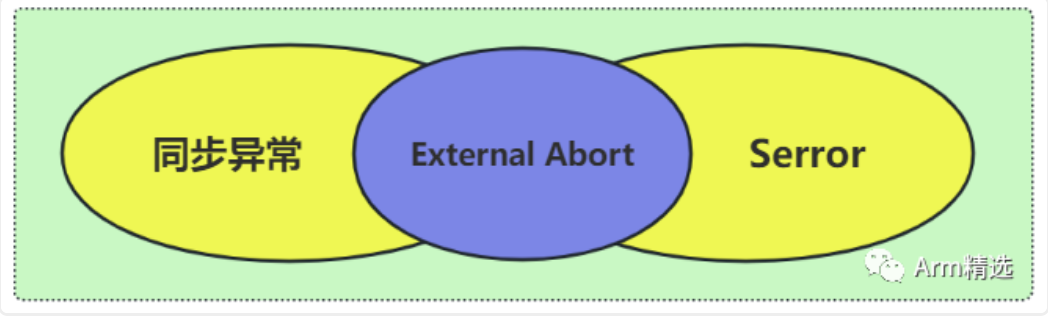

4、External abort的理解

External Abort,可以同步異常,也可以是Serror

例如:

- Instruction Abort 可能是內(nèi)部同步異常,也可能是同步External Abort

- Data Abort 可能是內(nèi)部同步異常,也可能是同步External Abort (即 External abort 可以屬于同步異常哦)

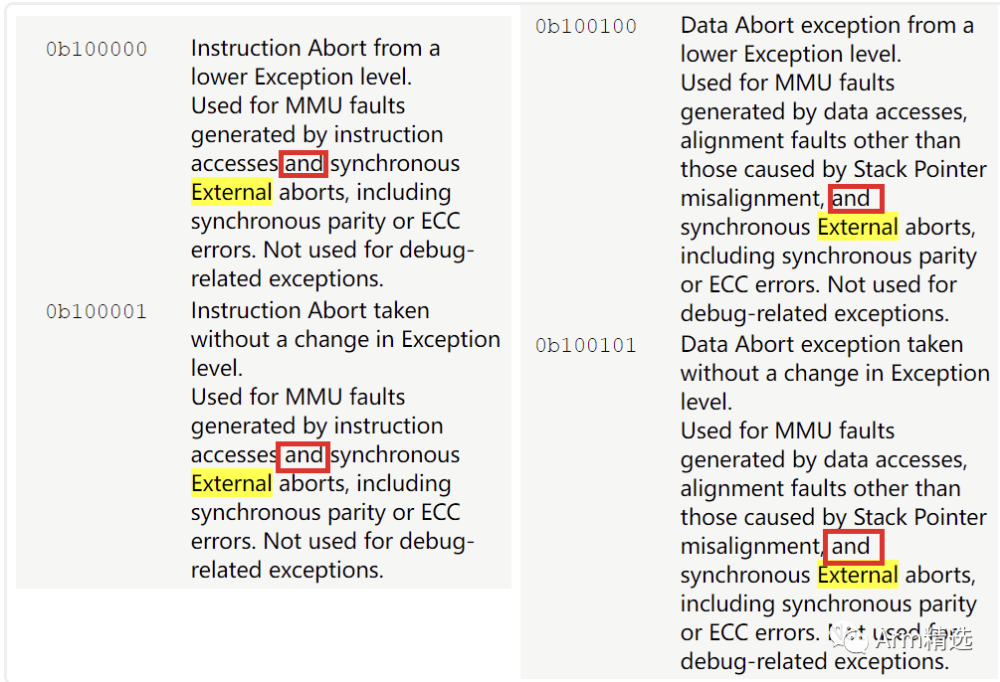

4、instruction abort、data abort

在aarch64架構中,instruction abort、data abort已然變成了同步異常中的一種。不再是單獨的異常模型了。所以當出現(xiàn)instruction abort、data abort時,那么一定是同步異常,可能是internal abort,也可能是external abort,但終歸是同步異常。

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

SMC

+關注

關注

2文章

85瀏覽量

20273 -

SVC

+關注

關注

0文章

33瀏覽量

12128 -

MMU

+關注

關注

0文章

91瀏覽量

18283 -

ARMv8

+關注

關注

1文章

35瀏覽量

14158

發(fā)布評論請先 登錄

相關推薦

一文幫你梳理Cortex與ARMv8等基礎概念

ARMv8架構資料分享

ARMv8架構的兩種執(zhí)行狀態(tài)分別是什么

探討一下ARMv8的AArch32 PE模式

ARMv8架構概述

Armv8.1-M PAC和BTI擴展簡析

ARMv8 architecture里的Memory aborts簡析

ARM推新品:ARMv8首次支援64位元指令集

TRACE32支持ARMv8架構

Armv8架構及虛擬化介紹

ARMv8工作模式有哪些

armv8 u-boot的啟動介紹

Armv8的同步異常、External abort等區(qū)別簡析

Armv8的同步異常、External abort等區(qū)別簡析

評論