眾所周知,芯片是現(xiàn)代科技的核心關(guān)鍵和技術(shù)底座。

而EDA作為集成電路產(chǎn)業(yè)鏈上游的關(guān)鍵環(huán)節(jié),是設(shè)計(jì)大規(guī)模集成電路必備的工具,堪稱“芯片之母”,也是一個公認(rèn)市場規(guī)模本身不大,但卻能撬動半導(dǎo)體產(chǎn)業(yè)鏈的關(guān)鍵“杠桿”。

近年來,隨著全球芯片市場的動蕩和變革,強(qiáng)韌、高效和創(chuàng)新的EDA生態(tài)建設(shè)成為了業(yè)界迫切的需求。

在此背景和趨勢下,在11月10日舉行的ICCAD 2023高峰論壇上,上海思爾芯技術(shù)股份有限公司(下文簡稱“思爾芯”)副總裁陳英仁帶來了**《共贏 EDA新生態(tài):全方位解決方案與多元合作》**的主題演講,圍繞數(shù)字EDA的產(chǎn)業(yè)破局、技術(shù)創(chuàng)新,以及如何鑄造國產(chǎn)EDA新生態(tài)等話題進(jìn)行了精彩分享,同時也重點(diǎn)展示了思爾芯在數(shù)字EDA領(lǐng)域的全面解決方案。

陳英仁表示,盡管面對國際巨頭的市場競爭和圍追堵截,面對技術(shù)積累、人才儲備、生態(tài)缺失的諸多短板,但本土EDA廠商近年來在政策和資本的大力扶持、產(chǎn)業(yè)鏈伙伴協(xié)同合作,以及行業(yè)人才不斷取得突破的趨勢下,如雨后春筍般爆發(fā),迎難而上。

他強(qiáng)調(diào),“在EDA新生態(tài)中,除了追求經(jīng)濟(jì)回報外,更要注重與合作伙伴建立基于‘利+義’”的深度合作關(guān)系,共同推動行業(yè)的繁榮與進(jìn)步。”

所謂利,即對利益的追求,EDA技術(shù)的革新一方面可以給資本帶來利益回報,另一方面可以幫助客戶提高設(shè)計(jì)效率,降低成本,增強(qiáng)競爭力,為客戶帶來經(jīng)濟(jì)效益;義,則是對雙贏的新定義,EDA企業(yè)與合作伙伴不僅僅是經(jīng)濟(jì)利益,更重要的是合作與責(zé)任的共同承擔(dān)。

不難理解,EDA與國產(chǎn)技術(shù)同行,秉承“利+義”的原則,打造有溫度的合作關(guān)系,才是共筑EDA產(chǎn)業(yè)新生態(tài)的基礎(chǔ)。

新技術(shù)浪潮推動EDA創(chuàng)新與變革

當(dāng)前,除了本土EDA廠商和行業(yè)伙伴自身努力謀發(fā)展之外,芯片領(lǐng)域新興技術(shù)層出不窮,新興架構(gòu)、標(biāo)準(zhǔn)、需求和理念也在不斷推動行業(yè)進(jìn)步。當(dāng)下RISC-V、Chiplet和AI技術(shù)成為行業(yè)高頻詞,其發(fā)展和成熟給EDA廠商帶來了新挑戰(zhàn)和新機(jī)遇。

陳英仁表示,面對RISC-V、AI、Chiplet等技術(shù)的快速發(fā)展,EDA技術(shù)必須進(jìn)行創(chuàng)新和變革,以滿足新的設(shè)計(jì)和實(shí)現(xiàn)需求。

RISC-V為設(shè)計(jì)帶來更多可能性

首先來看RISC-V,RISC-V架構(gòu)從設(shè)計(jì)理念上摒棄了“歷史包袱”,具有精簡、低功耗、模塊化、可擴(kuò)展、開放開源等技術(shù)優(yōu)勢,旨在為芯片設(shè)計(jì)帶來更多可能性。

尤其是在物聯(lián)網(wǎng)(IoT)領(lǐng)域,開源架構(gòu)RISC-V的出現(xiàn),進(jìn)一步點(diǎn)燃了新晉者的熱情。

在逐漸走向成熟的IoT行業(yè)中,RISC-V以其極具多樣性、低功耗、高安全性和成本效益的優(yōu)勢,展現(xiàn)出巨大的潛力。更重要的是,其開源和高度可定制的特性賦予了芯片設(shè)計(jì)企業(yè)更大的自主權(quán),從而滿足了多樣化的客戶需求。

根據(jù)RISC-V基金會數(shù)據(jù),2022年采用RISC-V架構(gòu)的處理器核已出貨100億顆,其中絕大多數(shù)出貨都集中在MCU和IoT領(lǐng)域。預(yù)計(jì)到2025年,RISC-V架構(gòu)的處理器核出貨量將突破800億顆。在出貨量暴增的同時,RISC-V應(yīng)用場景不再局限于低功耗物聯(lián)網(wǎng)領(lǐng)域,而是逐漸向手機(jī)、電腦、汽車、數(shù)據(jù)中心等應(yīng)用領(lǐng)域拓展。

不僅如此,RISC-V作為一種開放指令集架構(gòu),也為中國芯片產(chǎn)業(yè)提供了一個新的選擇和機(jī)會。隨著國際貿(mào)易沖突和“逆全球化”加劇,國內(nèi)開始加速擁抱開源RISC-V架構(gòu)發(fā)展,以避免在主流CPU芯片架構(gòu)上受制于人,實(shí)現(xiàn)更多的自主創(chuàng)新和供應(yīng)鏈安全。

去年出貨量超100億顆的RISC-V架構(gòu)芯片,國內(nèi)出貨量已經(jīng)占據(jù)一半,不僅有眾多國內(nèi)企業(yè)和科研機(jī)構(gòu)加入了RISC-V國際基金會,還成立了中國開放指令生態(tài)聯(lián)盟和國內(nèi)首個RISC-V專利聯(lián)盟,致力于推動中國RISC-V芯片生態(tài)建設(shè)。

RISC-V技術(shù)正憑借其開放性、高效性和卓越的可擴(kuò)展性,重新定義計(jì)算的未來。不過,任何技術(shù)的發(fā)展都存在兩面性,RISC-V在提供自主供應(yīng)鏈機(jī)會,加速技術(shù)迭代的同時,其開放協(xié)作模式也帶來了諸多挑戰(zhàn)。

RISC-V的劣勢在于其還處于發(fā)展初期,還沒有形成一個完善而統(tǒng)一的技術(shù)體系和商業(yè)模式。陳英仁指出,在標(biāo)準(zhǔn)細(xì)節(jié)定義、碎片化&穩(wěn)定性以及EDA支持方面,RISC-V還存在不足,為芯片設(shè)計(jì)帶來挑戰(zhàn)。

隨著RISC-V技術(shù)深入各領(lǐng)域,它以開源、簡潔和高度可擴(kuò)展的特性正逐步塑造未來。盡管RISC-V潛力巨大,其生態(tài)系統(tǒng)仍存在待完善之處。特別是其獨(dú)立、靈活和彈性的設(shè)計(jì)理念讓系統(tǒng)碎片化的問題劇增。

EDA的任務(wù)就是傾聽客戶需求,來滿足他們在不同應(yīng)用對產(chǎn)品設(shè)計(jì)或生態(tài)系統(tǒng)的支持。

為了應(yīng)對這些挑戰(zhàn),思爾芯為RISC-V提供了涵蓋微架構(gòu)分析、系統(tǒng)整合、規(guī)范符合性測試以及軟件性能評估的一系列優(yōu)化解決方案。通過思爾芯的“芯神匠”的系統(tǒng)&應(yīng)用性能分析、“芯神瞳”的評估架構(gòu)配置/軟件性能分析、“芯神鼎”的規(guī)范符合性測試等策略,構(gòu)建一個更高效和穩(wěn)定的RISC-V平臺。

據(jù)悉,思爾芯還在助力北京開源芯片研究院“香山”項(xiàng)目的不斷演進(jìn)。

“香山”高性能RISC-V處理器是一個由中國科學(xué)院計(jì)算技術(shù)研究所孕育出的開源項(xiàng)目,從“香山”的第一代到目前的第三代,其背后的技術(shù)支撐與演進(jìn)都離不開思爾芯的助力,開芯院都采用了思爾芯的“芯神瞳”原型驗(yàn)證解決方案,加速其技術(shù)的演進(jìn)與應(yīng)用落地。

在集成電路和微處理器設(shè)計(jì)中,原型驗(yàn)證是不可或缺的一環(huán),它涉及到在真實(shí)硬件上驗(yàn)證設(shè)計(jì)的功能、性能和可靠性。思爾芯為“香山”提供了一個針對性的解決方案——芯神瞳VU19P原型驗(yàn)證系統(tǒng),使“香山”能夠高效地完成SPEC跑分驗(yàn)證、IO驗(yàn)證以及BSP驅(qū)動的開發(fā)等工作,涵蓋了從硬件設(shè)計(jì)到軟件集成的整個生命周期的不同方面。

Chiplet技術(shù):未來算力芯片的解決方案

RISC-V之外,當(dāng)下Chiplet技術(shù)的發(fā)展也給本土EDA廠商帶來“換道超車”的新機(jī)遇。

Chiplet又稱“小芯片”或“芯粒”,通過將不同工藝節(jié)點(diǎn)和不同材質(zhì)的芯片通過先進(jìn)封裝技術(shù)集成在一起,形成一個系統(tǒng)芯片,實(shí)現(xiàn)了一種新形式的IP復(fù)用。

在芯片產(chǎn)業(yè),由于Chiplet能夠緩解性能、功耗和成本的限制,大幅度降低對最先進(jìn)工藝的要求和成本負(fù)擔(dān),這一技術(shù)方向受到行業(yè)追捧,AMD、英特爾等公司已采用Chiplet方案設(shè)計(jì)芯片,此方案也被稱為“異構(gòu)集成”。

與RISC-V技術(shù)類似,Chiplet新趨勢背后也面臨新挑戰(zhàn)。

陳英仁表示,Chiplet趨勢下,更多異構(gòu)芯片和各類總線的加入,整個過程將會變得更加復(fù)雜,對EDA工具也提出了新要求。一方面,芯片的設(shè)計(jì)必須適應(yīng)不同IP、不同Chiplet組合的復(fù)雜產(chǎn)品形態(tài),異構(gòu)集成系統(tǒng)中接口與標(biāo)準(zhǔn)的統(tǒng)一性,設(shè)計(jì)者需在異構(gòu)芯片的性能與靈活性之間找到平衡;另一方面,Chiplet正重塑半導(dǎo)體產(chǎn)業(yè)鏈, 推動新的EDA工具鏈,以及IP、設(shè)計(jì)、后端封裝/生產(chǎn)等新的上下游生態(tài)結(jié)合,催生新的商業(yè)模式。

針對此類需求,EDA業(yè)內(nèi)提出了混合異構(gòu)驗(yàn)證方法,成熟的Chiplet,RTL-Ready IP,System Modeling IP可以在一個系統(tǒng)中同時建模驗(yàn)證,并發(fā)揮Chiplet、RTL-Ready IP的高速優(yōu)勢,也支持System Modeling IP的靈活配置功能。

據(jù)悉,對于異構(gòu)芯片設(shè)計(jì)驗(yàn)證的需求,思爾芯也提出了基于驗(yàn)證云系統(tǒng)的統(tǒng)一驗(yàn)證平臺,平臺融合架構(gòu)設(shè)計(jì)、原型驗(yàn)證等不同解決方案,以期實(shí)現(xiàn)高效快速驗(yàn)證。

AI + EDA:適應(yīng)存儲和算力爆炸性增長的挑戰(zhàn)

此外,在ChatGPT引領(lǐng)的新一代生成式AI浪潮下,隨著AI應(yīng)用的持續(xù)增長,為芯片和EDA生態(tài)帶來新機(jī)遇的同時,也引發(fā)了對算力基礎(chǔ)設(shè)施的需求飆升,而作為算力基礎(chǔ)的高性能芯片,存儲與算力的爆發(fā)式增長對SoC設(shè)計(jì)和驗(yàn)證施加了巨大壓力。

陳英仁表示,AI技術(shù)的發(fā)展不僅加速了更復(fù)雜的計(jì)算需求、更強(qiáng)的功能性和更快的數(shù)據(jù)傳輸速度,同時也為芯片研發(fā)人員帶來了前所未有的挑戰(zhàn),傳統(tǒng)的芯片設(shè)計(jì)方法已經(jīng)不能適應(yīng)當(dāng)前的市場需求;此外,AI引擎一改傳統(tǒng)的馮諾·依曼架構(gòu),在新的框架需求下,探索應(yīng)用驅(qū)動算法、算法驅(qū)動軟件,以及軟硬件架構(gòu)靈活協(xié)同設(shè)計(jì),引領(lǐng)芯片設(shè)計(jì)的下一場革新,芯片設(shè)計(jì)行業(yè)迫切需要EDA的創(chuàng)新來應(yīng)對AI時代的新變革。

尤為值得關(guān)注的是,在集成電路規(guī)模越發(fā)龐大的現(xiàn)實(shí)情況下,從設(shè)計(jì)到流片的全流程中,驗(yàn)證變得尤為重要。因?yàn)橛行У尿?yàn)證不僅能確保電路設(shè)計(jì)層面的完善,還保證了其在實(shí)際應(yīng)用中的穩(wěn)定運(yùn)行,從而降低修正和調(diào)整的成本和時間。

為了應(yīng)對這一挑戰(zhàn)并縮短驗(yàn)證周期,硬件仿真成為了超大規(guī)模集成電路驗(yàn)證的關(guān)鍵工具。同時,AI算力的飛速增長不僅促進(jìn)了EDA工具的快速演進(jìn),還與EDA工具結(jié)合,催生了一種“雙向加速”的良性循環(huán)。

對此,思爾芯推出了首款國產(chǎn)企業(yè)級硬件仿真系統(tǒng)——芯神鼎OmniArk,該硬件仿真系統(tǒng)采用了由AI驅(qū)動的智能編譯引擎,能夠在編譯流程中極大地減少編譯時間和內(nèi)存占用,實(shí)現(xiàn)增量編譯,并能智能匹配P&R策略,從而顯著提高布線的成功率。

芯神鼎將AI應(yīng)用于編譯流程,推動了芯片設(shè)計(jì)領(lǐng)域的發(fā)展,開啟了EDA驗(yàn)證新時代。

此外,思爾芯的芯神瞳邏輯系統(tǒng)和邏輯模塊產(chǎn)品也是目前市場上頗具競爭力的原型驗(yàn)證解決方案,其高性價比獲得了市場的青睞。前不久,思爾芯發(fā)布了最新一代原型驗(yàn)證解決方案——芯神瞳邏輯系統(tǒng)S8-40,也為當(dāng)前如AI、GPU芯片等大存儲和大數(shù)據(jù)設(shè)計(jì)提供了有效的解決方案。

思爾芯,20年持續(xù)打造數(shù)字EDA全流程

整體來看,面對RISC-V、Chiplet、AI等技術(shù)的快速進(jìn)展,EDA技術(shù)必須進(jìn)行創(chuàng)新和變革,以滿足新的設(shè)計(jì)和實(shí)現(xiàn)需求。

在新技術(shù)引領(lǐng)的行業(yè)契機(jī)和挑戰(zhàn)下,思爾芯致力于通過新技術(shù)的布局、前瞻性的探索,圍繞應(yīng)用創(chuàng)新、軟硬交互和系統(tǒng)工程等多方面打造創(chuàng)新的生意模式,為客戶創(chuàng)造更大價值。

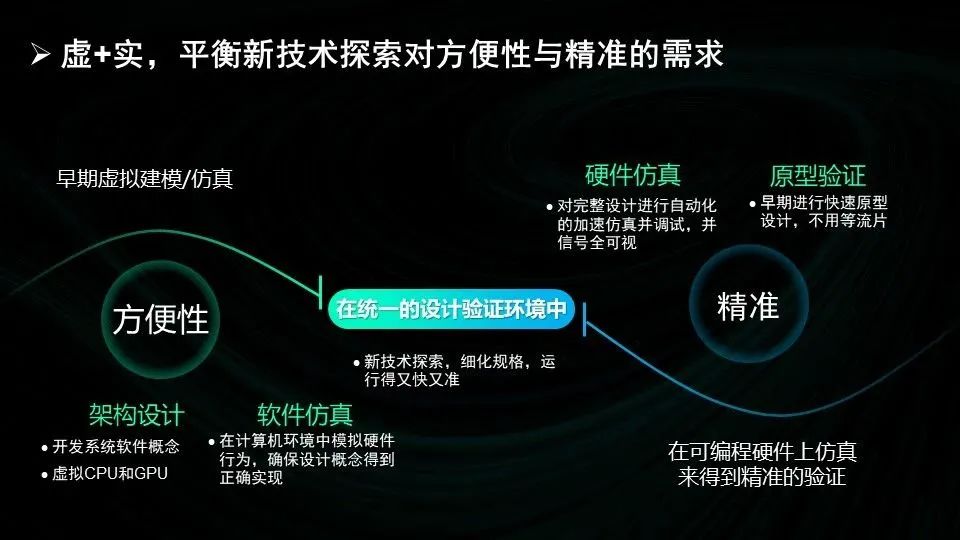

陳英仁介紹道,面臨上述新技術(shù)對方便性與精準(zhǔn)性的需求,思爾芯的工具作為載體和平臺,可以對新技術(shù)做虛和實(shí)的架構(gòu)探索,結(jié)合不同EDA廠商、IP廠商、后端制造等產(chǎn)業(yè)鏈伙伴,一起為客戶提供更有效的方案。

據(jù)了解,思爾芯于2004年在上海成立。近20年來,思爾芯持續(xù)發(fā)揮EDA技術(shù)優(yōu)勢,致力于為眾多的IC設(shè)計(jì)企業(yè)提供全方位、全流程和全覆蓋的產(chǎn)品組合。陳英仁表示,思爾芯專注于芯片數(shù)字前端領(lǐng)域,推出了一系列優(yōu)質(zhì)的數(shù)字EDA工具,如架構(gòu)設(shè)計(jì)工具“芯神匠”、軟件仿真工具“芯神馳”、硬件仿真工具“芯神鼎”、原型驗(yàn)證工具“芯神瞳”,以及提供全面的EDA云服務(wù),確保芯片設(shè)計(jì)流程能夠完整、準(zhǔn)確地實(shí)現(xiàn)對需求規(guī)格的響應(yīng),從而加快芯片產(chǎn)品的開發(fā)進(jìn)程。

當(dāng)前,EDA逐步上云已成趨勢。思爾芯是國內(nèi)首家通過自主研發(fā)推出原型驗(yàn)證云服務(wù)的EDA企業(yè)。

在ICCAD論壇上,中國半導(dǎo)體行業(yè)協(xié)會集成電路設(shè)計(jì)分會理事長魏少軍教授表示,2023年中國大陸有3451家芯片設(shè)計(jì)企業(yè),比去年增加了208家。但這3451家芯片設(shè)計(jì)企業(yè)廣泛分布在消費(fèi)電子、工業(yè)、汽車、數(shù)據(jù)中心等多個行業(yè)。這些企業(yè)大多為中小微企業(yè),且大多面臨人手短缺,設(shè)計(jì)能力匱乏等問題,尤其是設(shè)計(jì)團(tuán)隊(duì)在進(jìn)行仿真和驗(yàn)證時,往往缺乏大規(guī)模的算力集群支持。

對于AI和HPC這類對芯片設(shè)計(jì)要求更高的應(yīng)用來說,不僅對開發(fā)團(tuán)隊(duì)的創(chuàng)新提出了要求,也對其硬件計(jì)算資源提出了更高的要求,所以軟件上云被提了出來。可以持續(xù)擴(kuò)張的算力資源,為設(shè)計(jì)與驗(yàn)證提供了便利,大大降低了芯片設(shè)計(jì)自動化的效率,也降低了基礎(chǔ)設(shè)施的添置和管理成本。

在這一趨勢下,EDA廠商們紛紛開啟了自己的上云之路,發(fā)展云端EDA業(yè)務(wù)。

思爾芯重磅發(fā)布自研數(shù)字電路調(diào)試軟件“芯神覺”

與此同時,在ICCAD 2023上,思爾芯正式發(fā)布一款自主研發(fā)的數(shù)字電路調(diào)試軟件——“芯神覺”,這款全新的工具集成了源代碼追蹤、波形圖調(diào)試、原理圖萃取和覆蓋率分析等核心功能,旨在為工程師提供一個全面、高效的分析與調(diào)試平臺。利用先進(jìn)的調(diào)試技術(shù)幫助開發(fā)者簡化整個調(diào)試過程,加速芯片開發(fā)。

“芯神覺”在與思爾芯的其他產(chǎn)品如軟件仿真、硬件仿真以及原型驗(yàn)證等工具靈活銜接,實(shí)現(xiàn)深度融合后,可以為芯片工程師打造一個既統(tǒng)一又高效的設(shè)計(jì)環(huán)境。這不僅極大地簡化了繁復(fù)的調(diào)試工作,而且使得整個調(diào)試流程變得更加流暢和高效,顯著提升了復(fù)雜芯片設(shè)計(jì)驗(yàn)證的效率。

思爾芯在EDA領(lǐng)域的技術(shù)實(shí)力受到了業(yè)界的廣泛認(rèn)可,通過多年耕耘,已在數(shù)字前端EDA領(lǐng)域構(gòu)筑了技術(shù)與市場的雙優(yōu)勢地位,已與超過600家國內(nèi)外企業(yè)建立了良好的合作關(guān)系。并參與了我國 EDA 團(tuán)體標(biāo)準(zhǔn)的制定,承擔(dān)了多項(xiàng)國家及地方重大科研項(xiàng)目,獲國家級專精特新“小巨人”企業(yè)、國家工業(yè)軟件優(yōu)秀產(chǎn)品、上海市級企業(yè)技術(shù)中心等多項(xiàng)榮譽(yù)資質(zhì)。

隨著本次“芯神覺”新品的推出,將進(jìn)一步增強(qiáng)思爾芯數(shù)字前端EDA解決方案,為芯片設(shè)計(jì)企業(yè)提供了一個更全面的產(chǎn)品和服務(wù)組合。

寫在最后

作為芯片設(shè)計(jì)領(lǐng)域的“基座技術(shù)”,在RISC-V、Chiplet、AI等新技術(shù)趨勢推動下,EDA的全流程創(chuàng)新將撬動芯片產(chǎn)業(yè)的巨大變革。

同時,中國作為全球規(guī)模最大、增速最快的集成電路市場,在復(fù)雜的國際貿(mào)易關(guān)系和“國產(chǎn)替代”的時代浪潮下,國產(chǎn)EDA迎來巨大的發(fā)展空間和市場潛力。

諸多機(jī)會促進(jìn)發(fā)展,國內(nèi)EDA未來可期。

在這個過程中,以思爾芯為代表的國產(chǎn)EDA企業(yè),正著力EDA產(chǎn)業(yè)的破局之路,力圖鑄造國產(chǎn)EDA新生態(tài)。

審核編輯:劉清

-

集成電路

+關(guān)注

關(guān)注

5391文章

11617瀏覽量

362810 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27687瀏覽量

221431 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2912文章

44912瀏覽量

375877 -

eda

+關(guān)注

關(guān)注

71文章

2785瀏覽量

173612 -

RISC-V

+關(guān)注

關(guān)注

45文章

2322瀏覽量

46384

原文標(biāo)題:ICCAD 2023|新技術(shù)浪潮與變革下,國產(chǎn)EDA如何破局?

文章出處:【微信號:S2C_Corporation,微信公眾號:思爾芯S2C】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AI、Chiplet EDA需求強(qiáng)勁!國產(chǎn)EDA跑步進(jìn)入,突破3%市場份額有大招

國產(chǎn)汽車芯片現(xiàn)狀解讀:高端少、占比低,該如何破局?

廣立微攜EDA產(chǎn)品與創(chuàng)新技術(shù)亮相ICCAD 2024

探討大模型時代背景下數(shù)據(jù)存儲的變革之道

開啟數(shù)字化時代的智能園區(qū):破局之道

可驗(yàn)證AI開啟EDA新時代,引領(lǐng)半導(dǎo)體產(chǎn)業(yè)變革

合見工軟發(fā)布多款國產(chǎn)自研EDA與IP解決方案

概倫電子引領(lǐng)國產(chǎn)EDA產(chǎn)業(yè)升級

國產(chǎn)芯片原廠的出路:從風(fēng)潮到現(xiàn)實(shí)的破局之路

國產(chǎn)FPGA的發(fā)展前景是什么?

【試用評選】為昕原理圖設(shè)計(jì)EDA軟件(Jupiter)試用活動評選結(jié)果公布

華大九天收購阿卡思近50%股權(quán),國產(chǎn)EDA產(chǎn)業(yè)格局生變

攜手華為鯤鵬 芯華章助力打造國產(chǎn)EDA平臺

新技術(shù)浪潮與變革下,國產(chǎn)EDA如何破局?

新技術(shù)浪潮與變革下,國產(chǎn)EDA如何破局?

評論